Overwrite this text with the Lit. Number

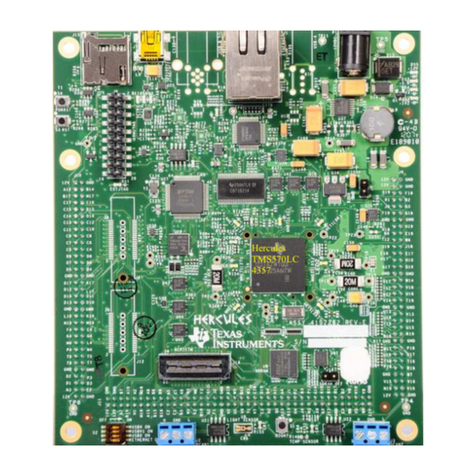

2Getting Started With TMS570LS Microcontrollers

Figures

Figure 1. Device Block Diagram........................................................................................................3

Figure 2. Flash Read Control Register: FRDCNTL, Address = 0xFFF87000...............................13

Figure 3. Flash Bank Fall-Back Control Register: FBFALLBACK, Address = 0xFFF87040 ......14

Figure 4. Flash Bank Access Control Register: FBAC, Address = 0xFFF8703C........................15

Figure 5. Flash Pump Access Control Register 1: FPAC1, Address = 0xFFF87048 ..................16

Figure 6. Flash Pump Access Control Register 2: FPAC2, Address = 0xFFF8704C..................16

Figure 7. FMzPLL Block Diagram ...................................................................................................17

Figure 8. PLL Control Register 1: PLLCTL1, Address = 0xFFFFFF70.........................................18

Figure 9. PLL Control Register 2: PLLCTL2, Address = 0xFFFFFF74.........................................19

Figure 10. FPLL Block Diagram ........................................................................................................20

Figure 11. PLL Control Register 3: PLLCTL3, Address = 0xFFFFE100.........................................21

Figure 12. Clock Source Disable Register: CSDIS, Address = 0xFFFFFF30 ................................23

Figure 13. Clock Source Disable Set Register: CSDISSET, Address = 0xFFFFFF34...................23

Figure 14. Clock Source Disable Clear Register: CSDISCLR, Address = 0xFFFFFF38...............24

Figure 15. GCLK, HCLK , VCLKx Source Register: GHVSRC, Address = 0xFFFFFF48...............26

Figure 16. Asynchronous Clock Source Register: VCLKASRC, Address = 0xFFFFFF4C ..........26

Figure 17. RTI Clock Source Register: RCLKSRC, Address = 0xFFFFFF50.................................27

Figure 18. Peripheral Clock Control Register: CLKCNTL, Address = 0xFFFFFFD0 ....................28

Figure 19. Memory Hardware Initialization Global Control Register: MINITGCR, Address =

0xFFFFFF5C......................................................................................................................32

Figure 20. Memory Self-Test / Initialization Control Register: MSIENA, Address = 0xFFFFFF6032

Figure 21. Memory Self-Test / Initialization Status Register: MSTCGSTAT, Address =

0xFFFFFF68......................................................................................................................33

Figure 22. VIM Interrupt Address Memory Map...............................................................................34

Figure 23. FIQ/IRQ Control Register 0: FIRQPR0, Address = 0xFFFFFE10 ..................................36

Figure 24. FIQ/IRQ Control Register 1: FIRQPR1, Address = 0xFFFFFE14 ..................................36

Figure 25. Interrupt Enable Set Register 0: REQENASET0, Address = 0xFFFFFE30 ..................37

Figure 26. Interrupt Enable Set Register 1: REQENASET1, Address = 0xFFFFFE34 ..................37

Figure 27. Interrupt Enable Clear Register 0: REQENACLR0, Address = 0xFFFFFE40...............37

Figure 28. Interrupt Enable Clear Register 1: REQENACLR1, Address = 0xFFFFFE44...............38

Tables

Table 1. Clock Sources on TMS570LS Microcontrollers.............................................................22

Table 2. Clock Domains on TMS570LS Microcontrollers............................................................25