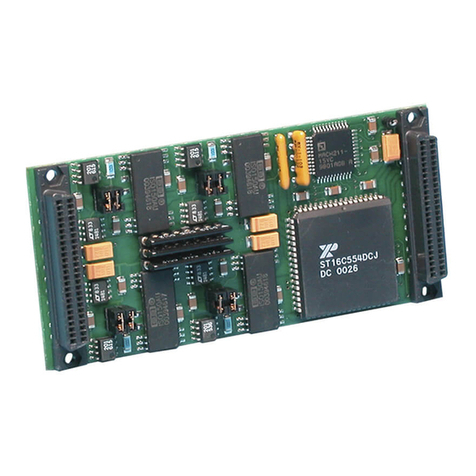

SERIES IP502 INDUSTRIAL I/O PACK QUAD EIA RS-485 SERIAL COMMUNICATION MODULE

___________________________________________________________________________________________

- 15 -

9. The host should begin writing data repeatedly to the Transmitter

Holding Register.

This loads the transmit FIFO and initiates transmission of serial

data on the TxD line. The first serial byte will take about 100us

to transmit, so it is likely that the transmit FIFO will fill before the

first byte has been sent.

10. Stop loading the transmit buffer, then write 00H to the Modem

Control Register (MCR).

This clears the Request-To-Send bit and releases the RTS*

signal line, disabling the transceiver for data output.

11. Read data repeatedly from the Receiver Buffer Register.

Provided data has been received.

After 14 bytes have been received (or fewer bytes with a

timeout), an interrupt will be generated if the host CPU has not

unloaded the receive FIFO.

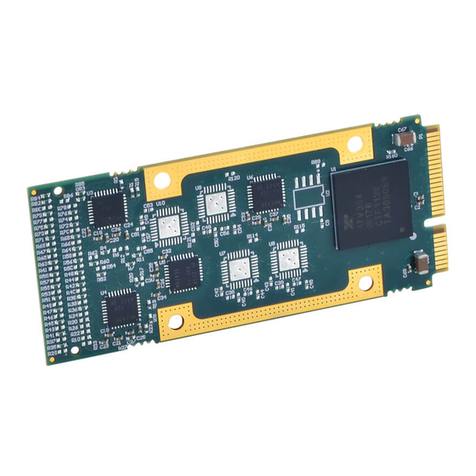

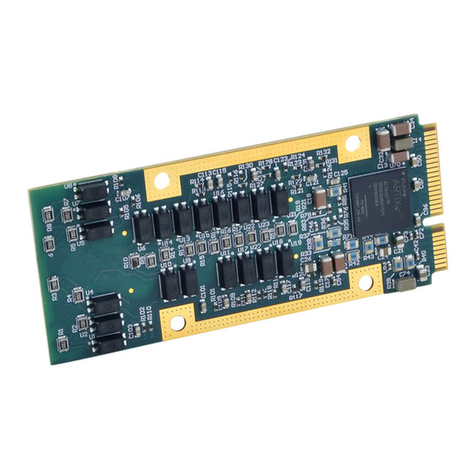

4.0 THEORY OF OPERATION

This section contains information regarding the EIA-485 serial

data interface. A description of the basic functionality of the circuitry

used on the board is also provided. Refer to the Block Diagram

shown in Drawing 4501-557 as you review this material.

EIA-RS485 SERIAL INTERFACE

The Electronic Industries Association (EIA) introduced EIA-

RS485 as a balanced (differential) serial data transmission interface

standard for the interchange of binary signals in multipoint

interconnection of digital equipments. Multiple generators and

receivers may be attached to a common interconnecting cable as

shown in Drawing 4501-558.

The EIA-RS485 interface specifies a balanced driver with

balanced receivers. Balanced data transmission refers to the fact

that two conductors are switched per signal and the logical state of

the data is referenced by the difference in potential between the two

conductors, not with respect to signal ground. The differential

method of data transmission makes EIA-RS485 ideal for noisy

environments since it minimizes the effects of coupled noise and

ground potential differences. That is, since these effects are seen

as common-mode voltages (common to both lines), not differential,

they are rejected by the receivers. Additionally, balanced drivers

have generally faster transition times and allow operation at higher

datarates over longer distances.

The EIA-RS485 standard defines a bi-directional, terminated,

multiple driver and multiple receiver configuration. Half-duplex

operation is provided by the sharing of a single data path for transmit

and receive. The maximum data transmission cable length is

generally limited to 4000 feet without a signal repeater installed.

EIA-RS485 is electrically similar to EIA/TIA-422B, except that

EIA/TIA-422B supports full-duplexed single driver multiple receiver

operation (see Acromag Model IP501).

With respect to EIA-485, logic states are represented by

differential voltages from 1.5 to 5V. The polarity of the differential

voltage determines the logical state. A logic is represented by a

negative differential voltage between the terminals (measured A to B,

or + to -). A logic 1 is represented by a positive differential voltage

between the terminals (measured A to B, or + to -). The line

receivers convert these signals to the conventional TTL level.

Start and stop bits are used to synchronize the receiver to the

asynchronous serial data of the transmitter. The transmit data line is

normally held in the mark state (logical 1). The transmission of a

data byte requires that a start bit (a logical 0 or a transition from

mark to space) be sent first. This tells the receiver that the next bit

is a data bit. The data bits are followed by a stop bit (a logical 1 or a

return to the mark state). The stop bit tells the receiver that a

complete byte has been received. Thus, 10 bits make up a data byte

if the data character is 8 bits long (and no parity is assumed). Nine

bits are required if only standard ASCII data is being transmitted (1

start bit + 7 data bits + 1 stop bit). The character size for this

module is programmable between 5 and 8 bits.

Parity is a method of judging the integrity of the data. Odd,

even, or no parity may be configured for this module. If parity is

selected, then the parity bit precedes transmission of the stop bit.

The parity bit is a 0 or 1 bit appended to the data to make the total

number of 1 bits in a byte even or odd. Parity is not normally used

with 8-bit data. Even parityspecifies that an even number of logical

1’s be transmitted. Thus, if the data byte has an odd number of 1’s,

then the parity bit is set to 1 to make the parity of the entire character

even. Likewise, if the transmitted data has an even number of 1’s,

then the parity bit is set to 0 tomaintain even parity. Odd parity

works the same way using an odd number of logical 1’s. Thus, both

the transmitter and receiver must have the same parity. If a byte is

received that has the wrong parity, an error is assumed and the

sending system is typically requested to retransmit the byte. Two

other parity formats not supported by this module are mark parity

and space parity. Mark parity specifies that the parity bit will always

be a logical 1, space parity requires the parity bit will always be 0.

The most common asynchronous serial data format is 1 start bit,

8 data bits, and 1 stop bit, with no parity. The following table

summarizes the available data formats:

START BIT Binary 0 (a shift from “Mark” to “Space”)

DATA BITS 5,6,7, or 8 Bits

PARITY Odd, Even, or None

STOP BIT Binary 1 (1, 1-1/2, or 2 Bit times)

With start, stop, and parity in mind, for an asynchronous data

byte, note that at least one bit will be a 1 (the stop bit). This defines

the break signal (all 0 bits with a 1 stop bit lasting longer than one

character). A break signal is a transfer from “mark” to “space” that

lasts longer than the time it takes to transfer one character.

Because the break signal doesn’t contain any logical 1’s, it cannot be

mistaken for data. Typically, whenever a break signal is detected,

the receiver will interpret whatever follows as a command rather than

data. The break signal is used whenever normal signal processing

must be interrupted. In the case of a modem, it will usuallyprecede

a modem control command. Do not confuse the break signal with

the ASCII Null character, since a break signal is longer than one

character time. That is, it is any “space” condition on the line that

lasts longer than a single character (including its framing bits) and is

usually 1-1/2 to 2 character times long.