6.2 Connector Information ...............................................................................................44

6.2.1 J3 CPU XDP Debug Connector ......................................................................................................... 44

6.2.2 J6 SPI BIOS Programming Header ................................................................................................... 44

6.2.3 J17 FPGA-based VME Bridge Programming Header ....................................................................... 44

6.2.4 VME Interface ................................................................................................................................. 45

6.2.4.1 P0 VME Connector (Optional)........................................................................................ 45

6.2.4.2 P1 VME Connector ......................................................................................................... 46

6.2.4.3 P2 VME Connector (Standard I/O)................................................................................. 47

6.2.4.4 P2 VME Connector (XVME-6300 Compatible I/O - Consult Factory for this Option)..... 48

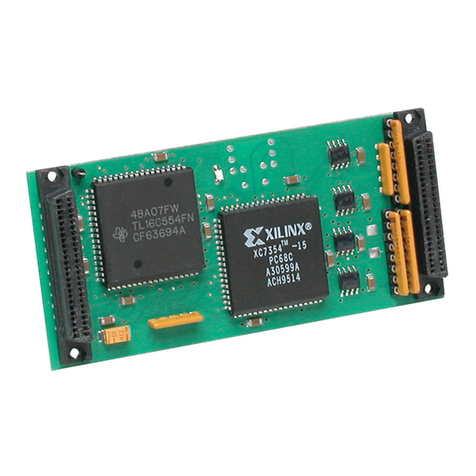

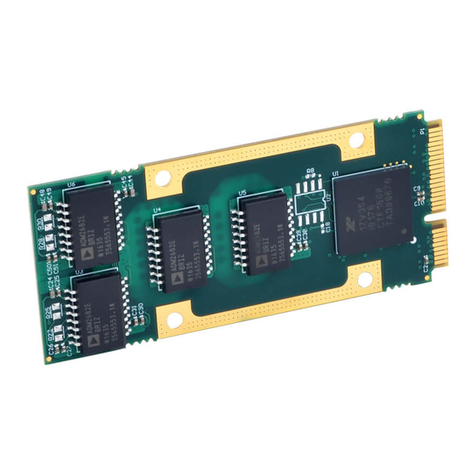

6.2.5 Lower PMC/XMC Site ...................................................................................................................... 49

6.2.5.1 J11 Lower PMC Site PCI-X Connector ............................................................................ 49

6.2.5.2 J12 Lower PMC Site PCI-X Connector ............................................................................ 50

6.2.5.3 J13 Lower PMC Site PCI-X Connector ............................................................................ 51

6.2.5.4 J14 Lower PMC Site Rear-I/O Connector ....................................................................... 52

6.2.5.5 J15 Lower XMC Site PCIe Connector.............................................................................. 53

6.2.5.6 J8 Lower PMC/XMC Site JTAG Connector...................................................................... 53

6.2.5.7 J16 Lower XMC Site Rear I/O Connector ....................................................................... 54

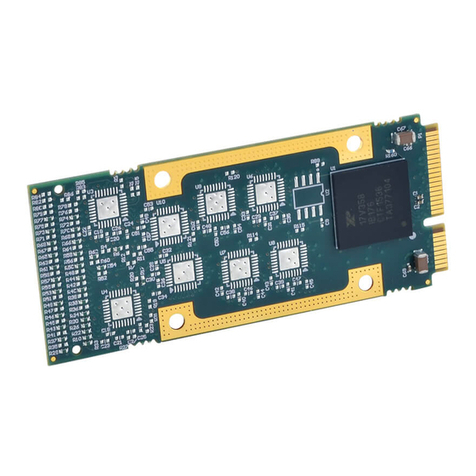

6.2.6 Upper PMC/XMC Site...................................................................................................................... 55

6.2.6.1 J21 Upper PMC Site PCI-X Connector ............................................................................ 55

6.2.6.2 J22 Upper PMC Site PCI-X Connector ............................................................................ 56

6.2.6.3 J23 Upper PMC Site PCI-X Connector ............................................................................ 57

6.2.6.4 J24 Upper PMC Site Rear I/O Connector ....................................................................... 58

6.2.6.5 J25 Upper XMC Site PCIe Connector.............................................................................. 59

6.2.6.6 J9 Upper PMC/XMC Site JTAG Connector...................................................................... 59

6.2.6.7 J7 Upper PMC/XMC Site Expansion Connector ............................................................. 60

6.2.7 Front Panel Connectors................................................................................................................... 61

6.2.7.1 J5 COM/USB/VGA Connector ........................................................................................ 61

6.2.7.2 J4 Dual Ethernet RJ Point 5 Connector .......................................................................... 62

6.2.8 P3 CPU Fan Connector .................................................................................................................... 62

6.3 P2 I/O Signal Requirements ........................................................................................63

6.3.1 VGA ................................................................................................................................................. 63

6.3.2 ESD .................................................................................................................................................. 63

It is strongly suggested that ESD protection be included in interface circuitry on the VGA and USB ports.

Failure to do so may cause damage the XVME-6500 in the event of an ESD discharge into the I/O pins. 63

6.4 Power Requirements ..................................................................................................64

6.5 Environmental Considerations ....................................................................................65

6.6 Reliability Prediction..................................................................................................66

6.7 XVME-6500 Certificate of Volatility.............................................................................67

7.0 XBRD-9060 I/O EXPANDER ACCESSORY MODULE.......................................... 68