[AKD4344-A]

<KM087902> 2007/07

- 4 -

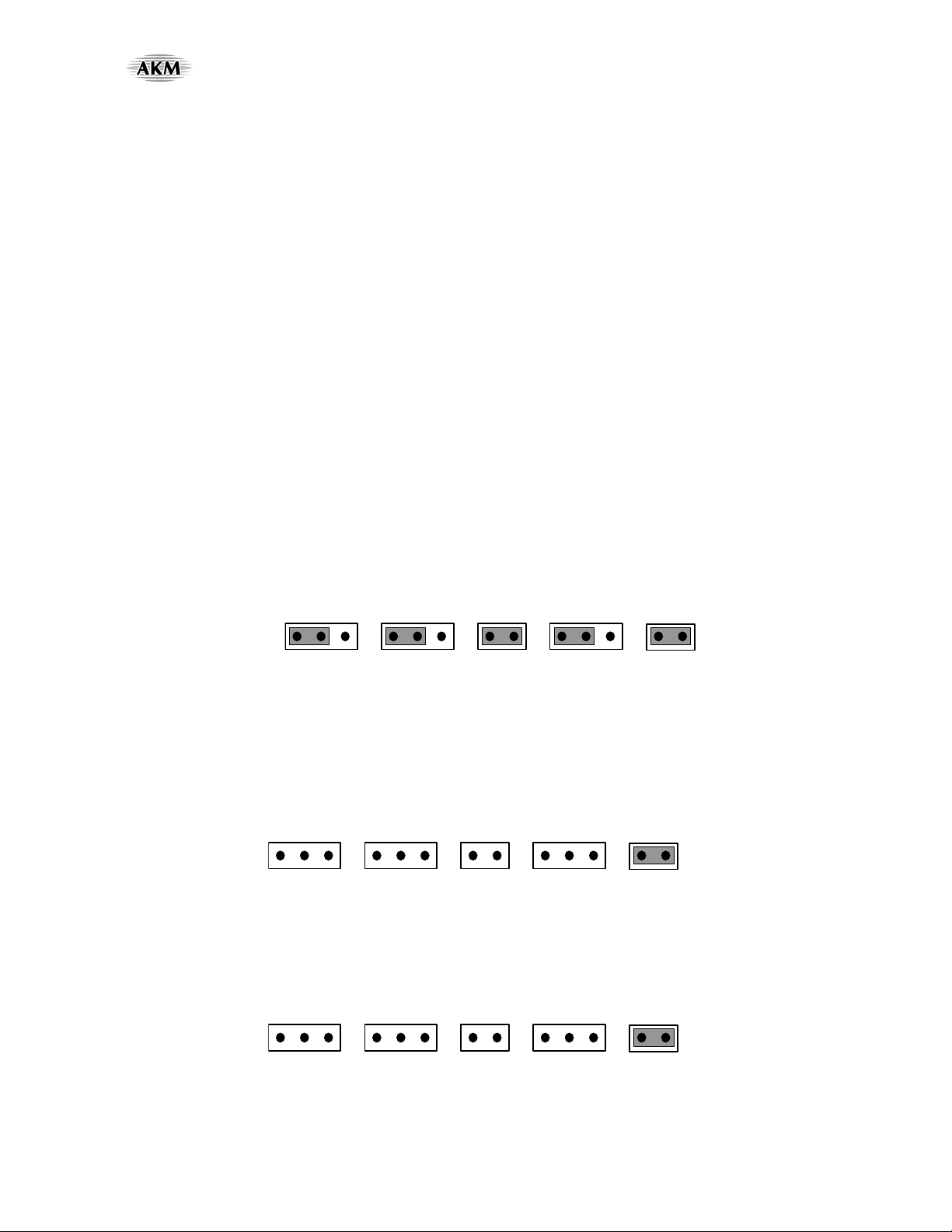

Example for External Clock setting

Refer to the following setting when MCLK, BICK and LRCK are supplied to the AK4344 from J1 (EXT).

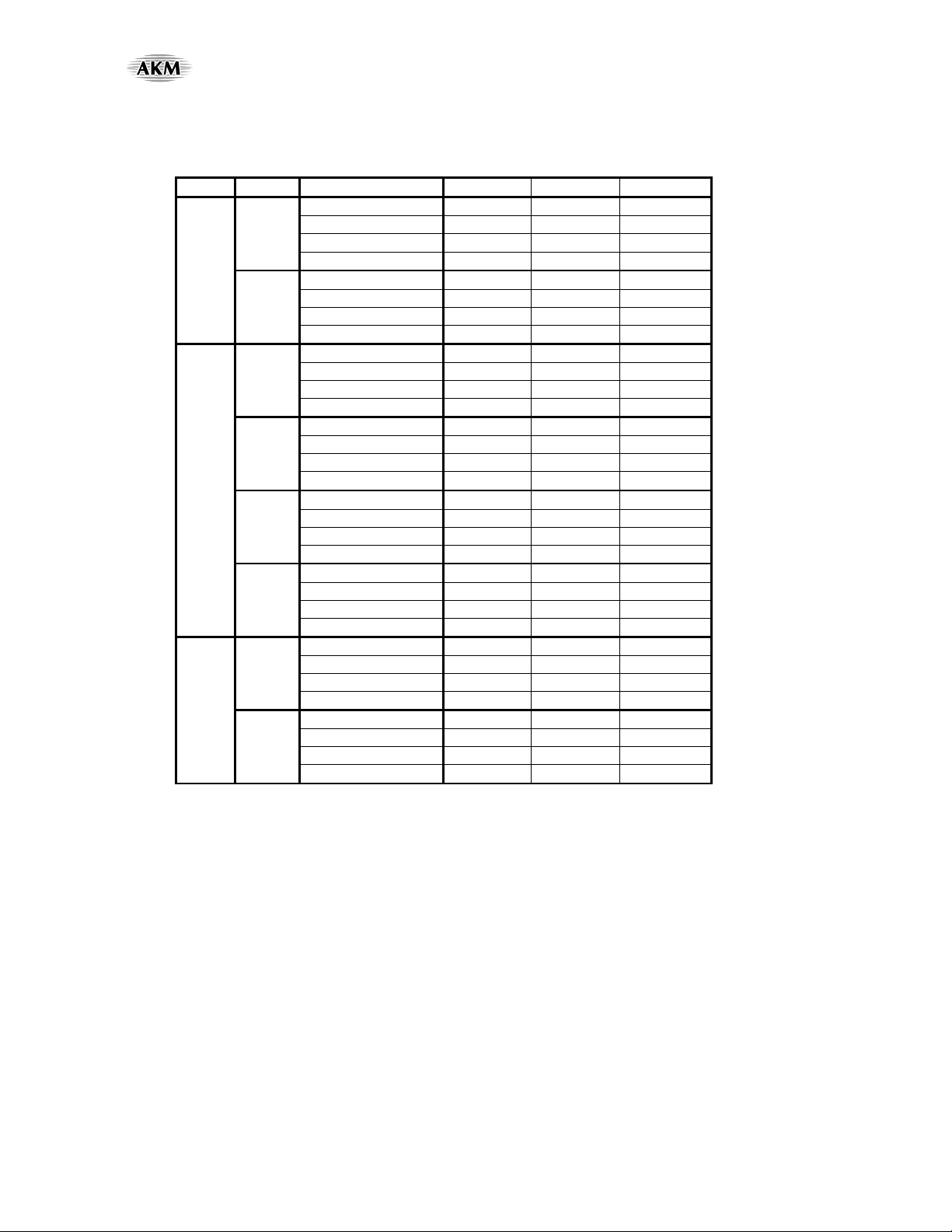

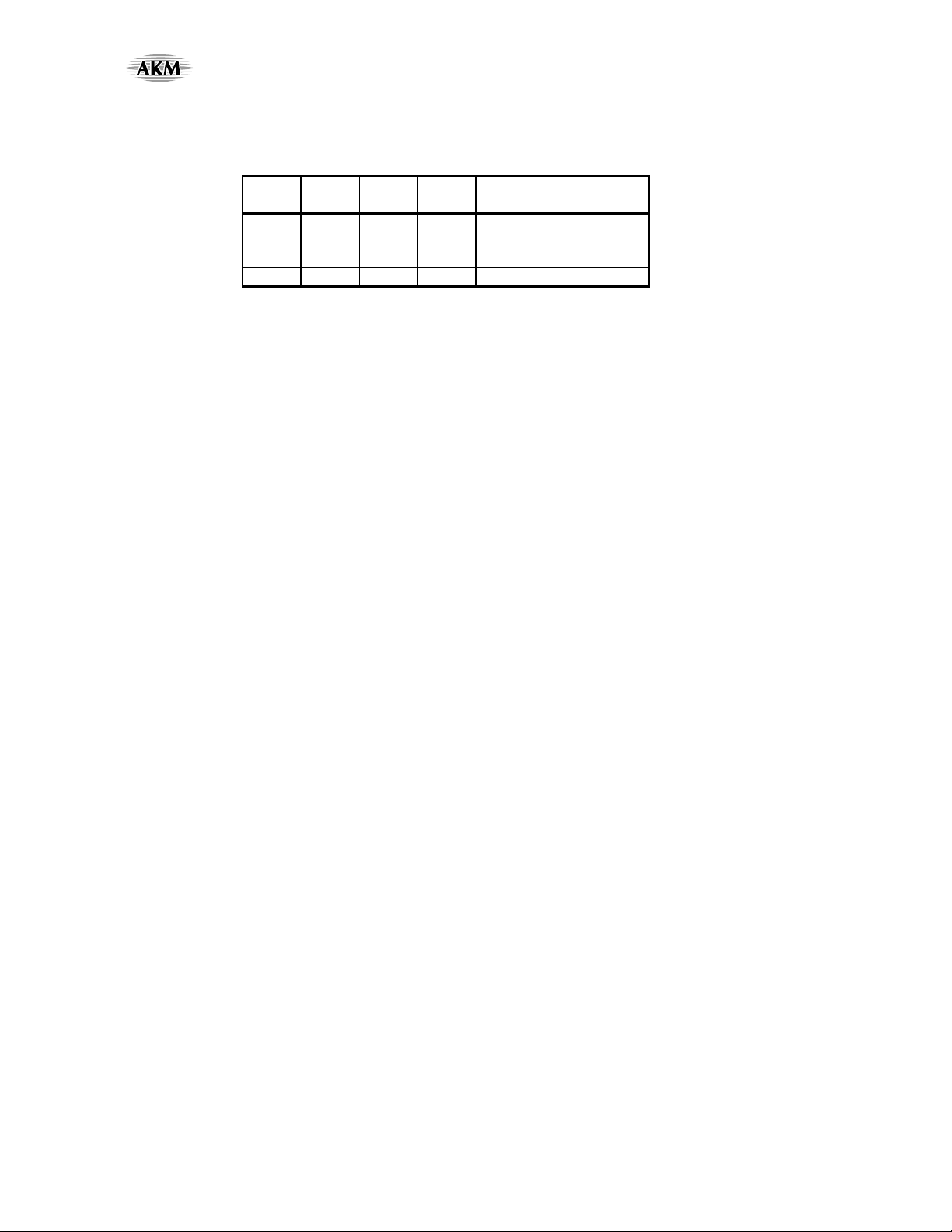

Mode fs MCLK JP11 (DIV) JP9 (CLK) JP13 (LRFS)

512fs = 4.096MHz x2 x2 x1

768fs = 6.144MHz x3 x2 x1

1024fs = 8.192MHz x2 x2 x2

8kHz

1536fs = 12.288MHz x3 x2 x2

512fs = 12.288MHz x2 x2 x1

768fs = 18.432MHz x3 x2 x1

1024fs = 24.576MHz x2 x2 x2

Half

24kHz

1536fs = 36.864MHz x3 x2 x2

256fs = 2.048MHz x1 x2 x1

384fs = 3.072MHz OPEN x3 x1

512fs = 4.096MHz x2 x2 x1

8kHz

768fs = 6.144MHz x3 x2 x1

256fs = 8.192MHz x1 x2 x1

384fs = 12.288MHz OPEN x3 x1

512fs = 16.384MHz x2 x2 x1

32kHz

768fs = 24.576MHz x3 x2 x1

256fs = 11.2896MHz x1 x2 x1 Default

384fs = 16.9344MHz OPEN x3 x1

512fs = 22.5792MHz x2 x2 x1

44.1kHz

768fs = 33.8688MHz x3 x2 x1

256fs = 12.288MHz x1 x2 x1

384fs = 18.432MHz OPEN x3 x1

512fs = 24.576MHz x2 x2 x1

Normal

48kHz

768fs = 36.864MHz x3 x2 x1

128fs = 6.144MHz OPEN x1 x1

192fs = 9.216MHz OPEN x3 x3

256fs = 12.288MHz x1 x2 x1

48kHz

384fs = 18.432MHz OPEN x3 x1

128fs = 12.288MHz OPEN x1 x1

192fs = 18.432MHz OPEN x3 x3

256fs = 24.576MHz x1 x2 x1

Double

96kHz

384fs = 36.864MHz OPEN x3 x1

Table 1. Clock Setting