[AKD4686-B]

EVALUATION BOARD MANUAL

Operating sequence

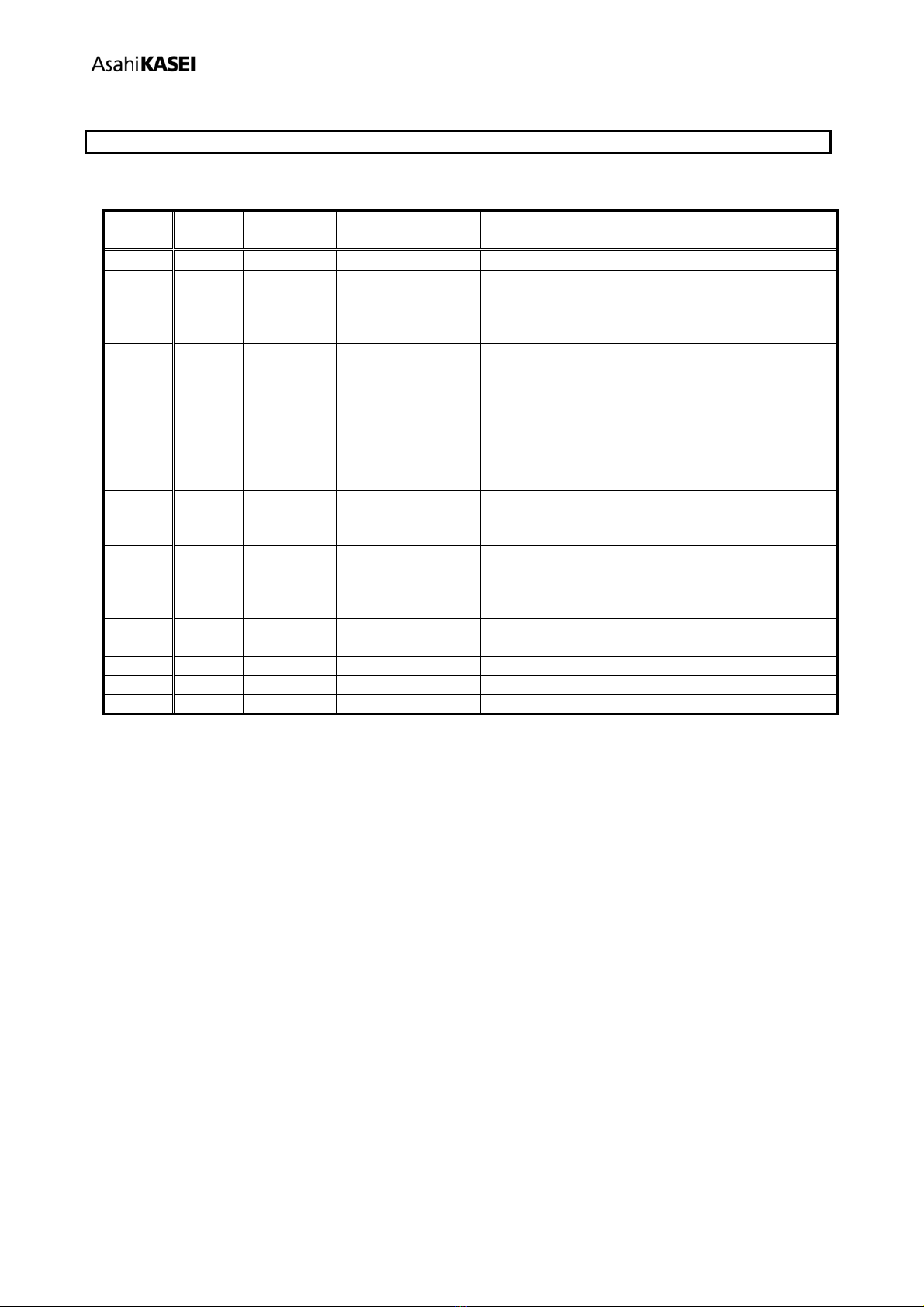

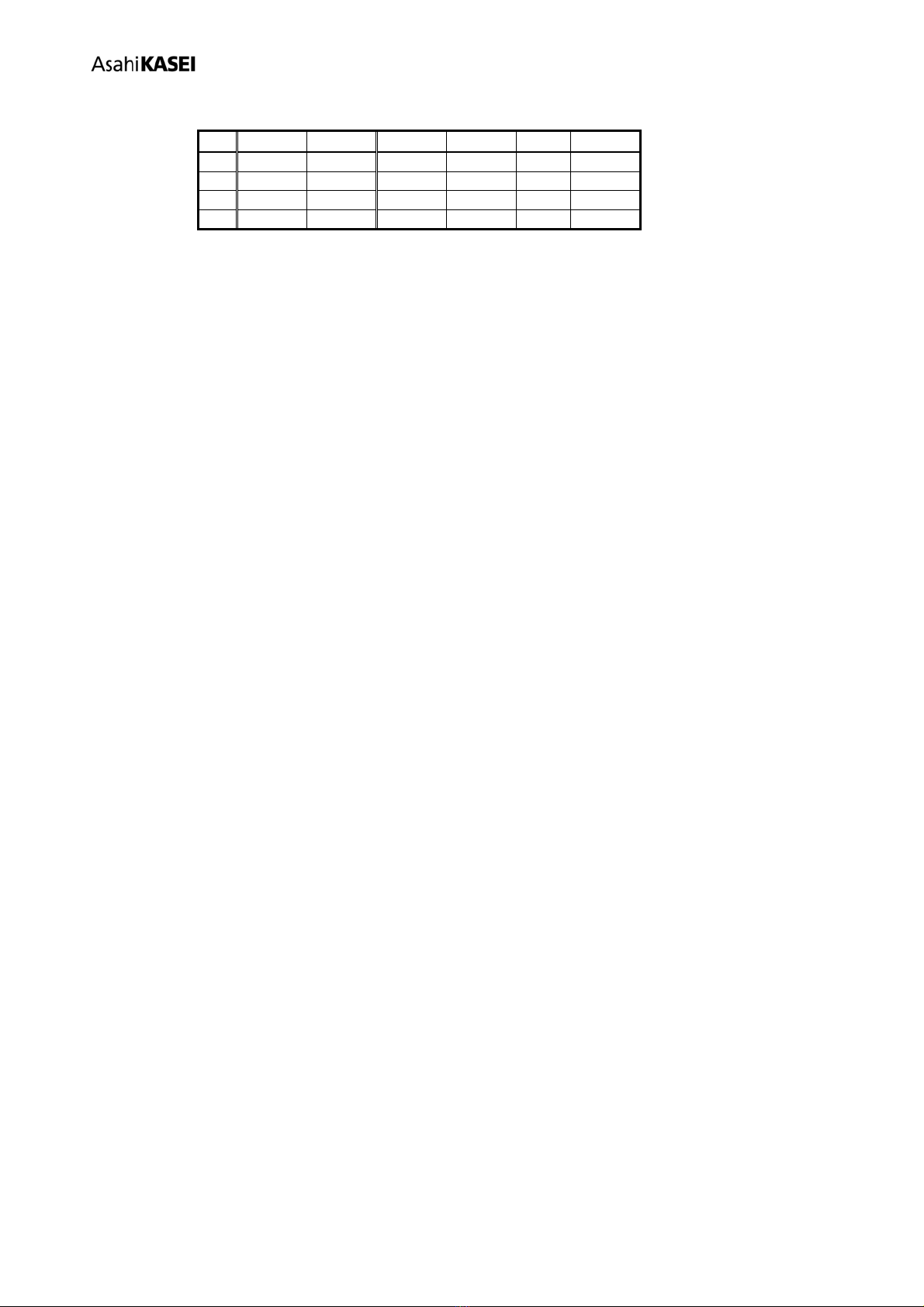

1. Set up power supply lines.

Name of

Jack

Color of

Jack Voltage Used for Comment and attention Default

+5V Red

+4.5∼+5.5V Regulator T2, T5 Should be always connected +5V

AVDD1 Orange +3.0∼+3.6V AVDD1 of AK4686

Should be open when JP40

(AVDD1_SEL) is set to REG side.

Should be connected when JP40

(AVDD1_SEL) is set to AVDD1 side.

Open

AVDD2 Orange +3.0∼+3.6V AVDD2 of AK4686

Should be open when JP41

(AVDD2_SEL) is set to REG side.

Should be connected when JP41

(AVDD2_SEL) is set to AVDD2 side.

Open

DVDD Orange

+3.0∼+3.6V DVDD of AK4686

Should be open when JP42 (DVDD_SEL)

is set to REG side.

Should be connected when JP42

(DVDD_SEL) is set to DVDD side.

Open

CVDD Orange

+3.0∼+3.6V CVDD of AK4686

Should be connected when default.

Should be open in case of using regulator

T2 when R85 is short and L7 is open.

+3.3V

D3.3V Orange

+3.0∼+3.6V Power supply of

logic

Should be open when JP45 (D3.3V_SEL)

is set to REG side.

Should be connected when JP45

(D3.3V_SEL) is set to D3.3V side.

Open

VSS1 Black 0V Analog Ground Should be always connected 0V

VSS2 Black 0V Analog Ground Should be always connected 0V

VSS3 Black 0V Analog Ground Should be always connected 0V

VSS4 Black 0V Analog Ground Should be always connected 0V

DGND Black 0V Digital Ground Should be always connected 0V

Table 1. Power supply lines

Each supply line should be distributed from the power supply unit.

2. Set up evaluation mode and jumper pins. (Refer to the following item.)

3. Connect cables. (Refer to the following item.)

4. Power on.

The AK4686 (U1) should be reset once bringing SW1 (PDN) “L” upon power-up.

Keep “H” during normal operaion.

5. Set up control software registers. (Refer to the following item.)

< KM103800> 2010/08

- 2 -