ARTIX-7 FPGA Development Board AX7202 User Manual

Table of Contents

Version Record .............................................................................................2

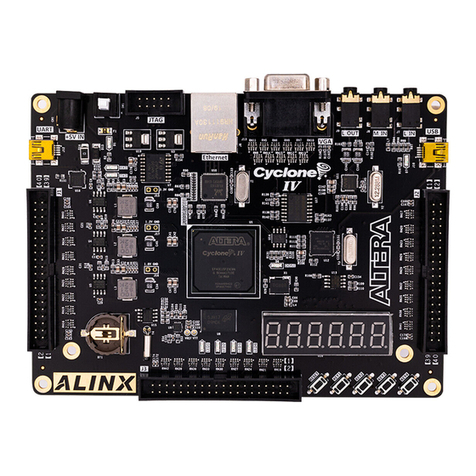

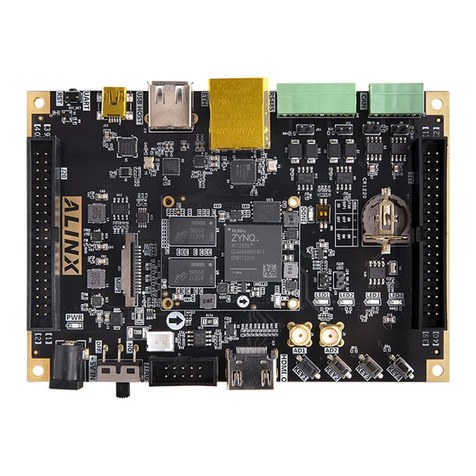

Part 1: FPGA Development Board Introduction .......................................... 6

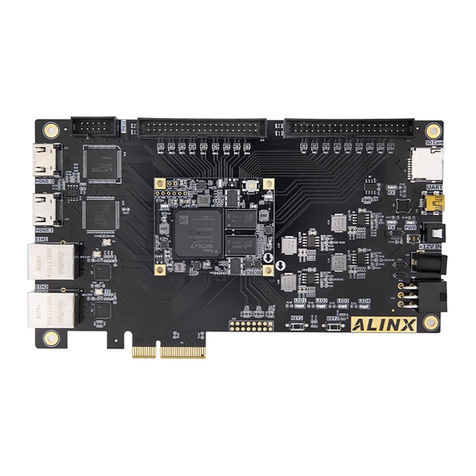

Part 2: AC7200 Core Board Introduction ...................................................10

Part 2.1: FPGA Chip ........................................................................... 12

Part 2.2: Active Differential Crystal .....................................................13

Part 2.3: 200Mhz Active Differential clock ..........................................14

Part 2.4: 148.5Mhz Active Differential Crystal ................................... 15

Part 2.5: DDR3 DRAM ........................................................................16

Part 2.6: QSPI Flash ...........................................................................21

Part 2.7: LED Light on Core Board .................................................... 23

Part 2.8: Reset Button ........................................................................ 24

Part 2.9: JTAG Interface .....................................................................25

Part 2.10: Power Interface on the Core Board .................................. 26

Part 2.11: Board to Board Connectors ............................................... 27

Part 2.12: Power Supply .....................................................................34

Part 2.13: Structure Diagram ..............................................................35

Part 3: Carrier Board ..................................................................................36

Part 3.1: Carrier Board Introduction ................................................... 36

Part 3.2: Gigabit Ethernet Interface ................................................... 37

Part 3.3: SFP Interface ....................................................................... 39

Part 3.4: VGA display interface .......................................................... 42

Part 3.5: USB2.0 Interface ................................................................. 44

Part 3.6: SD Card Slot ........................................................................46

Part 3.7: USB to Serial Port ................................................................48

Part 3.8: RS232 Interface ...................................................................50

Part 3.9: EEPROM 24LC04 ................................................................51

Part 3.10: Real time clock DS1302 .................................................... 52