Getting Started with AT32F421

2022.10.21 4 Ver 2.0.4

List of Figures

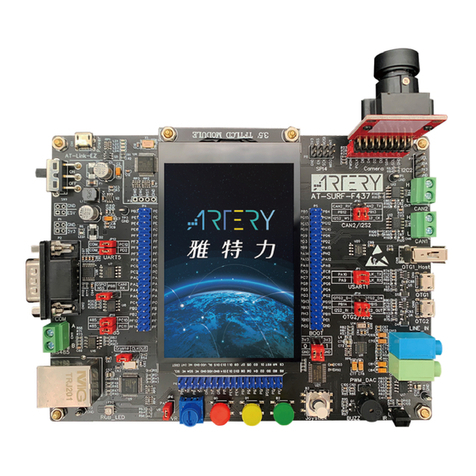

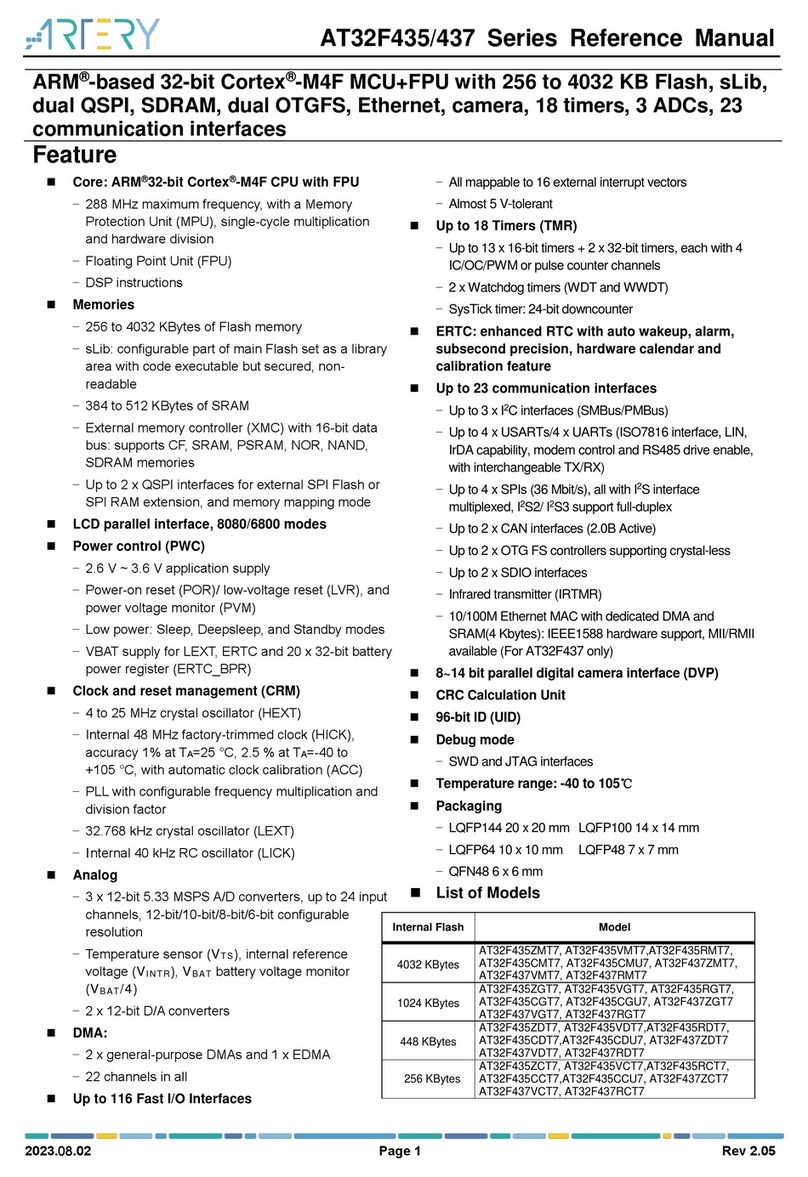

Figure 1. AT-START-F421 evaluation board with AT-Link-EZ............................................................5

Figure 2.AT-START-F421 evaluation board package.........................................................................5

Figure 3. ICP/ISP/AT-Link-Family........................................................................................................6

Figure 4. BSP package........................................................................................................................6

Figure 5. Keil_v5 templates.................................................................................................................7

Figure 6. Pack download.....................................................................................................................8

Figure 7. Set upArteryTek.AT32F421 _DFP.......................................................................................8

Figure 8. Set up Keil4_AT32MCU_AddOn..........................................................................................8

Figure 9. Pack Installer icon in Keil .....................................................................................................9

Figure 10. Set up IAR_AT32MCU_AddOn..........................................................................................9

Figure 11. Keil Debug option .............................................................................................................10

Figure 12. Keil Debug Settings..........................................................................................................10

Figure 13. Keil Utilities.......................................................................................................................10

Figure 14. IAR Debug option............................................................................................................. 11

Figure 15. IAR CMSIS-DAP option....................................................................................................11

Figure 16. Wait states of Flash performance select register (FLASH_PSR)....................................12

Figure 17. System clock configuration function “system_clock_config”............................................12

Figure 18.AT32F421 118 MHz PLL clock configuration ...................................................................13

Figure 19. SXX PLL auto step-by-step switch configurations...........................................................14

Figure 20. AT32 PLL auto step-by-step switch configurations..........................................................14

Figure 21. Enable/disable access protection in ICP Programmer ....................................................15

Figure 22. Enable access protection in ISP Programmer.................................................................16

Figure 23. Disable access protection in ISP Programmer ................................................................16

Figure 24. Enable erase and program protection in ICP Programmer..............................................17

Figure 25. Disable erase and program protection in ICP Programmer.............................................18

Figure 26. Set AP mode in ICP Programmer.....................................................................................19

Figure 27.AP mode enabling in ICP Programmer............................................................................19

Figure 28. Offline config settings in ICP Programmer.......................................................................20

Figure 29.AT-Link project file settings...............................................................................................21

Figure 30.AT-Link offline download status........................................................................................21

Figure 31. Read Cortex ID.................................................................................................................22

Figure 32. Read PID and UID............................................................................................................22

Figure 33. Flash Download failed–“Cortex- M4” pops up in downloading ........................................23