Benchmark DAC1 USB User manual

Benchmark

DAC1 USB

Instruction Manual

2-Channel 24-bit 192-kHz

Audio Digital-to-Analog Converter

DAC1 USB

Instruction Manual Revision D Page 2

Safety Information

Voltage Selection

CAUTION: THE FUSE DRAWER INCLUDES

A VOLTAGE SELECTION SWITCH WITH

TWO SETTINGS: ‘110’ AND ‘220’. CHECK

TO SEE THAT IT IS PROPERLY

CONFIGURED FOR YOUR LOCATION

BEFORE CONNECTING AC POWER.

Incorrect configuration may blow fuses or

cause erratic operation.

Repairs

CAUTION: DO NOT SERVICE OR REPAIR

THIS PRODUCT UNLESS PROPERLY

QUALIFIED. ONLY A QUALIFIED

TECHNICIAN SHOULD PERFORM

REPAIRS.

Fuses

CAUTION: FOR CONTINUED FIRE

HAZARD PROTECTION ALWAYS REPLACE

THE FUSES WITH THE CORRECT SIZE

AND TYPE (0.5A 250 V SLO-BLO® 5 X 20

MM – LITTELFUSE® HXP218.500 OR

EQUIVALENT).

Modifications

CAUTION: DO NOT SUBSTITUTE PARTS

OR MAKE ANY MODIFICATIONS

WITHOUT THE WRITTEN APPROVAL OF

BENCHMARK MEDIA SYSTEMS, INC.

MODIFICATION MAY CREATE SAFETY

HAZARDS AND VOID THE WARRANTY.

NOTICE: CHANGES OR MODIFICATIONS

NOT EXPRESSLY APPROVED BY

BENCHMARK MEDIA SYSTEMS COULD

VOID THE USER'S AUTHORITY TO

OPERATE THE EQUIPMENT UNDER FCC

REGULATIONS.

DAC1 USB

Instruction Manual Revision D Page 3

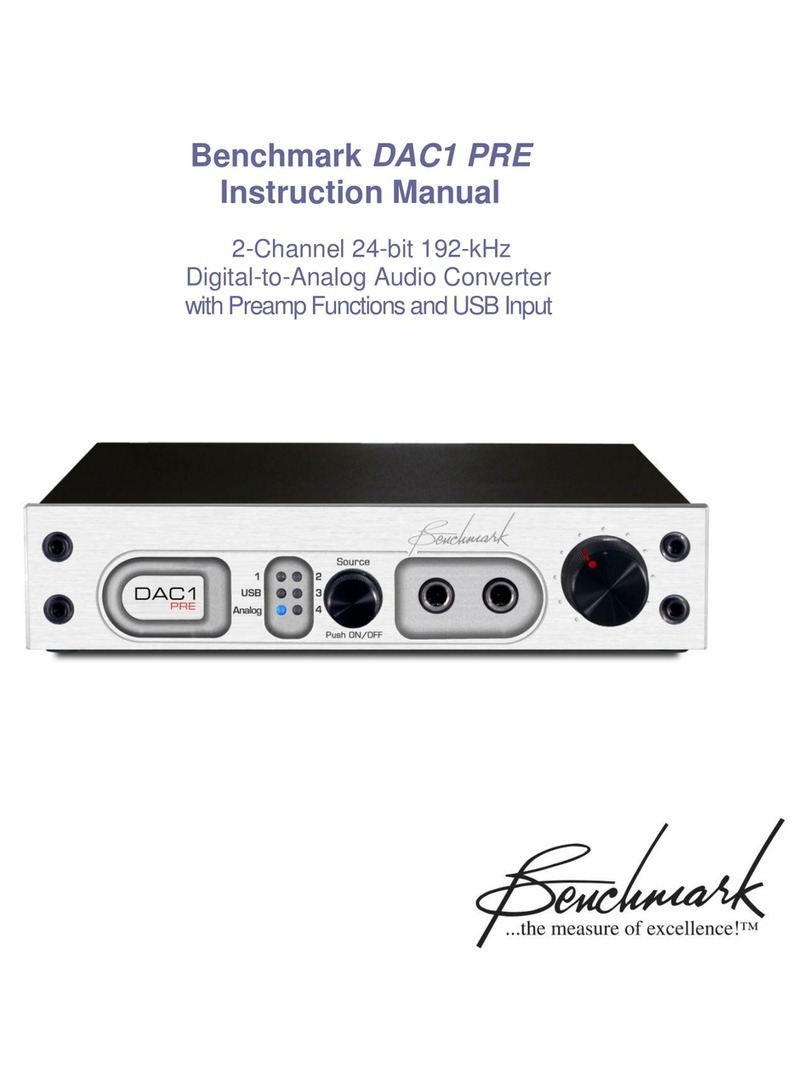

Faceplate Options

The DAC1 USB is available with 3 different faceplates. The internal electronics are identical in all

versions.

Black

Silver

Black Rack-Mount

DAC1 USB

Instruction Manual Revision D Page 4

Contents

Safety Information 2

Voltage Selection 2

Repairs 2

Fuses 2

Modifications 2

Faceplate Options 3

Contents 4

Features 5

Overview 6

DAC1 Heritage 6

Applications 6

Digital Inputs 6

Advanced USB Audio Technology 6

Jitter-Immune UltraLock™ 7

HPA2™ Headphone Amplifier 7

Mute Function 7

Volume Control 7

Direct Interfacing to Power Amplifiers 7

High-Current Output Drivers 7

‘Audio-Always’ Design Philosophy 7

Error Display 8

Automatic Standby/Resume 8

Low-Noise Internal Power Supply 8

Phase-Accurate Multi-Track and 5.1 8

Automatic Digital De-Emphasis 8

Front Panel 9

Input Status Display 9

Input Selector Switch 9

Input Indication 9

Error Indication 9

Standby Mode 10

HPA2TM Stereo Headphone Jacks 10

Volume Control 10

Rear Panel 11

Input 1 - SPDIF/AES BNC 11

Input 2 – AES/EBU XLR 12

Input 3 – Optical 12

Input 4 – USB 12

Output Level Switch 13

Balanced XLR Analog Line Outputs 13

Unbalanced RCA Analog Outputs 14

Low-Impedance Passive Pads 14

Calibration Trimmers 15

AC Power-Entry Module 15

Fuse Holder 15

Rack Mounting 16

Rack Mount Coupler 16

Blank Rack Panel 16

Benchmark Technologies 17

HPA2™ Headphone Amplifier 17

UltraLock™ Clock System 18

Advanced USB Audio Technology 21

Performance Graphs 24

Frequency Response Tests 24

FFT Analysis of Idle Channel Noise 26

Multi-Unit Phase Response 27

THD+N Tests 28

Jitter Tests 33

Input Sensitivity Tests 36

Volume Control Curve 39

Specifications 40

Audio Performance 40

Group Delay (Latency) 41

Digital Audio Inputs 42

Balanced Analog Outputs 43

Unbalanced Analog Outputs 43

HPA2TM Headphone Outputs 44

Status Display 44

AC Power Requirements 44

Dimensions 45

Weight 45

Regulatory Compliance 46

FCC Notice (U.S. Only) 46

RoHS Compliant Information 46

CE Certificate of Compliance 47

Warranty Information 48

Benchmark 1 Year Warranty 48

Benchmark Extended Warranty 49

Internal Settings 50

Removing Top Cover 50

Jumpers 50

DAC1 USB

Instruction Manual Revision D Page 5

Features

yUSB, XLR balanced, BNC coaxial, and TOSLINK optical digital inputs

yCompatible with Windows Vista/XP/2000 and Mac OS X without driver installation

yJumper-selected low-impedance 10, 20, or 30 dB pads on balanced outputs

y-10 dBV unbalanced RCA analog outputs, +13.5 dBu maximum output level

yTwo HPA2™ high-current, “0-Ohm”, high-output ¼” headphone outputs

yHPA2™ gain jumpers to match gain to headphone sensitivity

yFront-panel volume control for headphone outputs

yFront-panel volume control of all analog outputs (in Variable mode)

yRear-panel Variable/Calibrated mode switch enables volume control of analog outputs

yRear-panel Variable/Calibrated mode switch includes a center mute position

yIn Calibrated mode, levels are set by 10-turn trimmers (20 dB Range, 2 dB/turn)

yXLR outputs are preset to +4dBu at 0 dBFS in Calibrated mode (20-dB Pad enabled)

yRCA outputs are preset to +2 Vrms (8.2 dBu) at 0 dBFS in Calibrated mode

yHeadphone jack 1 mutes XLR and RCA outputs (feature may be disabled)

yBenchmark’s phase-accurate UltraLock™ technology for total jitter immunity

yStatus LED’s - display input selection and error conditions

yAutomatic Standby Mode – activated after 15 seconds of loss of digital input signal

yInstant wake-up from Standby Mode - no loss of audio

yTHD+N = -107 dB, 0.00045% @ -3 dBFS input, -105 dB, 0.00056% @ 0 dBFS input

yAutomatic de-emphasis in response to consumer pre-emphasis bit (44.1, 48, 88.2, and 96 kHz)

yReliable and consistent performance under adverse operating conditions

y115 V, 230 V, 50-60 Hz international power supply with very wide operating range

yLow radiation toroidal power transformer significantly reduces hum and line related interference

yLow power consumption (8 Watts typical program, 16 Watts peak)

yMeets FCC Class B and CE emissions requirements

DAC1 USB

Instruction Manual Revision D Page 6

Overview

The DAC1 USB is a reference-quality, 2-

channel 192-kHz 24-bit digital-to-analog

audio converter featuring Benchmark’s

Advanced USB Audio technology,

UltraLock™ clock system, and HPA2™

headphone amplifier.

DAC1 Heritage

The pristine audio path of the award-winning

DAC1 has made it the Benchmark of stand-

alone D/A converters. The DAC1 USB

preserves the exact topology of this audio

path while adding some of the most

frequently requested features.

The DAC1 USB includes a very unique USB

input with bit-transparent native 96/24

capability, a programmable mute function,

programmable headphone gain range, an

automatic standby/resume feature, and a

high-current output stage designed to drive

long cables or low-impedance loads, such as

high-end power-amplifiers.

The DAC1 USB looks, sounds, and measures

the same as the DAC1. We have added

convenience and flexibility without altering

the performance.

Applications

The DAC1 USB is designed for maximum

transparency and is well suited for critical

playback in studio control rooms, mastering

rooms, and high-end audiophile applications.

Benchmark’s Advanced USB Audio interface

makes the DAC1 USB an ideal primary

output device for digital audio workstations,

desktop audio editing applications, computer-

based media playback, home media servers,

and computer-based radio broadcast systems.

The rugged and compact rack-mount option

makes the DAC1 USB an excellent choice for

location recording, broadcast facilities, and

mobile trucks.

Digital Inputs

There are four digital input connectors

(coaxial, balanced XLR, optical, and USB).

The coaxial, XLR, and optical digital inputs all

accept professional (AES) and consumer

(SPDIF) data formats at sample rates up to

192 kHz.

Advanced USB Audio Technology

The USB input is compatible with Windows

Vista/XP/2000 and Mac OS X, and does not

require driver installation or system

configuration.

Unlike all previous driverless USB audio

interfaces, Benchmark’s Advanced USB

Audio technology supports sample rates up

to 96 kHz and word lengths up to 24-bits.

The DAC1 USB is a true plug-and-play

solution, and is designed to begin playback

immediately after the unit is connected to a

USB port for the first time.

DAC1 USB

Instruction Manual Revision D Page 7

Jitter-Immune UltraLock™

The Benchmark UltraLock™ system is nearly

100% jitter-immune. The D/A conversion

clock is isolated from the input digital audio

clock in a topology that outperforms two-

stage PLL designs. In fact, no jitter-induced

artifacts can be detected using an Audio

Precision System 2 Cascade test set.

Measurement limits include detection of

artifacts as low as -140 dBFS, application of

jitter amplitudes as high as 12.75 unit

intervals (UI) and application of jitter over a

frequency range of 2 Hz to 200 kHz.

Any signal that can be decoded by the USB or

AES/EBU receivers will be reproduced without

the addition of any measurable jitter artifacts.

The AES/EBU receiver IC has been selected

for its ability to accurately recover data in the

presence of very high jitter levels.

HPA2™ Headphone Amplifier

Two ¼” headphone jacks are driven by the

HPA2™ - Benchmark’s signature high-

current, 0-Ohm headphone amplifier. The

HPA2™ is capable of delivering the full

performance of the DAC1 USB into the

difficult loading presented by headphones.

The HPA2™ maintains less than 0.0003%

THD+N under full load.

Mute Function

The left-hand headphone jack includes a

switch that mutes the XLR and RCA analog

outputs when a headphone plug is inserted.

This mute feature can be disabled with

internal jumpers.

Volume Control

The front-panel Volume Control sets the

output level of the headphone jacks. It can

also be used to control the output level of the

balanced XLR and unbalanced RCA analog

outputs. A rear-panel switch selects

Variable or Calibrated output levels. In

Variable mode the analog outputs are

controlled by the Volume Control.

Direct Interfacing to Power

Amplifiers

The DAC1 USB is designed to interface

directly to power amps and powered studio

monitors in order to provide the cleanest and

shortest path from the digital source to the

monitor output. This often results in a

substantial improvement in sound quality.

10, 20, and 30 dB pads are provided for

interfacing directly to monitors and amplifiers

that often have too much input sensitivity to

handle high-level (+29 dBu) signal levels.

High-Current Output Drivers

The DAC1 USB features new high-current

output drivers that are capable of driving

300-Ohm loads without an increase in

distortion. They are also well suited for

driving long cables or high-capacitance loads.

‘Audio-Always’ Design

Philosophy

The DAC1 USB is designed to perform

gracefully in the presence of errors and

interruptions at the digital audio inputs. A

soft mute circuit eliminates pops when a

digital signal is applied. Power management

circuitry controls the muting and resetting of

all digital circuits upon removal and

application of power. Audio is present at the

outputs only 60 ms after applying a digital

input signal and only 500 ms after applying

power to the unit.

The DAC1 USB is designed to avoid all

unnecessary mute scenarios. Muting is only

enabled upon loss of power, or when digital

transmission errors occur. The DAC1 USB

does not mute when the input data is all

zeros. Consequently, no audio is lost when

an audio transient follows full silence.

Furthermore, the DAC1 USB signal-to-noise

specifications represent the true system

performance, not just the performance of an

output mute circuit.

The DAC1 USB will operate even when

sample rate status bits are set incorrectly.

DAC1 USB

Instruction Manual Revision D Page 8

Sample rate is determined by measuring the

incoming signal. Lack of sample rate status

bits or incorrectly set status bits will not

cause loss of audio.

Error Display

When the selected digital input signal is

disconnected, incompatible, or drops out, the

Input Status Display will flash indicating a

signal error. This flashing will stop when the

error is corrected. If the error persists for

more than 15 seconds, the DAC1 USB will

enter Standby Mode.

Automatic Standby/Resume

The DAC1 USB features an automatic

standby mode that eliminates the need to

turn the converter on and off. Standby

Mode starts 15 seconds after a digital source

device is turned off, disconnected, or contains

errors that prevent D/A conversion. All LED’s

are off while in standby mode.

While in Standby Mode, the DAC1 USB

continues to monitor the selected digital input

and will immediately resume normal

operation when an error-free signal is

restored.

Low-Noise Internal Power

Supply

The internal power supply supports all

international voltages and has generous

margins for over and under voltage

conditions. It has excellent immunity to noise

on the AC line and no external AC filtering is

required.

Phase-Accurate Multi-Track and

5.1

The DAC1 is phase-accurate between

channels at all sample rates, and is phase

accurate between any combination of DAC1

and DAC1 USB converters at sample rates up

to 96 kHz. Phase-accurate multi-track and

5.1 surround systems are easily constructed

using multiple DAC1 and/or DAC1 USB

converters.

Automatic Digital De-Emphasis

Pre-emphasis was used on many early CD

recordings. It is rarely used on newer

recordings and consequently some D/A

converters omit de-emphasis. The DAC1

USB will correctly apply precise digital de-

emphasis when and if it is needed. The de-

emphasis circuit supports 44.1, 48, 88.2 and

96-kHz sample rates and is automatically

enabled in response to the pre-emphasis

status bits in consumer format digital signals.

DAC1 USB

Instruction Manual Revision D Page 9

Front Panel

Input Status Display

The DAC1 USB has three LED’s on the front

panel that indicate which digital input is

selected. These LED’s flash when an error

condition occurs. All LED’s turn off when the

DAC1 USB is in Standby Mode.

Input Selector Switch

The input selector toggle switch is located

directly to the right of the Input Status

Display.

The switch is a momentary 3-position switch

that scrolls up and down through the 4 digital

inputs in a round-robin format.

If the DAC1 USB is in Standby Mode it will

resume normal operation when the Input

Selector Switch is toggled.

Input Indication

The numbers to the left of the LED’s

correspond to the following inputs:

1. Coaxial (bottom LED)

2. XLR (middle LED)

3. Optical (top LED)

4. USB (top and bottom LED’s)

When the top and bottom LED’s are lit

simultaneously, the USB (Input 4) is selected.

Error Indication

The Input Status Display will flash when an

error occurs on the selected digital input. The

number of times the display flashes before

entering standby indicates the type of error.

If the error is not resolved within about 15

seconds, the DAC1 USB will enter Standby

Mode. The DAC1 USB will resume normal

operation when it detects a valid input signal

at the last chosen input.

Error Codes:

•No signal – 16 slow flashes – audio

muted

•Data transmission errors - 16 flashes –

audio muted

•Non-PCM – 16 flashes – audio muted

•Non-audio – 32 rapid flashes – audio

muted

•Invalid sample (v-bit) – 64 very rapid

flashes – no mute

Common causes of errors are:

•Disconnected cable

•Data drop-outs due to a bad cable

•Incompatible audio data type (AC3,

ADAT, etc.)

•Non-Audio data

DAC1 USB

Instruction Manual Revision D Page 10

Standby Mode

The DAC1 USB features an automatic

standby mode that eliminates the need to

turn the converter on and off. Standby

Mode starts 15 seconds after a digital source

device is turned off, disconnected, or contains

errors that prevent D/A conversion. All status

LED’s are off while in Standby Mode.

While in Standby Mode, the DAC1 USB

continues to monitor the selected digital input

and will immediately resume normal

operation when an error-free signal is

restored.

HPA2TM Stereo Headphone

Jacks

There are two stereo headphone jacks. The

left-hand jack is equipped with a switch that

mutes the XLR and RCA analog outputs when

a headphone plug is inserted. The right-hand

jack has no switch. This gives the user the

option of muting the analog outputs when

using headphones. Internal jumpers are

available to disable the headphone switch.

TIP: Use the left-hand jack when you

want to mute your playback system and

just listen to headphones. Use the right-

hand jack when you need to keep all

outputs active.

The dual jacks also allow two listeners to

monitor and compare notes on what is heard.

We recommend using identical headphones

because headphone sensitivities can differ

significantly. The Volume Control adjusts

the level at both jacks.

Because of the variations in headphone

sensitivity, the DAC1 USB features two gain

ranges for the headphone outputs. Our

experience with the classic DAC1 showed us

that most users cannot use the full output of

the HPA2™. These users benefit from a

reduced maximum gain. Internal jumpers

reduce the input to the HPA2™ by 10 dB and

place the Volume Control near 12 O’clock at

a comfortable listening level with most

headphones. These jumpers are factory

installed, but can be removed if a user needs

more output. Removing the jumpers

increases the gain to a level that is equal to

that of the classic DAC1.

TIP: For optimal L/R balance, the

headphone gain jumpers should be set

so that comfortable listening levels occur

when the ‘Volume Control’ is set above

the 10th detent.

Instructions for setting the headphone gain

range and headphone mute switch are

detailed in the ‘Internal Settings’ section of

this manual.

Volume Control

The front-panel Volume Control is a 41-

detent potentiometer (see ‘Volume Control

Curve’ in the ‘Performance Graphs’ section of

this manual).

The Volume Control always controls the

output level of the headphone jacks. It can

also be used to control the output levels of

the balanced XLR and unbalanced RCA analog

outputs when the rear-panel Output Level

Switch is set to Variable.

The XLR outputs have jumper-enabled pads

that can be used to optimize the gain

structure of the playback system.

TIP: For optimal L/R balance, and

minimal noise, the XLR gain jumpers

should be set so that comfortable

listening levels occur when the ‘Volume

Control’ is set above the 10th detent.

Instructions for setting the XLR pads are

detailed in the ‘Internal Settings’ section of

this manual. The DAC1 USB is shipped with

the XLR attenuation set to -20 dB.

DAC1 USB

Instruction Manual Revision D Page 11

Rear Panel

Digital Inputs

There are four digital inputs on the DAC1

USB. These inputs are selected from the

front-panel toggle switch.

The coaxial, XLR, and optical inputs can

decode AES/EBU and S/PDIF input signals in

either professional or consumer formats.

TIP: The DAC1 USB will not decode AC3

or ADAT signals. The ‘Status Display’ will

flash when AC3, ADAT, or other non-PCM

input signals are connected to the

selected digital input.

The Benchmark UltraLock™ system removes

interface jitter from all inputs. The result is

that all digital inputs have identical jitter

performance.

TIP: Internal jumpers can be used to

determine which of the four inputs is

active when the DAC1 USB is powered

up. Factory default is input 4 (USB).

Input 1 - SPDIF/AES BNC

The coaxial input uses a female BNC

connector that is securely mounted directly to

the rear panel. The input impedance is 75

Ohms. Maximum word length is 24-bits. All

sample rates between 28 and 195 kHz are

supported.

The BNC input is DC isolated, transformer

coupled, current limited, and diode protected.

The BNC body is bonded directly to the

chassis to prevent currents in the internal

ground systems. This direct bonding also

maximizes RF shielding.

TIP: Shielded 75-Ohm coaxial cable is

highly recommended for stable

performance. Do not use 50-Ohm cables.

The BNC input accepts AES/EBU or S/PDIF

digital audio formats. The BNC connector is

specified by the AES3-id and SMPTE 276M

standards for 75-Ohm 1 Vpp digital audio

signals and is commonly used in video

production facilities. IEC 609588-3 specifies

the use of an RCA type connector for 75-Ohm

0.5 Vpp consumer-format digital audio signals

(commonly known as S/PDIF). The coaxial

input on the DAC1 USB is designed to accept

either type of signal.

We have chosen to use a BNC connector

because of its superior reliability and RF

performance. The DAC1 USB comes with a

BNC-to-RCA adapter to allow easy interfacing

with consumer S/PDIF equipment.

TIP: The BNC input has a 75-Ohm

internal termination that may be

DAC1 USB

Instruction Manual Revision D Page 12

disabled by removing a jumper (JP7).

This termination is required for normal

operation, but may be removed if the

user wishes to loop a single coaxial feed

through several other pieces of

equipment.

A 75-Ohm termination must be applied at the

last device on the loop, and there should be a

combined total of less than 6 feet of cable

between the first and last receive device.

Input 2 – AES/EBU XLR

This input uses a gold-pin Neutrik™ female

XLR connector. The input is balanced and has

an input impedance of 110 Ohms. Maximum

word length is 24-bits. All sample rates

between 28 and 195 kHz are supported.

This input is DC isolated, transformer

coupled, current limited, and diode protected.

The XLR shell and pin 1 (ground) are both

directly bonded to the chassis to prevent

currents in the internal ground systems. This

direct bonding also maximizes RF shielding.

The XLR input is designed to accept standard

4 Vpp AES signals, and will work reliably with

levels as low as 300 millivolts. Receive errors

will occur (and the DAC1 USB will mute)

when the peak-to-peak input voltage is less

than about 160 millivolts at the XLR input.

TIP: Shielded 110-Ohm AES/EBU digital

audio cable is highly recommended for

stable performance. For improved

shielding, we also recommend selecting

digital cables that have the connector

shells bonded to the cable shield.

Input 3 – Optical

The optical input connector is manufactured

by Toshiba and is commonly known as a

TOSLINK connector. The TOSLINK optical

connector used on the DAC1 USB is designed

to work well at sample rates up to 192 kHz.

Maximum word length is 24-bits. All sample

rates between 28 and 195 kHz are supported.

Input 4 – USB

The USB input accepts a ‘B-type’ male USB

1.1 or USB 2.0 connector. An ‘A-B type’ USB

cable is provided with the DAC1 USB. The

USB cable connects the DAC1 USB directly to

a computer’s USB output. The USB interface

utilizes USB 1.1 protocol, and is compatible

with both USB 1.1 and USB 2.0 ports.

The USB input supports 44.1, 48, 88.2 and 96

kHz sample rates at word lengths up to 24-

bits. The USB interface acts as a ‘native’ USB

audio device and does not require the

installation of any custom drivers.

Benchmark’s Advanced USB Audio

technology achieves bit-transparent operation

without special drivers and without changing

system settings.

The Benchmark USB interface is truly a plug-

and-play solution. The DAC1 USB can begin

streaming high resolution audio bit-

transparently within seconds after being

plugged into a computer for the first time. No

software or hardware configuration is

required.

The DAC1 USB is designed, tested and

proven compatible with the following four

operating systems:

•Windows Vista

•Windows XP

•Windows 2000

•Mac OS X *

* TIP – When using OS X the system

sample rate should be set to match the

sample rate of the files being played.

Also, we do not recommend using the OS

X system volume control – set it to

100%.

DAC1 USB

Instruction Manual Revision D Page 13

Analog Outputs

The DAC1 USB has two unbalanced RCA

outputs and two balanced XLR outputs.

The DAC1 USB features new high-current

output drivers that are capable of driving

300-Ohm loads without an increase in

distortion. They are also well suited for

driving long cables or high-capacitance loads.

Note: The XLR and RCA output levels are

controlled by the Volume Control level when

the Output Level Switch is set to variable.

Otherwise the levels are set by the 10-turn

calibration trimmers located on the rear

panel.

The XLR outputs are equipped with low-

impedance passive output attenuators that

can be set at 0 dB, -10 dB, -20 dB, or -30 dB

to allow interfacing to a wide variety of audio

devices without any loss of dynamic range.

Output Level Switch

The Output Level Switch is a

three-position toggle switch

located on the rear panel. The

DAC1 USB ships with this

switch set in the Variable

position.

CAUTION: Do not set the ‘Output Level

Switch’ to ‘Calibrated’ if you are directly

driving a power amplifier or powered

speakers. The ‘Calibrated’ setting

produces an output that is near full-

volume and may damage your speakers.

Calibrated (UP) – Analog output levels are

controlled by 10-turn rear-panel trim controls.

Off (CENTER) – Analog XLR and RCA outputs

are muted; headphone outputs remain active.

Variable (DOWN) – Analog output levels are

controlled by the Volume Control.

The Output Level Switch does not affect the

operation of the headphone jacks (the

headphone outputs are never disabled and

the headphone level is always controlled from

the Volume Control).

TIP: If the DAC1 USB is being used in a

critical signal chain (such as a broadcast

facility or theater) the headphone mute

switch should be defeated using the

internal jumpers. See ‘Internal Settings’

for instructions.

Balanced XLR Analog Line

Outputs

The Left and Right balanced outputs use

Neutrik™ gold-pin male XLR jacks. The XLR

shell and pin 1 (ground) are both directly

bonded to the chassis to prevent currents in

the internal ground systems. This direct

bonding also maximizes RF shielding.

The XLR output levels may be controlled from

the front panel, or may be set to fixed levels

using the rear-panel Calibration Trimmers.

The XLR outputs have passive attenuators

that allow direct connections to a wide variety

of audio devices without a loss of dynamic

range. The 20 dB pad is usually required for

direct interfacing to power amplifiers and

powered speakers. The DAC1 USB ships

with the 20 dB pad enabled.

Industry-standard XLR wiring:

XLR pin 2 = + Audio Out

XLR pin 3 = - Audio Out

XLR pin 1 = Cable Shield

CAUTION: If the balanced XLR outputs

are wired to an unbalanced input (using

a special adapter cable), pin 3 must be

left floating. Shorting pin 3 to ground

will increase the temperature of the

DAC1 USB

Instruction Manual Revision D Page 14

output drivers, will increase power

consumption, and may cause distortion.

Unbalanced RCA Analog

Outputs

The Left and Right unbalanced outputs use

standard RCA style jacks. The

ground connections are bonded

to chassis ground at the

location where analog ground is

bonded to the chassis. This

minimizes the effects of ground

loops caused by AC currents in

the cable shield.

The RCA output levels may be controlled from

the front panel, or may be set to fixed levels

using the rear-panel Calibration Trimmers.

In Calibrated mode the RCA outputs are

factory preset to –10 dBV at -20 dBFS. This

is typical for most consumer-grade

equipment.

TIP: Mono summing with an RCA ‘Y’

cable is not recommended as this will

cause high amounts of distortion. Mono

summing with a ‘Y’ cable can be

accomplished with the use of a modified

cable by implementing a 1k Ohm series

resistor in each leg of the ‘Y’.

Note: The XLR pads do not have any effect

on the level of the RCA outputs.

The RCA output impedance is very low (30

Ohms). This makes these outputs well suited

for driving high-capacitance loads and/or

high-capacitance cables.

TIP: The RCA outputs are capable of

driving cables as long as 1360 feet (see

Table 1). But, long un-balanced cables

will generally suffer from hum problems

due to ground loops. We highly

recommend using balanced

interconnects for long runs.

Low-Impedance Passive Pads

The XLR outputs are equipped with low-

impedance passive pads that may be used to

reduce the output levels while preserving the

full dynamic range of the DAC1 USB. The

DAC1 USB ships with the 20 dB pads

enabled.

TIP: When directly driving power

amplifiers and powered speakers, use

‘Variable’ mode and start with the

factory default 20 dB pad setting. If

necessary, change the pads to achieve a

normal listening level when the ‘Volume

Control’ is near mid-rotation.

When the output pads are enabled, the

output impedance changes slightly, and the

maximum allowable cable length should be

reduced as shown in Table 1 (assuming 32

pF/foot and a maximum allowable loss of 0.1

dB at 20 kHz).

Table 1 - Cable Drive Capability

Balanced Output Drive Capability:

A

ttenuator Output Maximum Loss in dB

Setting (dB) Impedance Cable (ft) at 20 kHz

0 60 680 0.1

10 425 96 0.1

20 135 302 0.1

30 43 949 0.1

Unbalanced Output Drive Capability:

Output Maximum Loss in dB

Impedance Cable (ft) at 20 kHz

30 1360 0.1

TIP: To set the XLR outputs to typical

professional studio levels, set the pads

to 0 dB, and set the ‘Output Level Switch’

to ‘Calibrated’. If the factory settings of

the ‘Calibration Trimmers’ have not been

changed, the XLR outputs will be

calibrated to +4 dBu at -20 dBFS, and the

RCA outputs will be calibrated to -10 dBV

at -16 dBFS.

DAC1 USB

Instruction Manual Revision D Page 15

Calibration Trimmers

The Calibration Trimmers are

located to the left and right of the

Output Level Switch. They are

10-turn trimmers and are

accessible through the rear panel

using a small screwdriver.

These trimmers provide a 2 dB per rotation

adjustment with a total control range of + 9

to +29 dBu at 0 dBFS (full-scale digital

input). There are no stops at either end of

the 10-turn rotation.

CAUTION: Do not change the calibration

trimmers unless you have the ability to

accurately measure audio levels.

Factory calibration has been set so that the

output level at the balanced XLR connectors is

+4 dBu at -0 dBFS. This is exactly 20 dB

lower than a typical alignment of +4 dBu at

-20 dBFS. The lower level is appropriate for

most powered monitors.

TIP: To set the XLR outputs to typical

professional studio levels, set the pads

to 0 dB, and set the ‘Output Level Switch’

to ‘Calibrated’. If the factory settings of

the ‘Calibration Trimmers’ have not been

changed, the XLR outputs will be

calibrated to +4 dBu at -20 dBFS, and the

RCA outputs will be calibrated to -10 dBV

at -16 dBFS.

The factory-preset levels may be increased by

5 dB or decreased by 15 dB in order to

conform to other studio reference levels. This

range of levels is also well suited for direct

connection to the balanced line-level inputs

on most power amplifiers. Most professional

equipment will work well at these levels.

Note: The Calibration Trimmers have no

effect on the output levels when the Output

Level Switch is set to Variable.

AC Power-Entry Module

The AC power input uses a standard IEC type

connector. One USA-compatible power cord

is included with DAC1 USB converters

shipped to North America. IEC style power

cords in country-specific configurations are

available in your locality.

Fuse Holder

The fuse holder is built into a drawer next to

the IEC power connector. The drawer

requires two 5 x 20 mm 250 V Slo-Blo®Type

fuses. The drawer includes a voltage

selection switch with two settings: 110 and

220. The fuse rating for all voltage settings

is 0.50 Amps.

The AC input has a very wide input voltage

range and can operate over a frequency

range of 50 to 60 Hz. At 110, the DAC1

USB will operate normally over a range of 90

to 140 VAC. At 220, the DAC1 USB will

operate normally over a range of 175 to 285

VAC.

Caution: Always install the correct fuses.

Always insure that the voltage setting is

correct for your locality.

DAC1 USB

Instruction Manual Revision D Page 16

Rack Mounting

(DAC1 USB Black RM only)

The rack-mount version of the DAC1 USB is

part of Benchmark’s ½-wide System1™

product family. Each is one rack unit high

and is exactly ½ the width of a standard 19”

rack panel. The front panels on System1™

products have rack-mount holes that are

machined to conform to standard rack-mount

dimensions. Two ½-wide System1™ units

may be joined together to form a single rigid

19” panel that can be installed in any

standard 19” rack.

Either ear of a ½-wide System1™ device can

be mounted directly to a standard 19” rack.

A Rack Mount Coupler connects the other

ear to a ½-wide Blank Rack Panel or

another ½-width System1™ product

TIP: Use the rack-mount screws supplied

with the DAC1 USB (or screws with

plastic washers) to avoid scratching the

surface of the faceplate.

The Rack Mount Coupler and Blank Rack

Panel are available from Benchmark.

Call us, visit our website

(http://www.BenchmarkMedia.com), or

contact your dealer to purchase these

accessories.

Rack Mount Coupler

The Rack Mount Coupler is a machined

aluminum junction block that joins any two

½-wide System1™ devices for rack

mounting. It is also used to join a Blank

Rack Panel to a single ½-wide System1™

device.

Blank Rack Panel

The Blank Rack Panel is a ½-wide 1-RU

aluminum panel for mounting a single ½-wide

System1™ device in a standard 19” rack.

Installation requires one Rack Mount

Coupler.

DAC1 USB

Instruction Manual Revision D Page 17

Benchmark

Technologies

HPA2™ Headphone Amplifier

The DAC1 USB headphone output is driven

by Benchmark’s signature HPA2™ headphone

amplifier. This high-current, high-output

amplifier has an output impedance of near 0-

Ohms. It is designed to drive loads as low as

30 Ohms without any increase in distortion.

It also has sufficient amplitude to drive low-

sensitivity 600-Ohm headphones.

The HPA2™ includes current-limiting circuits

that fully protect against damage from short

circuits. This is important because the right

channel of a headphone amplifier will

experience a short whenever a mono phone

plug is inserted into the stereo headphone

jack. Shorts may also occur when a plug is

partially inserted.

0-Ohm Output Impedance

Most headphone amplifiers use series

resistors to maintain stability and protect

against short-circuit conditions. These

resistors are usually at least 30 Ohms, and

have a negative impact on performance. A

headphone amplifier with series resistors may

measure very well when driving resistive

loads. However, the same amplifier will

measure very poorly when driving a

headphone load. Unfortunately, most

manufacturers do not specify headphone

amplifier performance with anything other

than ideal resistive loads. Our measurements

show that headphones do not behave like

resistive loads.

Headphone Performance

In our tests we have measured substantial

distortion across resistors that are wired in

series with headphones. We conducted

measurements with a variety of headphones.

In general, distortion increases as headphone

impedance decreases. This distortion can be

eliminated with a properly designed 0-Ohm

headphone amplifier.

The performance of the HPA2™ does not

change when headphones are driven. THD+N

measurements for no-load, 30-Ohm resistive

loads, 30-Ohm headphone loads, and 600-

Ohm headphone loads are virtually identical.

The HPA2™ will substantially improve the

sound of 30 and 60-Ohm headphones. It will

make very noticeable improvements with

600-Ohm headphones.

Headphone Gain Range

Because of the variations in headphone

sensitivity, the DAC1 USB features two gain

ranges for the headphone outputs. Our

experience with the classic DAC1 showed us

that most users cannot use the full output of

the HPA2™. These users benefit from a

reduced maximum gain. Internal jumpers

reduce the input to the HPA2™ by 10 dB and

place the Volume Control near 12 O’clock at

a comfortable listening level with most

headphones. These jumpers are factory

installed, but can be removed if a user needs

more output. Removing the jumpers

increases the gain to a level that is equal to

that of the classic DAC1.

TIP: For optimal L/R balance, the

headphone gain jumpers should be set

so that comfortable listening levels occur

when the ‘Volume Control’ is set above

the 10th detent.

Instructions for setting the headphone gain

range and headphone mute switch are

detailed in the ‘Internal Settings’ section of

this manual.

DAC1 USB

Instruction Manual Revision D Page 18

UltraLock™ Clock System

Accurate 24-bit audio conversion requires a

very low-jitter conversion clock. Jitter can

very easily turn a 24-bit converter into a 16-

bit converter (or worse). There is no point in

buying a 24-bit converter if clock jitter has

not been adequately addressed.

Jitter is present on every digital audio

interface. This type of jitter is known as

‘interface jitter’ and it is present even in the

most carefully designed audio systems.

Interface jitter accumulates as digital signals

travel down a cable and from one digital

device to the next. If we measure interface

jitter in a typical system we will find that it is

10 to 10,000 times higher than the maximum

allowable level for accurate 24-bit conversion.

Fortunately, interface jitter has absolutely no

effect on the audio unless it influences the

conversion clock in an analog-to-digital

converter (A/D) or in a digital-to-analog

converter (D/A).

Many converters use a single-stage Phase

Lock Loop (PLL) circuit to derive their

conversion clocks from AES/EBU, Wordclock,

or Superclock reference signals. Single-stage

PLL circuits provide some jitter attenuation

above 5 kHz but none below 5 kHz.

Unfortunately, digital audio signals often have

their strongest jitter components at 2 kHz.

Consequently, these converters can achieve

their rated performance only when driven

from very low jitter sources and through very

short cables. It is highly unlikely that any

converter with a single-stage PLL can achieve

better than 16 bits of performance in a typical

installation. Specified performance may be

severely degraded in most installations.

Better converters usually use a two-stage PLL

circuit to filter out more of the interface jitter.

In theory, a two-stage PLL can remove

enough of the jitter to achieve accurate 24-bit

conversion (and some do). However, not all

two-stage PLL circuits are created equal.

Many two-stage PLL’s do not remove enough

of the low-frequency jitter. In addition, two-

stage PLL circuits often require several

seconds to lock to an incoming signal.

Finally, a two-stage PLL may fail to lock when

jitter is too high, or when the reference

sample frequency has drifted.

UltraLock™ converters exceed the jitter

performance of two-stage PLL converters, and

are free from the slow-lock and no-lock

problems that can plague two-stage PLL

designs. UltraLock™ converters have

extremely high immunity to interface jitter

under all operating conditions. No jitter-

induced artifacts can be detected using an

Audio Precision System 2 Cascade test set.

Measurement limits include detection of

artifacts as low as –140 dBFS, application of

jitter amplitudes as high as 12.75 UI, and

application of jitter over a frequency range of

2 Hz to 200 kHz. Any AES/EBU signal that

can be decoded by the AES/EBU receiver will

be reproduced without the addition of any

measurable jitter artifacts.

The DAC1 USB, DAC1, DAC-104, ADC1 and

the ADC-104 employ Benchmark’s

UltraLock™ technology to eliminate jitter-

induced performance problems. UltraLock™

technology isolates the conversion clock from

the digital audio interface clock. Jitter on a

D/A digital audio input, or an A/D reference

input can never have any measurable effect

on the conversion clock of an UltraLock™

converter. In an UltraLock™ converter, the

conversion clock is never phase-locked to a

reference clock. Instead the converter

oversampling-ratio is varied with extremely

high precision to achieve the proper phase

relationship to the reference clock. The clock

isolation of the UltraLock™ system insures

that interface jitter can never degrade the

quality of the audio conversion. Specified

performance is consistent and repeatable in

any installation with cables of any quality

level!

How does conversion clock jitter

degrade converter performance?

Problem #1: Jitter phase modulates the

audio signal. This modulation creates

sidebands (unwanted tones) above and below

every tone in the audio signal. Worse yet,

these sidebands are often widely separated

from the tones in the original signal.

DAC1 USB

Instruction Manual Revision D Page 19

Jitter-induced sidebands are not musical in

nature because they are not harmonically

related to the original audio. Furthermore,

these sidebands are poorly masked (easy to

hear) because they can be widely separated

above and below the frequencies of the

original audio tones. In many ways, jitter

induced distortion resembles intermodulation

distortion (IMD). Like IMD, jitter induced

distortion is much more audible than

harmonic distortion, and more audible than

THD measurements would suggest.

Jitter creates ‘new audio’ that is not

harmonically related to the original audio

signal. This ‘new audio’ is unexpected and

unwanted. It can cause a loss of imaging, and

can add a low and mid frequency ‘muddiness’

that was not in the original audio.

Jitter induced sidebands can be measured

using an FFT analyzer.

Problem #2: Jitter can severely degrade the

anti-alias filters in an oversampling converter.

This is a little known but easily measurable

effect. Most audio converters operate at high

oversampling ratios. This allows the use of

high-performance digital anti-alias filters in

place of the relatively poor performing analog

anti-alias filters. In theory, digital anti-alias

filters can have extremely sharp cutoff

characteristics, and very few negative effects

on the in-band audio signal. Digital anti-alias

filters are usually designed to achieve at least

100 dB of stop-band attenuation. But, digital

filters are designed using the mathematical

assumption that the time interval between

samples is a constant. Unfortunately, sample

clock jitter in an A/D or D/A varies the

effective time interval between samples. This

variation alters the performance of these

carefully designed filters. Small amounts of

jitter can severely degrade stop-band

performance, and can render these filters

useless for preventing aliasing.

The obvious function of a digital anti-alias

filter is the removal of audio tones that are

too high in frequency to be represented at the

selected sample rate. The not-so-obvious

function is the removal of high-frequency

signals that originate inside the converter

box, or even originate inside the converter IC.

These high-frequency signals are a result of

crosstalk between digital and analog signals,

and may have high amplitudes in a poorly

designed system. Under ideal (low jitter)

conditions, a digital anti-alias filter may

remove most of this unwanted noise before it

can alias down into lower (audio) frequencies.

These crosstalk problems may not become

obvious until jitter is present.

Stop-band attenuation can be measured very

easily by sweeping a test tone between 24

kHz and at least 200 kHz while monitoring the

output of the converter.

Put UltraLock™ converters to the

test:

We encourage our customers to perform the

above tests on UltraLock™ converters (or let

your ears be the judge). There will be

absolutely no change in performance as jitter

is added to any digital input on an

UltraLock™ converter. Try the same tests

on any converter using conventional single or

two-stage PLL circuits. Tests should be

performed with varying levels of jitter and

with varying jitter frequencies. The results will

be very enlightening. Jitter related problems

have audible (and measurable) effects on A/D

and D/A devices. Practitioners of Digital Audio

need to understand these effects.

Is it possible to eliminate all of

the effects of jitter in an entire

digital audio system?

Interface jitter will accumulate throughout

even the most carefully designed digital audio

system. Fortunately, interface jitter can

only degrade digital audio if it affects the

sampling circuit in an analog-to-digital or

digital-to-analog converter. Any attempt to

cure jitter outside of an A/D or D/A will prove

expensive and, at best, will only partially

reduce jitter-induced artifacts. Dedicated

clock signals (word clock, and super clock,

etc.) are often distributed to A/D converters

and D/A converters in an attempt to reduce

jitter. Again, these are only partial solutions

because jitter even accumulates in these

clock distribution systems. Furthermore, a

DAC1 USB

Instruction Manual Revision D Page 20

poor quality master clock generator can

degrade the performance of the entire system

(if converter performance is dependent upon

reference clock quality). Jitter free A/D and

D/A converters are the only true insurance

against the ill effects of jitter. UltraLock™

converters are jitter-immune under all

operating conditions (they will never add

audible jitter induced artifacts to an audio

signal).

What UltraLock™ converters

cannot do:

UltraLock™ converters cannot undo damage

that has already been done. If an A/D with a

jitter problem was used to create a digital

audio signal, then there is nothing that can be

done to remove the damage. Jitter-induced

sidebands are extremely complex and cannot

be removed with any existing audio device.

Therefore, it is very important to attack jitter

at both ends of the audio chain. The DAC1

USB is a great start, as it will allow accurate

assessment of various A/D converters. It is

impossible to audibly evaluate A/D

performance without a good D/A. The

consistent performance delivered by the

DAC1 USB eliminates one major variable:

jitter.

Table of contents

Other Benchmark Media Converter manuals

Benchmark

Benchmark AD2402-96 User manual

Benchmark

Benchmark DAC3 HGC Quick start guide

Benchmark

Benchmark ADC16 User manual

Benchmark

Benchmark ADC1 USB User manual

Benchmark

Benchmark ADC1 USB User manual

Benchmark

Benchmark DAC1 HDR User manual

Benchmark

Benchmark DAC2 DX User manual

Benchmark

Benchmark DAC2 DX User manual

Benchmark

Benchmark DAC1 HDR User manual

Benchmark

Benchmark ADC1 USB User manual

Popular Media Converter manuals by other brands

Absolute Process Instruments

Absolute Process Instruments DuoPak APD 2010 manual

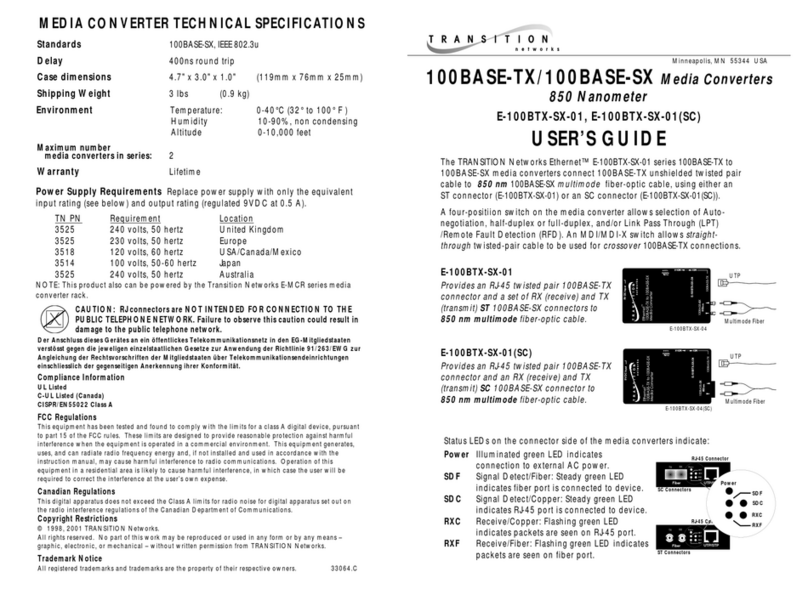

Transition Networks

Transition Networks NANOMETER E-100BTX-SX-01 user guide

Me

Me R189 user manual

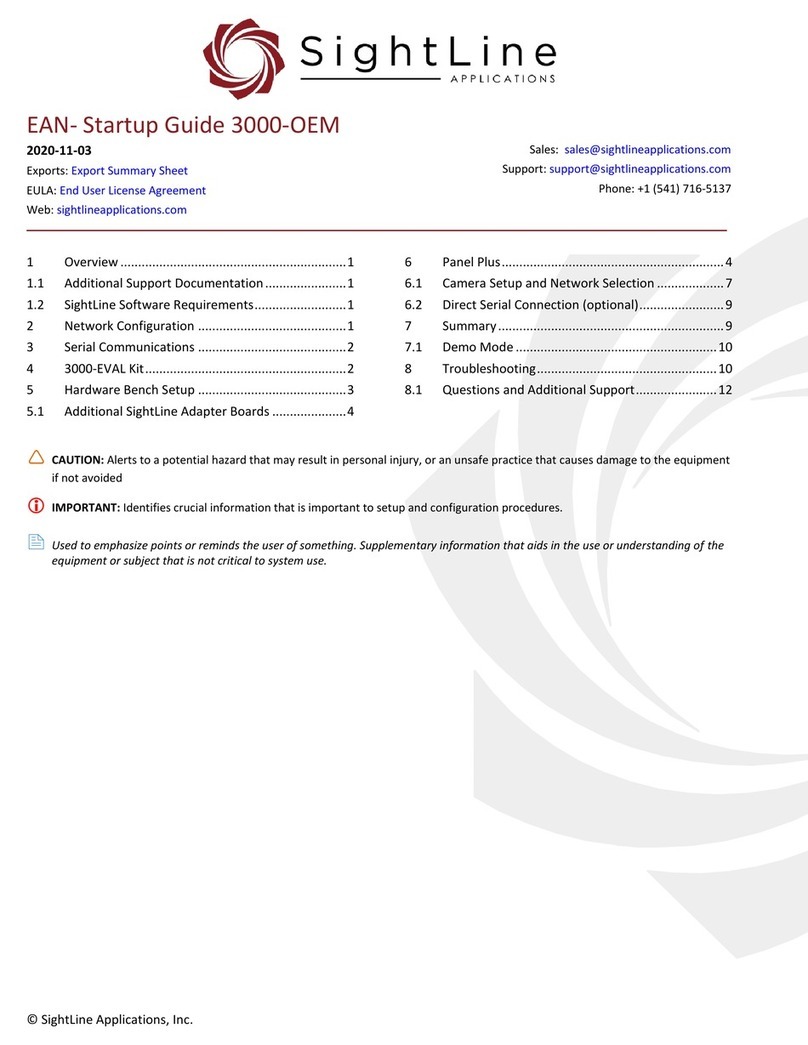

SightLine

SightLine 3000-OEM Startup guide

Vetra

Vetra SmartWye USB-311 User instructions

Elko

Elko inels RFSG-1M quick start guide