Con tents

Introduction &Features..........................................

1

Board layout ................................................................ 2

Installation....................................................................3- 15

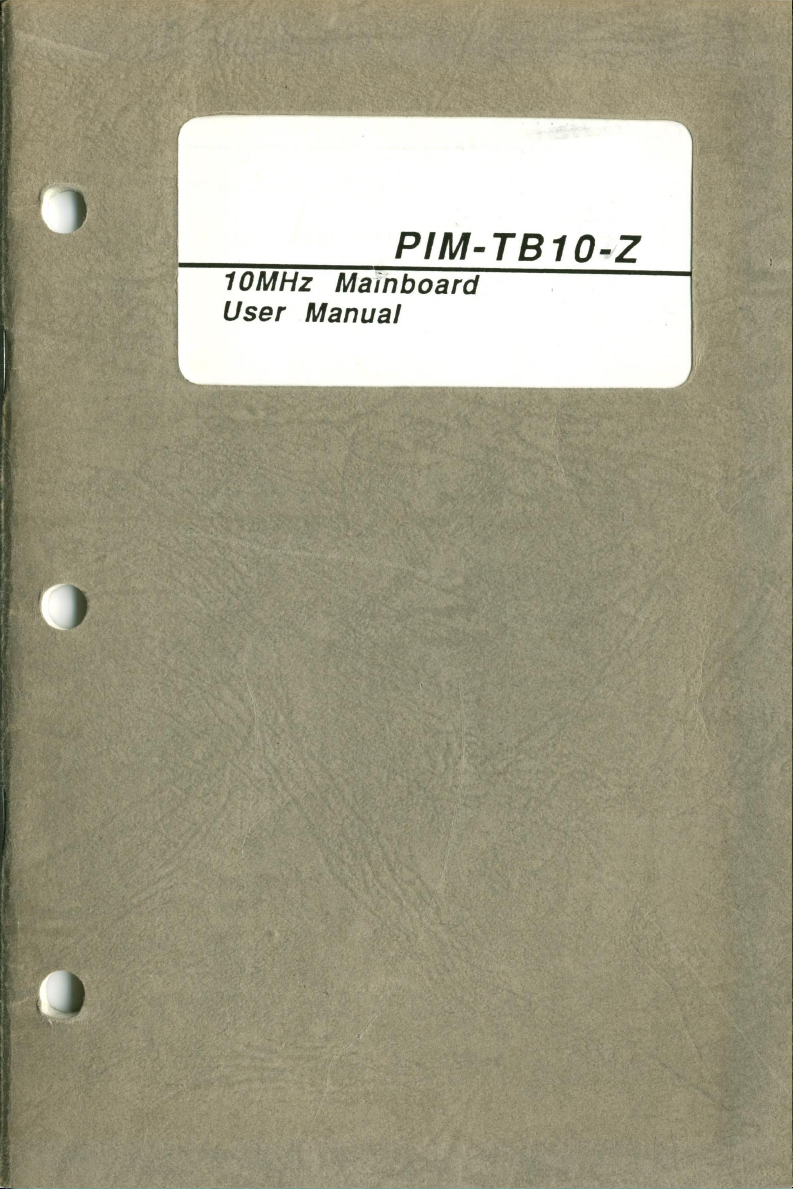

RAM installation &configuration ................................ 3-4

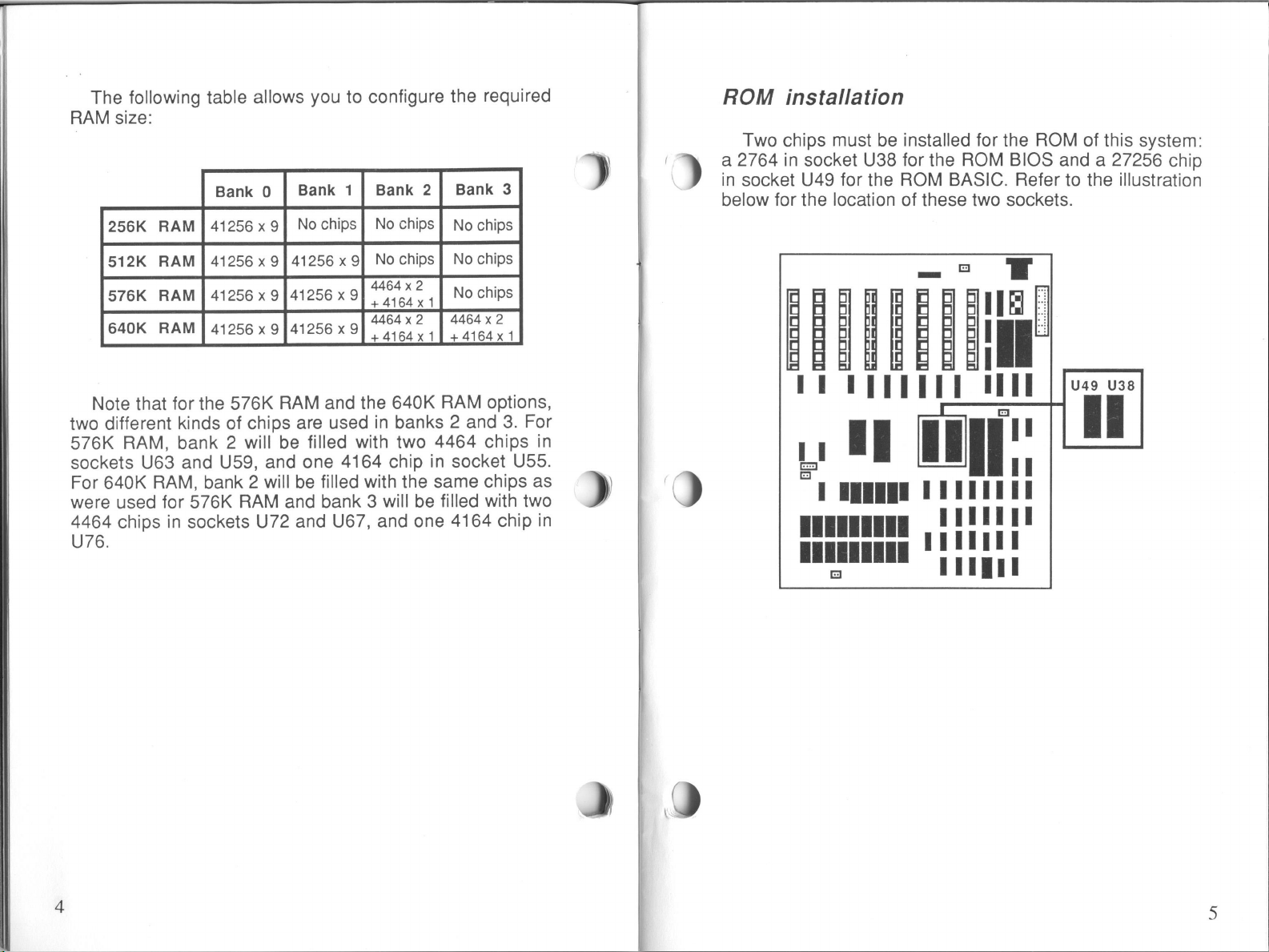

ROM installation ....................................................... 5

DIP switch settings ................................................... 6-8

Panel indicators and switches ....................................

9-10

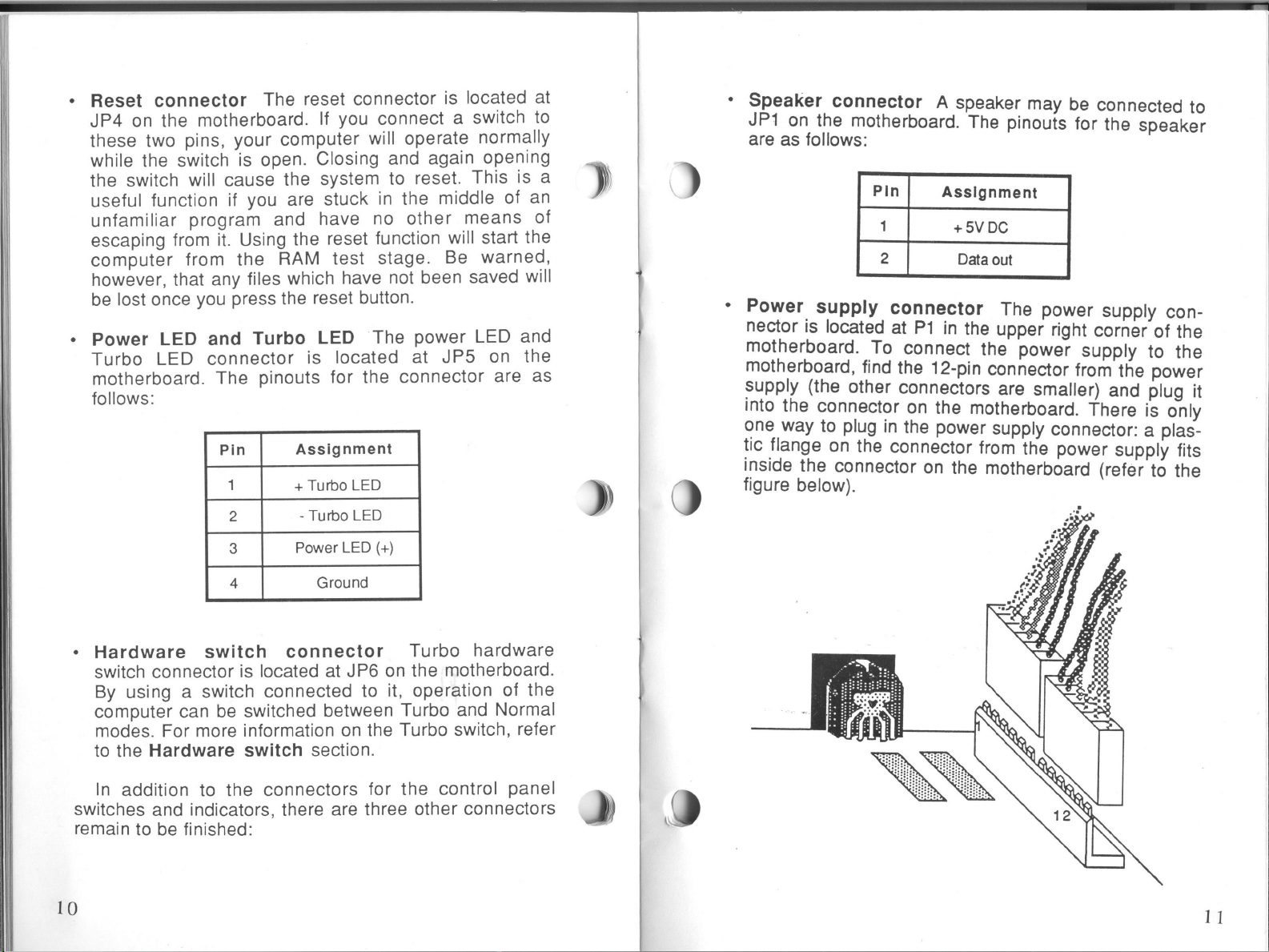

Speaker and power supply connector......... ....11-12

Keyboard connector................................................. 13

Fastening motherboard to case ................................. 14-15

Reconfiguring.............................................................. 16

Operation ...................................................................... 17-20

Obtaining 10MHz Turbo mode .................................. 18

Setting default operation mode ................................. 18

Software switch ........................................................ 18-19

Hardware switch ....................................................... 19

Alternate use of both switches .................................. 20

Turbo LED and hardware switch ................................ 20

Technical information ............................................. 21 -30

Introduction ............................................................. 21-22

DMA........................................................................ 22

Timer....................................................................... 22

Interrupt ................................................................... 23

Memory ................................................................... 23

Keyboard ................................................................. 23

Speaker ................................................................... 24

Expansion I/O channel..............................................24-25

I/O channel description ............................................. 26—29

Speaker interface ..................................................... 30

1

)

J.9

Introduction

You can rest assured of having made awise choice in

buying the PIM-TB10-Z motherboard for your personal

computer. This motherboard is not only compatible with

the PC/XT but provides you with these features:

-16-bit 8088-10 CPU or qualified 8088-2 CPU (optional

8087-1 coprocessor).

-Switchable processing speed in 10MHz (110% faster

than normal —4.77MHz) and 4.77MHz.

-Turbo/Normal modes selectable by either asoftware

switch or ahardware switch.

-Memory expandable to 640K on mainboard.

-ROM capacity —8K BIOS.

~LEGAL BIOS from ERSO (Electronics Research &

Organization),

8expansion slots.

4-channel DMA for disk and special I/O.

3-channel timer for music and time.

8-Ievel interrupt.

-IBM PC/XT® compatible.

-Operating systems :MS-DOS®, CPM/86®, CCP/M®.

-Speed test

by Norton® Utility :2.1

by Landmark® Speed Test Program :4.1

The clear, well-illustrated instructions in this manual

ensure that even if you are a newcomer to the computer

world, you will have your system installed and running

with the minimum of effort.