QSG-25850FMC

QSG-25850FMC Rev. B Holt Integrated Circuits

7

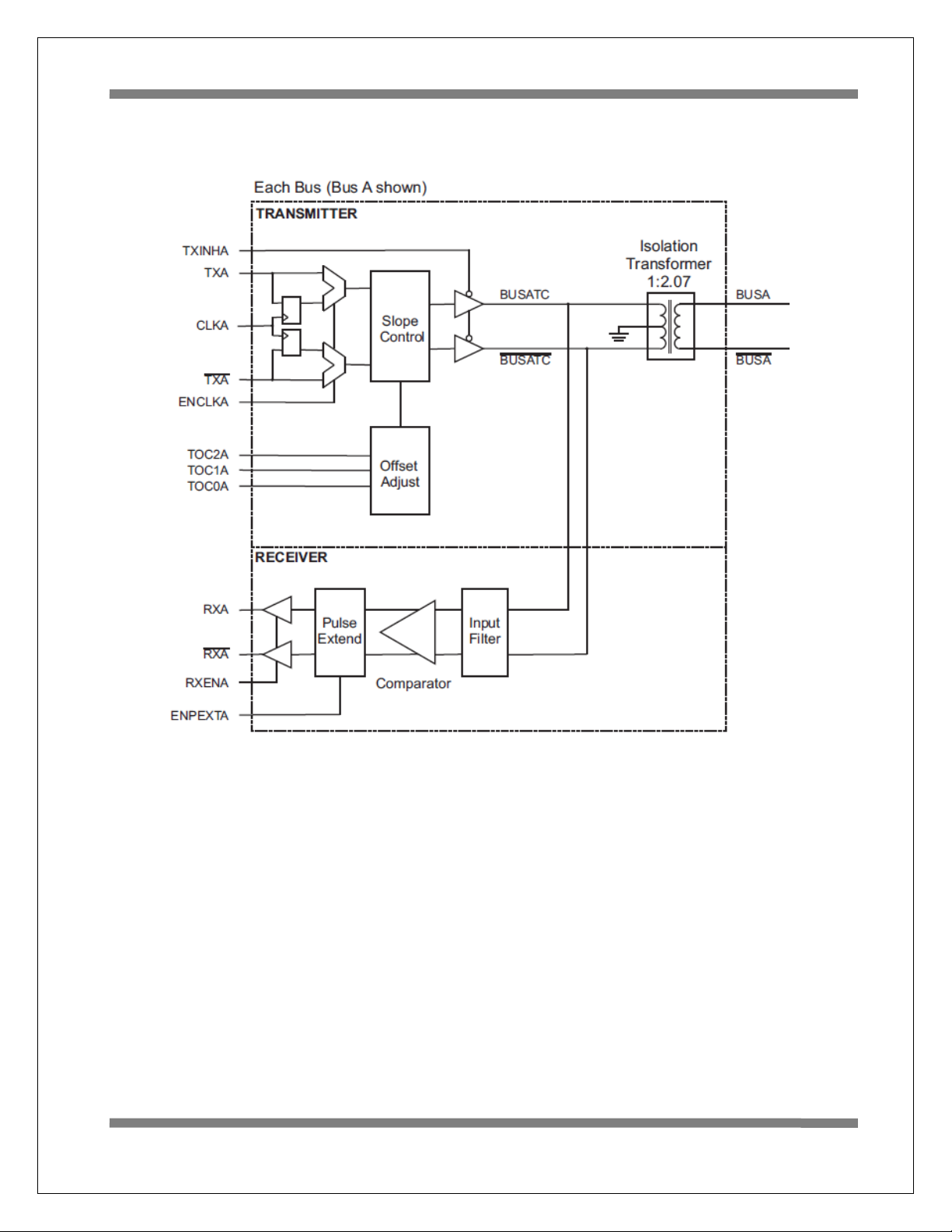

transformer-coupled), traditional transceivers produce narrow output pulses at RX and nRX because the

time that analog bus voltage exceeds the receiver threshold is much shorter than for a nominal or large

amplitude bus voltage. This function is enabled by opening SW1 or SW3 DIP switches which will assert

highs on the ENPEXTA and ENPEXTB pins of each device due to internal pull-ups. When these pins are

low, the comparator output is conventional.

Figure 4 - Bus Receiver Signal Path

Note: Receiver pulse stretching may cause issues with noise rejection, especially when noise pulses are

stretched in the intermessage gap just before or during command sync rising edge. For this reason, use

of receiver pulse width stretching should be weighed carefully against noise immunity considerations.

Bus Transmit Signal Path

A pair of CMOS logic-level inputs accepts bipolar serial signals for driving each bus from an external user-

provided Manchester encoder. Transmit for each bus can be enabled or inhibited using the

corresponding TXINH transmit inhibit signal.

The transmit signal path for each bus includes the bipolar TX and nix signals generated by the external

Manchester encoder. Signal quality concerns dictate that the TX/nix signals for each bus have matched

characteristics. This includes matched conductor length and impedance, matched layer-to-layer vias (or

even better, no vias). It is not always possible to achieve good matching on the board layout. The result:

TX and nTX switching transitions are not quite simultaneous; the TX/nTX crossover occurs early or late.

Crossover should occur mid-way between ground and the VDDIO supply rail to assure acceptable

“output symmetry” or “tail-off” occurring at the end of long transmit messages. This effect is discussed

at length in Holt application note AN-550.

Transmit Signal Sync Option

To accurately synchronize TX and nTX inputs, the HI-25850 offers the option to simultaneously clock

transmit input signals for each bus with a clock pulse input pin. When high, the CLKAEN input enables

synchronized TX and nTX inputs for bus A. With synchronization enabled (CLKENA = 1), the CLKA input

pin synchronizes TXA and nTXA for bus A transmit. If using an FPGA encoder, the user must provide a

brief positive clock pulse every time the TXA and nTXA signals change state. Logic levels present at the

TXA and nTXA inputs are latched by CLKA rising edge. If CLKENA is held low, the clocked input latches are

bypassed and the CLKA input has no effect.