Contents

©PHYTEC Messtechnik GmbH 2010 L-750e_1

Index of Figures ...........................................................................................3

Index of Tables.............................................................................................5

Conventions, Abbreviations and Acronyms..............................................1

Preface...........................................................................................................3

1Introduction.........................................................................................7

1.1 Block Diagram ...........................................................................10

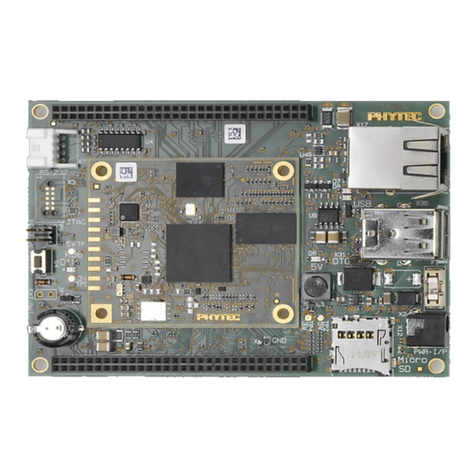

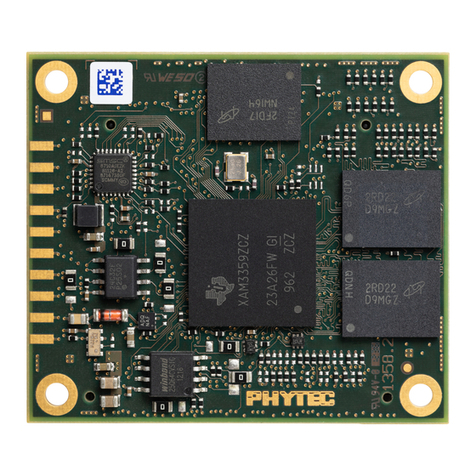

1.2 View of the phyCARD-M..........................................................11

1.3 Minimum Requirements to Operate the phyCARD-M..............13

2Pin Description..................................................................................14

3Jumpers..............................................................................................22

4Power..................................................................................................27

4.1 Primary System Power (VCC_3V3)..........................................27

4.2 Standby Voltage (VBAT)...........................................................28

4.3 On-board Voltage Regulator (U1)..............................................28

4.4 Supply Voltage for external Logic.............................................30

5Power Management ..........................................................................31

6System Configuration and Booting .................................................34

7System Memory.................................................................................38

7.1 DDR2-SDRAM (U8 - U11).......................................................38

7.2 NAND Flash Memory (U13) .....................................................39

7.3 I²C EEPROM (U6).....................................................................39

7.3.1 Setting the EEPROM Lower Address Bits (J1, J3, J4).40

7.3.2 EEPROM Write Protection Control (J16) ....................41

7.4 Memory Model...........................................................................41

8SD / MMC Card Interfaces..............................................................42

9Serial Interfaces.................................................................................44

9.1 Universal Asynchronous Interface.............................................45

9.2 USB-OTG Interface ...................................................................46

9.3 USB-Host Interface....................................................................47

9.4 Ethernet Interface .......................................................................48

9.4.1 PHY Physical Layer Transceiver (U7) .........................48

9.4.2 MAC Address................................................................50

9.5 I2C Interface ...............................................................................50

9.6 SPI Interface...............................................................................51

9.7 Synchronous Serial Interface (SSI)............................................51

10 General Purpose I/Os........................................................................53

11 Debug Interface (X1) ........................................................................54

12 LVDS Display Interface....................................................................57

12.1 Signal configuration (J22)..........................................................58

12.2 LVDS Display Interface pixel mapping.....................................58

13 LVDS Camera Interface...................................................................60