-

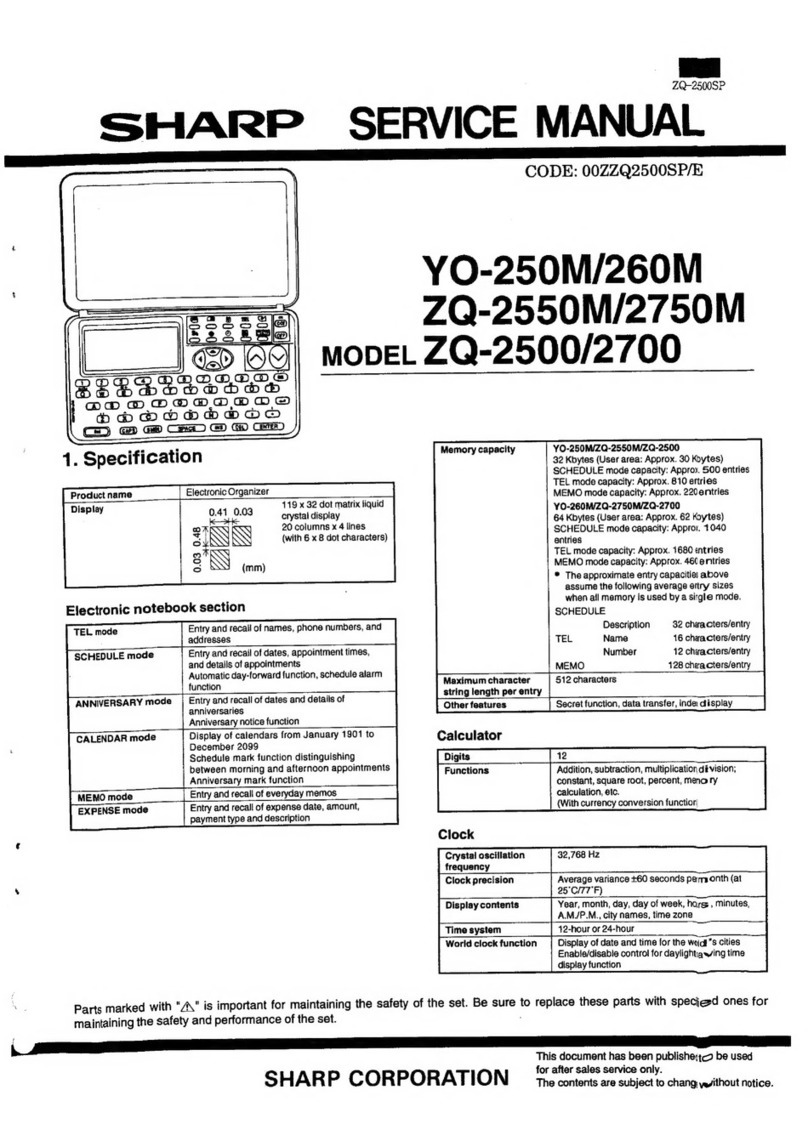

NZ-6600

SHARP

SERVICE

MANUAL

COD

E

:OO

Z

ft

I

Z5600Sft

l/ E

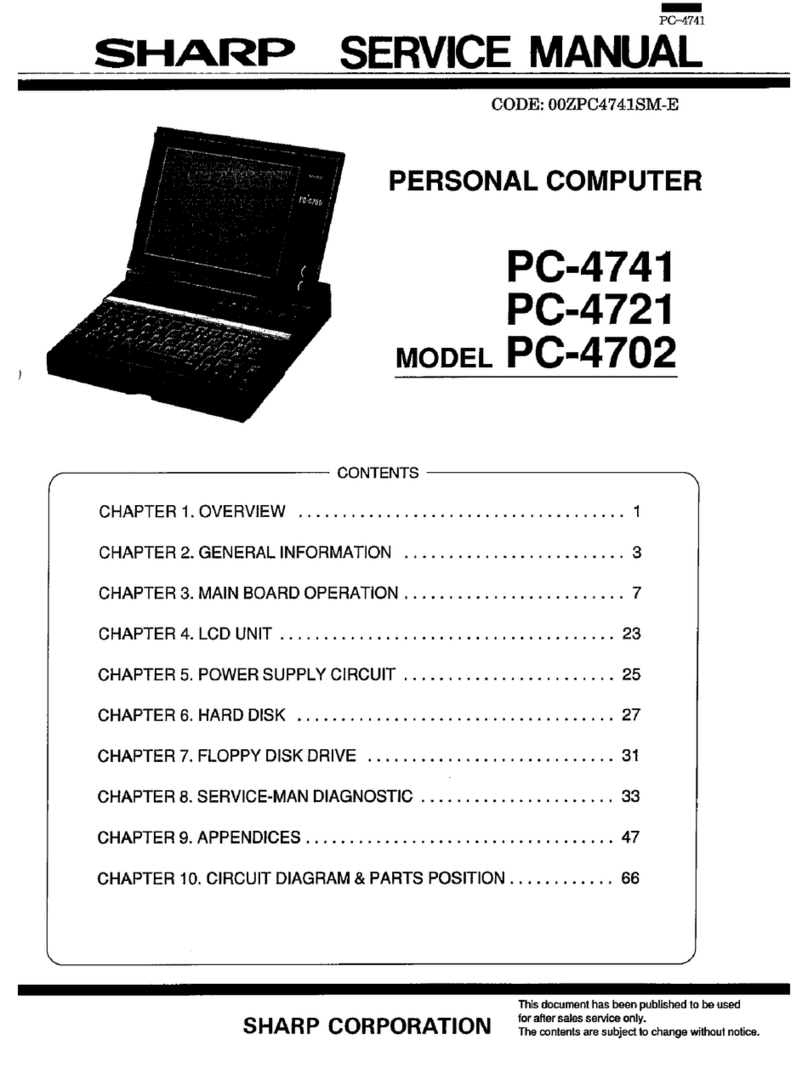

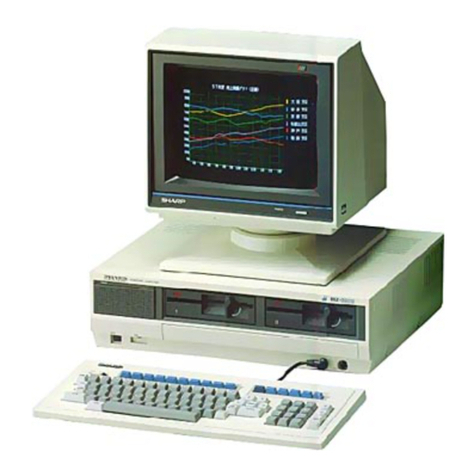

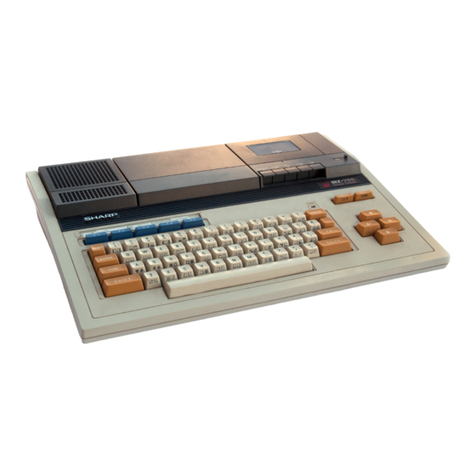

PERSONAL COMPUTER

MODEL

MZ-5600

~--------------

------

-

CO

NTENT

S--------

--

------------~

1.

MZ

5600

Series Hardware Description

.......

,

........................•...

1

2. Software Configuration

................................................

6

3. MZ-5600 System Block Diagram

........................................

13

4. The CPU and LIS Peripheral Logics

.......................

•

...........

,.

14

5.

Memory Control Logic

..•......................•....•......•.........

24

6.

I/O Decoder

Logi<;

............••....•.....•.........................•

28

7.

DMA

Interface Log;\:

......•...•.....•......•...........

•

..•..........

31

8.

MDF

Interface circuit

................................................

35

9 . Printer Interface

...................................................

44

10

.

ATC

Real Time

Clock·

...............................................

46

11. Programmab

le

Sound

Generator Interface

.................................

47

12. AS-232C Interface

................................

.

..................

48

13. Software Timer

.....................................................

51

14. Displav Interface

...........

.............

..

..

.....

.........

• .

........

54

15. KeVboard and KeVboard Interface

......................................

76

16. Power Circuit

......................................................

80

17. Self Cheek

.........................................................

84

18. Terminal View of Cable

...............................................

86

19. Circuit Diagram & Parts & Position

20. Parts

Lin

& Guide

SHARP CORPORATION ,