Description

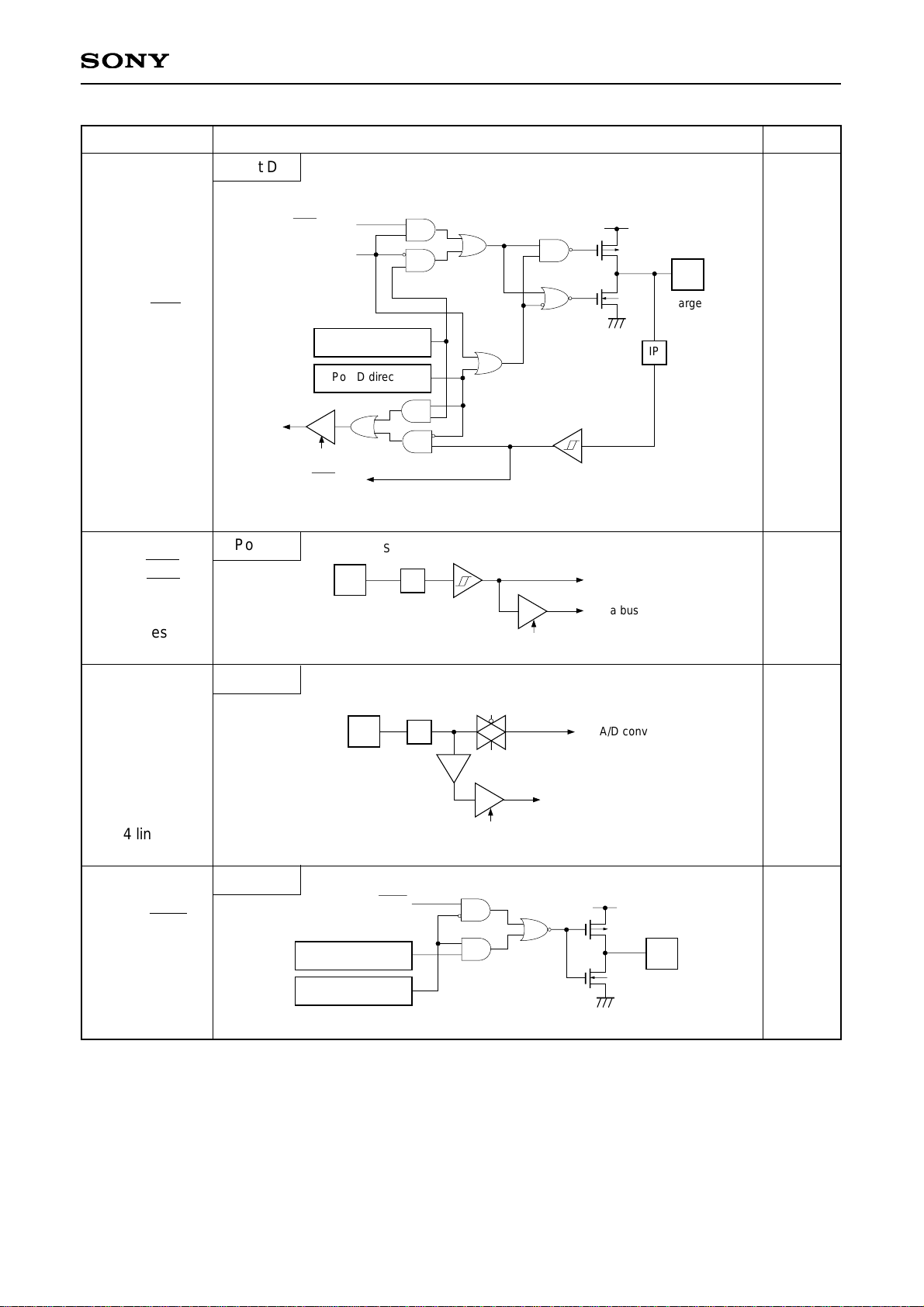

The CXP854P60 are a highly integrated micro-

computers composed of a 8-bit CPU, PROM, RAM,

and I/O ports. These chips feature many other high-

performance circuits in a single-chip CMOS design,

including an A/D converter, serial interface,

timer/counter, time-base timer, vector interrupt, on-

screen display function, I2C bus interface, PWM

generator, remote control receiver, HSYNC counter,

and watchdog timer.

Also, the CXP854P60 provides power-on reset

and sleep functions. The designers have ensured

low power consumption for these powerful micro-

computers.

Incorporating a one-time PROM, the CXP854P60

has an equivalent function to the CXP85460 and

character ROM for OSD can be written. Therefore, it

is suitable for evaluation in system development

and for the production of small amounts.

Features

•Instruction set which supports a wide array of data types-213 types of instructions which include 16-bit

calculations, multiplication and division arithmetic, and boolean operations.

•Minimum instruction cycle 0.5µs/8MHz

•On-chip PROM 60K bytes (For program)

10K bytes (For OSD)

•On-chip RAM 960 bytes

•On-screen display function 12 ×18 dots, 384 types, 12lines of 32 characters

Black frame output, half blanking, shadow, background color on full screen

Double scanning mode supported includes jitter elimination circuit

•I2C bus interface

•14-bit PWM output, 8-bit PWM output (8 channels)

•Remote control receiver circuit

•8-bit A/D converter (4 channels, 20µs conversion time/4MHz, 8MHz)

•HSYNC counter (2channels)

•Watchdog timer

•8-bit synchronized serial I/O

•8-bit timer, 8-bit timer/counter, 19-bit time-base timer

•General purpose input/output 32-line I/O (bit-selectable input/output), also 6-line input, 10-line output (internal

8-line Nch-O/D)

•Interrupts 13 factors, 13 vectors, multiple interrupt possible

•Standby mode SLEEP

•Package 64-pin plastic SDIP/QFP

Purchase of Sony's I2C components conveys a license under the Philips I2C Patent Rights to use these components

in an I2C system, provided that the system conforms to the I2C Standard Specifications as defined by Philips.

– 1 –

CXP854P60

E95109A16-PS

CMOS 8-bit Single-chip Microcomputer

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by

any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the

operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

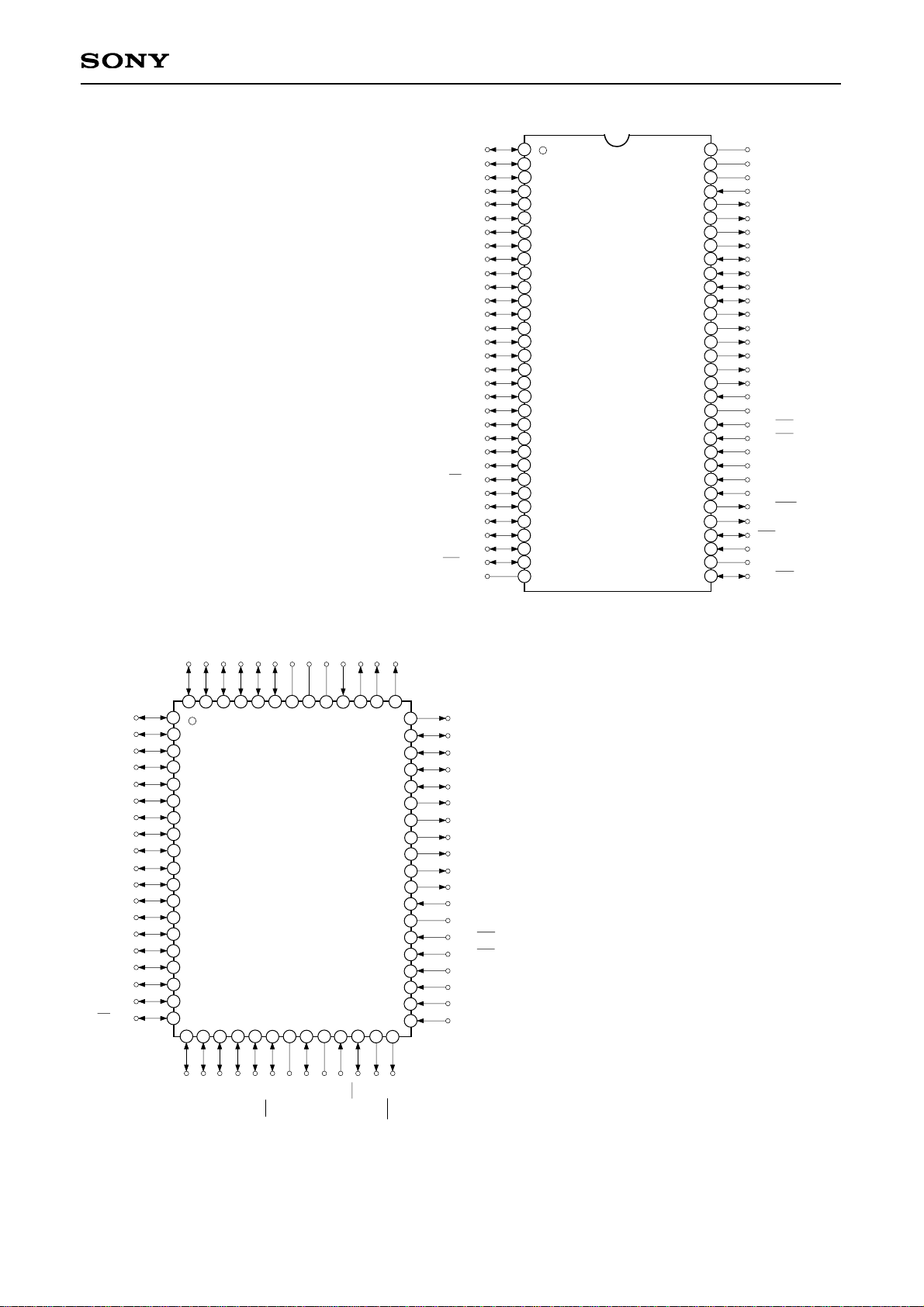

64 pin SDIP (PIastic) 64 pin QFP (PIastic)

Structure

Silicon gate CMOS IC