Texas Instruments TMS320DM646 Series User manual

Other Texas Instruments Controllers manuals

Texas Instruments

Texas Instruments TMS320x2833 series User manual

Texas Instruments

Texas Instruments MSMC User manual

Texas Instruments

Texas Instruments TPS51124 User manual

Texas Instruments

Texas Instruments TUSB422 EVM User manual

Texas Instruments

Texas Instruments TMS320 2833 Series User manual

Texas Instruments

Texas Instruments TMS320C2000 User manual

Texas Instruments

Texas Instruments LM5160A User manual

Texas Instruments

Texas Instruments UCC38500EVM User manual

Texas Instruments

Texas Instruments bq24013 User manual

Texas Instruments

Texas Instruments TPS53647 User manual

Texas Instruments

Texas Instruments TUSB5052 User manual

Texas Instruments

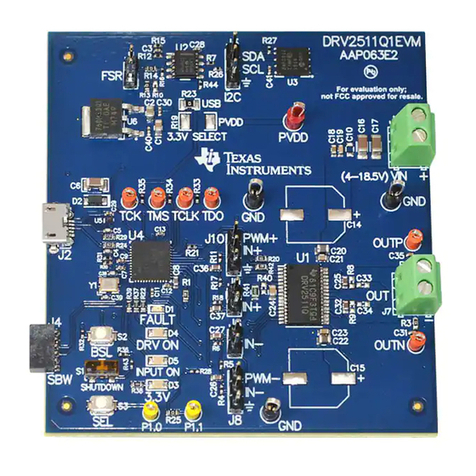

Texas Instruments DRV2511Q1EVM User manual

Texas Instruments

Texas Instruments DLP LightCrafter Dual DLPC900 Instruction sheet

Texas Instruments

Texas Instruments LM4040A User manual

Texas Instruments

Texas Instruments TMS370 Series User manual

Texas Instruments

Texas Instruments Stellaris MDL-BDC24 User manual

Texas Instruments

Texas Instruments bq24010/2 User manual

Texas Instruments

Texas Instruments bq78350-R1 Use and care manual

Texas Instruments

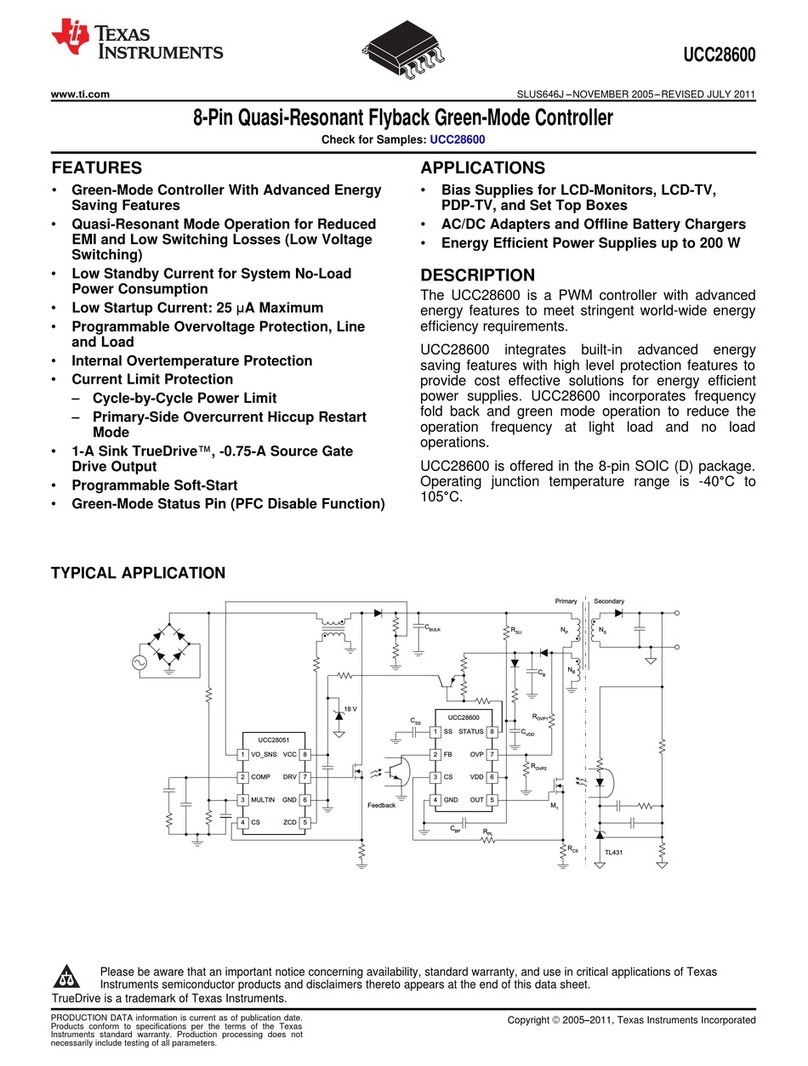

Texas Instruments UCC28600 User manual

Texas Instruments

Texas Instruments TMS320C6000 DSP User manual

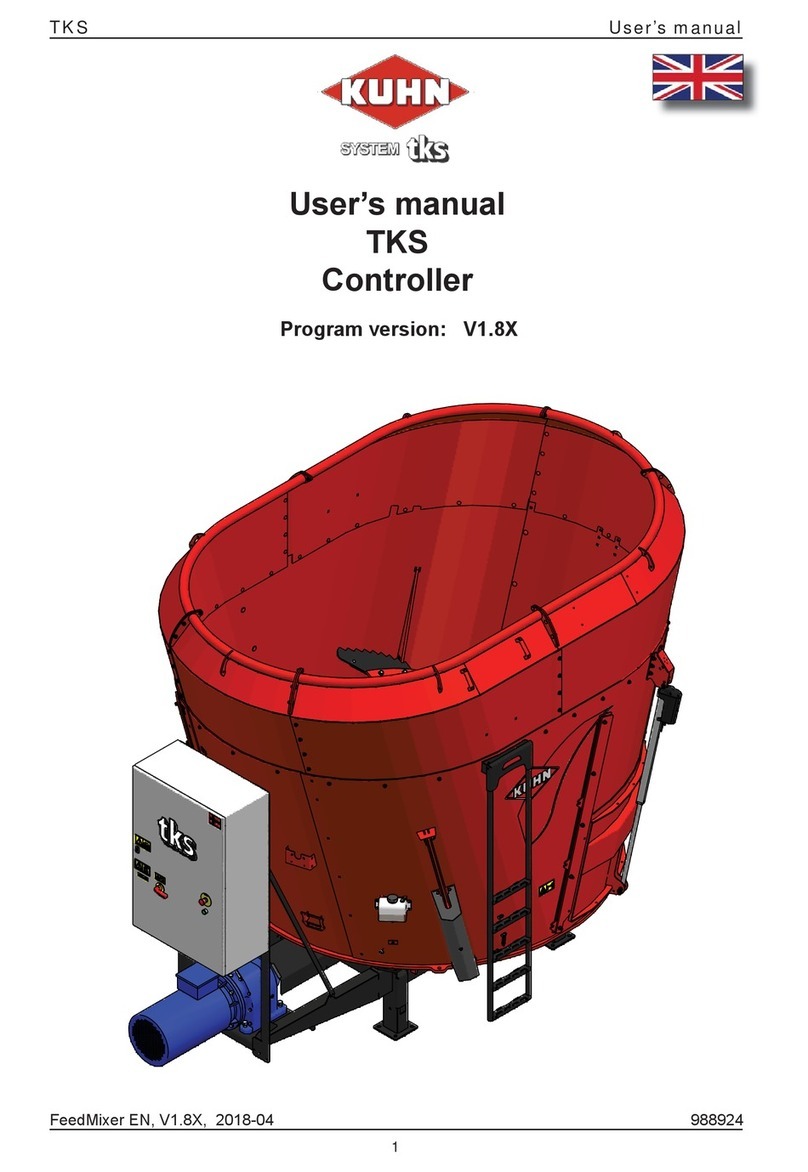

Popular Controllers manuals by other brands

Digiplex

Digiplex DGP-848 Programming guide

YASKAWA

YASKAWA SGM series user manual

Sinope

Sinope Calypso RM3500ZB installation guide

Isimet

Isimet DLA Series Style 2 Installation, Operations, Start-up and Maintenance Instructions

LSIS

LSIS sv-ip5a user manual

Airflow

Airflow Uno hab Installation and operating instructions