5

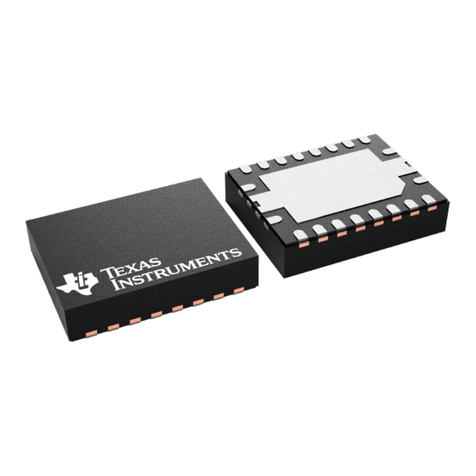

TPS65981

www.ti.com

SLVSDC2B –FEBRUARY 2016–REVISED AUGUST 2016

Product Folder Links: TPS65981

Submit Documentation FeedbackCopyright © 2016, Texas Instruments Incorporated

Pin Functions (continued)

PIN CATEGORY I/O TYPE POR STATE DESCRIPTION

NAME NO.

DEBUG_CTL1 45 Digital Core I/O

and Control Digital I/O Hi-Z General-purpose digital I/O 16. At power-up, pin state is sensed

to determine bit 4 of the I2C address.

DEBUG_CTL2 44 Digital Core I/O

and Control Digital I/O Hi-Z General-purpose digital I/O 17. At power-up, pin state is sensed

to determine bit 5 of the I2C address.

DEBUG1 2 Digital Core I/O

and Control Digital I/O Hi-Z General-purpose digital I/O 15. Ground pin with a 1-MΩresistor

when unused in the application.

GPIO0 41 Digital Core I/O

and Control Digital I/O Hi-Z General-purpose digital I/O 0. Float pin if it is configured as a

push-pull output in the application. Ground pin with a 1-MΩ

resistor when unused in the application.

GPIO2 25 Digital Core I/O

and Control Digital I/O Hi-Z General-purpose digital I/O 2. Float pin if it is configured as a

push-pull output in the application. Ground pin with a 1-MΩ

resistor when unused in the application.

GPIO3 19 Digital Core I/O

and Control Digital I/O Hi-Z General-purpose digital I/O 3. Float pin if it is configured as a

push-pull output in the application. Ground pin with a 1-MΩ

resistor when unused in the application.

GPIO4 26 Digital Core I/O

and Control Digital I/O Hi-Z

General-purpose digital I/O 4. Configured as a hot-plug detect

(HPD) transistor, HPD receiver, or both when DisplayPort mode is

supported. Ground pin with a 1-MΩresistor when unused in the

application.

GPIO5 23 Digital Core I/O

and Control Digital I/O Hi-Z

General-purpose digital I/O 5. Can be configured as a HPD

receiver when DisplayPort mode is supported. Must be tied high

or low through a 1-kΩpull-up or pull-down resistor when used as

a configuration input. Ground pin with a 1-MΩresistor when

unused in the application.

GPIO6 20 Digital Core I/O

and Control Digital I/O Hi-Z General-purpose digital I/O 6. Float pin if it is configured as a

push-pull output in the application. Ground pin with a 1-MΩ

resistor when unused in the application.

GPIO7 38 Digital Core I/O

and Control Digital I/O Hi-Z General-purpose digital I/O 7. Float pin if it is configured as a

push-pull output in the application. Ground pin with a 1-MΩ

resistor when unused in the application.

GPIO8 1 Digital Core I/O

and Control Digital I/O Hi-Z General-purpose digital I/O 8. Float pin if it is configured as a

push-pull output in the application. Ground pin with a 1-MΩ

resistor when unused in the application.

HV_GATE1 31 External HV FET

Control and Sense Analog Output Short to

SENSEP External NFET gate control for high voltage power path. Float pin

when unused.

HV_GATE2 32 External HV FET

Control and Sense Analog Output Short to

VBUS External NFET gate control for high voltage power path. Float pin

when unused.

I2C_IRQZ 43 Digital Core I/O

and Control Digital Output Hi-Z I2C port interrupt. Active low. Implement externally as an open-

drain with a pull-up resistance. Float pin when unused.

I2C_SCL 47 Digital Core I/O

and Control Digital I/O Digital Input I2C port serial clock. Open-drain output. Tie pin to LDO_3V3 or

VDDIO (depending on configuration) through a 10-kΩresistor

when used or unused.

I2C_SDA 46 Digital Core I/O

and Control Digital I/O Digital Input I2C port serial data. Open-drain output. Tie pin to LDO_3V3 or

VDDIO (depending on configuration) through a 10-kΩresistor

when used or unused.

LDO_1V8A 56 Low Current Power N/A Output of the 1.8-V LDO for core analog circuits. Bypass with

capacitance CLDO_1V8A to GND.

LDO_1V8D 40 Low Current Power N/A Output of the 1.8-V LDO for core digital circuits. Bypass with

capacitance CLDO_1V8D to GND.

LDO_3V3 51 Low Current Power N/A Output of the VBUS to 3.3-V LDO or connected to VIN_3V3 by a

switch. Main internal supply rail. Used to power external flash

memory. Bypass with capacitance CLDO_3V3 to GND.

LDO_BMC 48 Low Current Power N/A Output of the USB-PD BMC transceiver output level LDO. Bypass

with capacitance CLDO_BMC to GND.

MRESET 24 Digital Core I/O

and Control Digital I/O Hi-Z

General-purpose digital I/O 11. Forces RESETZ to assert. By

default, this pin asserts RESETZ when pulled high. The pin can

be programmed to assert RESETZ when pulled low. Ground pin

with a 1-MΩresistor when unused in the application.

PP_5V0 27 High Current Power N/A 5-V supply for VBUS. Bypass with capacitance CPP_5V0 to

GND. Tie pin to GND when unused

28

PP_CABLE 14 High Current Power N/A 5-V supply for C_CC pins. Bypass with capacitance CPP_CABLE

to GND when not tied to PP_5V0. Tie pin to PP_5V0 when

unused.