Product Preview WM8581

w PP Rev 1.0 March 2006

3

TABLE OF CONTENTS

DESCRIPTION ................................................................................................................................................................................. 1

FEATURES ...................................................................................................................................................................................... 1

APPLICATIONS ............................................................................................................................................................................... 1

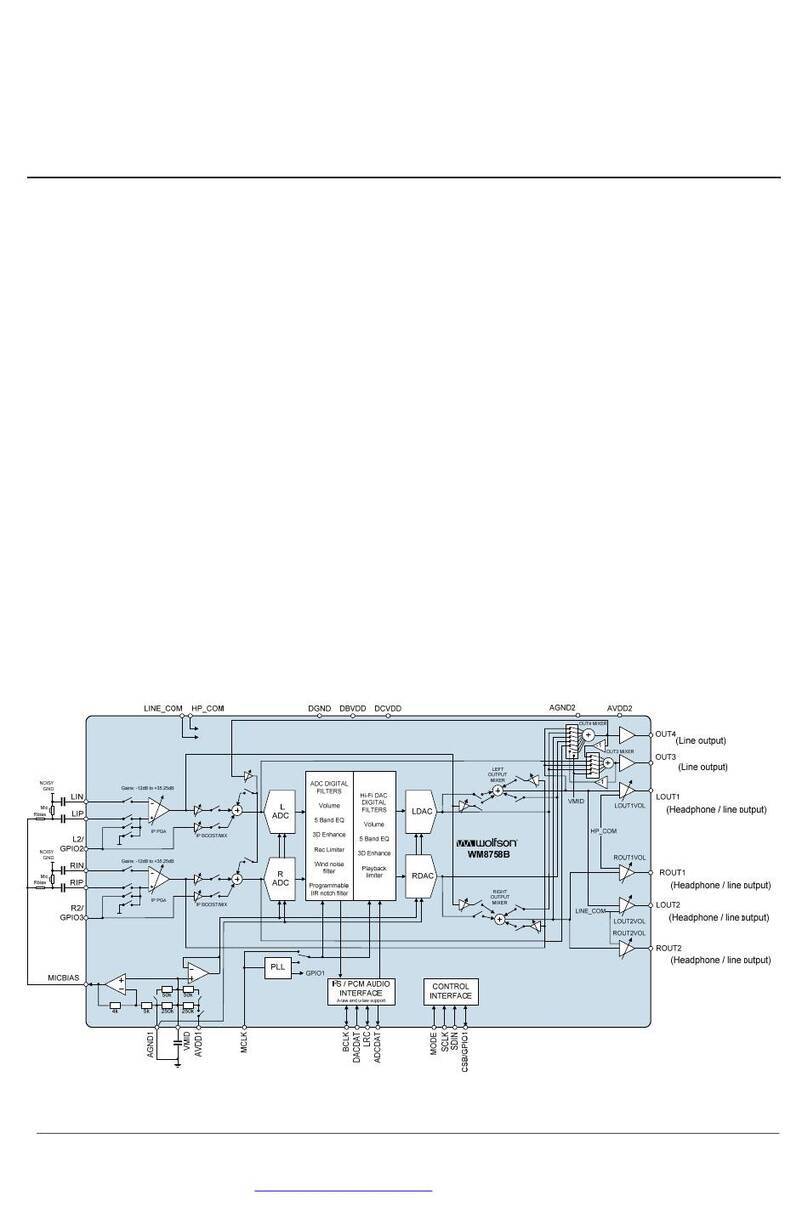

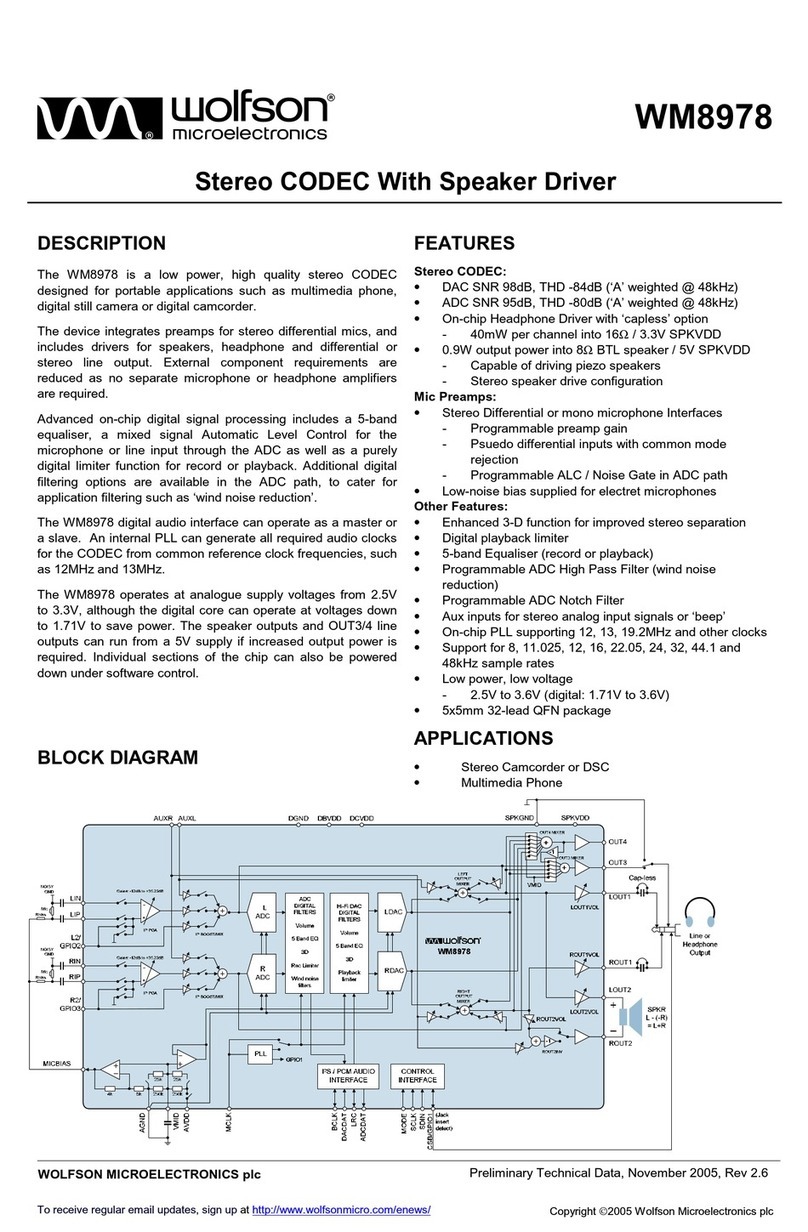

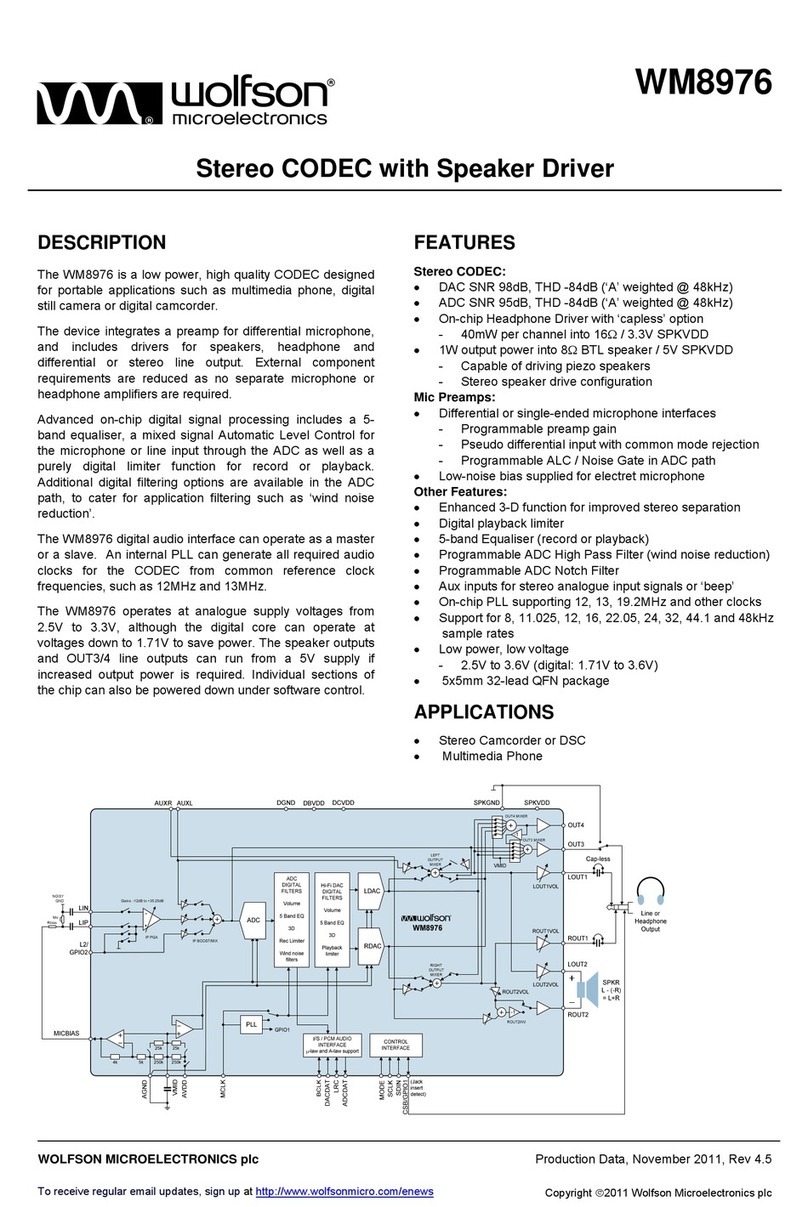

BLOCK DIAGRAM ........................................................................................................................................................................... 2

TABLE OF CONTENTS.................................................................................................................................................................... 3

PIN CONFIGURATION..................................................................................................................................................................... 4

ORDERING INFORMATION............................................................................................................................................................. 4

PIN DESCRIPTION .......................................................................................................................................................................... 5

MULTI-FUNCTION PINS.............................................................................................................................................................. 6

ABSOLUTE MAXIMUM RATINGS ................................................................................................................................................... 8

RECOMMENDED OPERATING CONDITIONS................................................................................................................................ 9

ELECTRICAL CHARACTERISTICS................................................................................................................................................. 9

TERMINOLOGY......................................................................................................................................................................... 12

MASTER CLOCK TIMING.......................................................................................................................................................... 12

DIGITAL AUDIO INTERFACE – MASTER MODE...................................................................................................................... 13

DIGITAL AUDIO INTERFACE – SLAVE MODE ......................................................................................................................... 14

CONTROL INTERFACE TIMING – 3-WIRE MODE ................................................................................................................... 15

CONTROL INTERFACE TIMING – 2-WIRE MODE ................................................................................................................... 15

DEVICE DESCRIPTION ................................................................................................................................................................. 17

INTRODUCTION........................................................................................................................................................................ 17

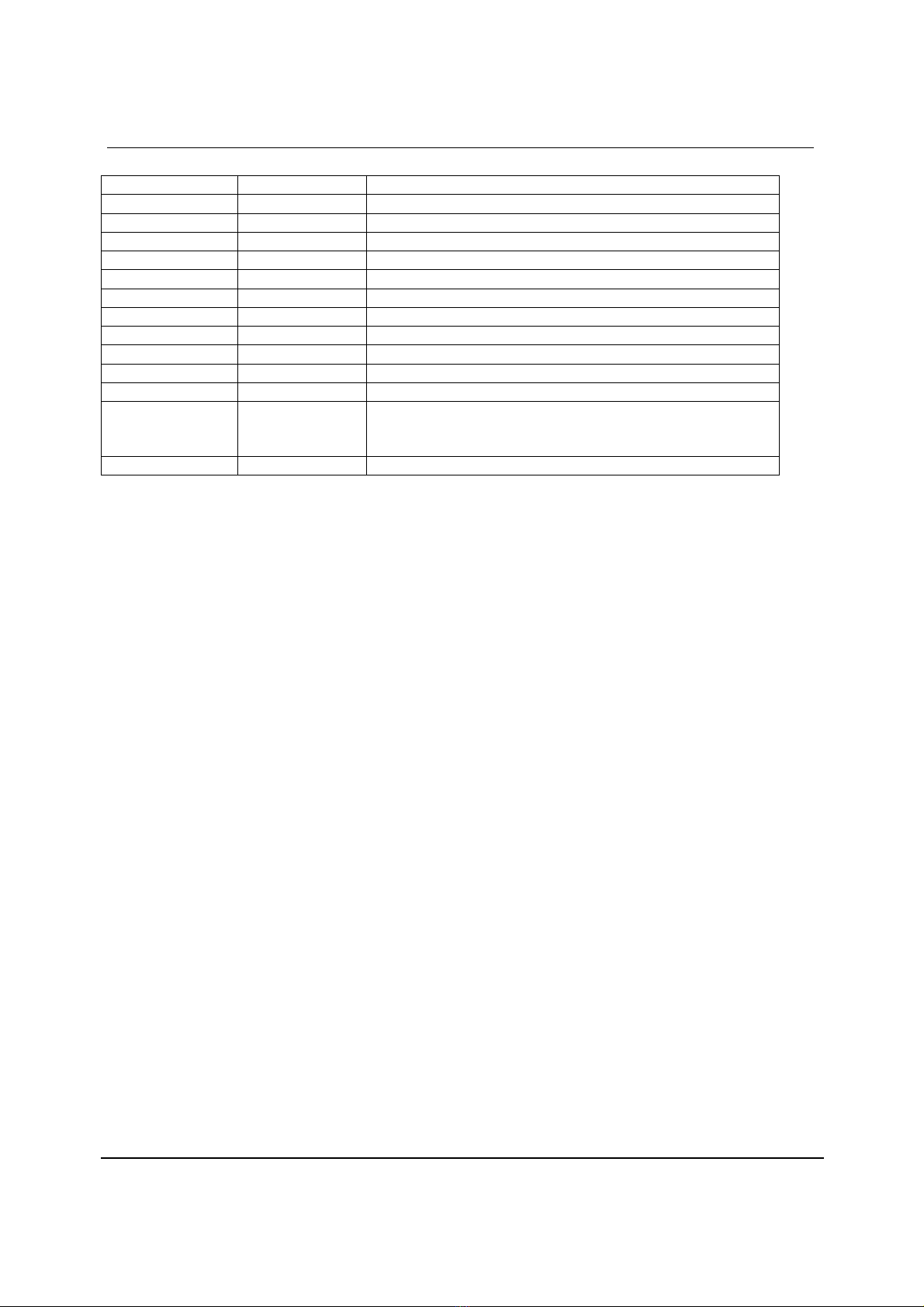

CONTROL INTERFACE OPERATION....................................................................................................................................... 18

DIGITAL AUDIO INTERFACES.................................................................................................................................................. 22

AUDIO DATA FORMATS ........................................................................................................................................................... 24

AUDIO INTERFACE CONTROL................................................................................................................................................. 27

DAC FEATURES........................................................................................................................................................................ 30

ADC FEATURES........................................................................................................................................................................ 37

DIGITAL ROUTING OPTIONS ................................................................................................................................................... 38

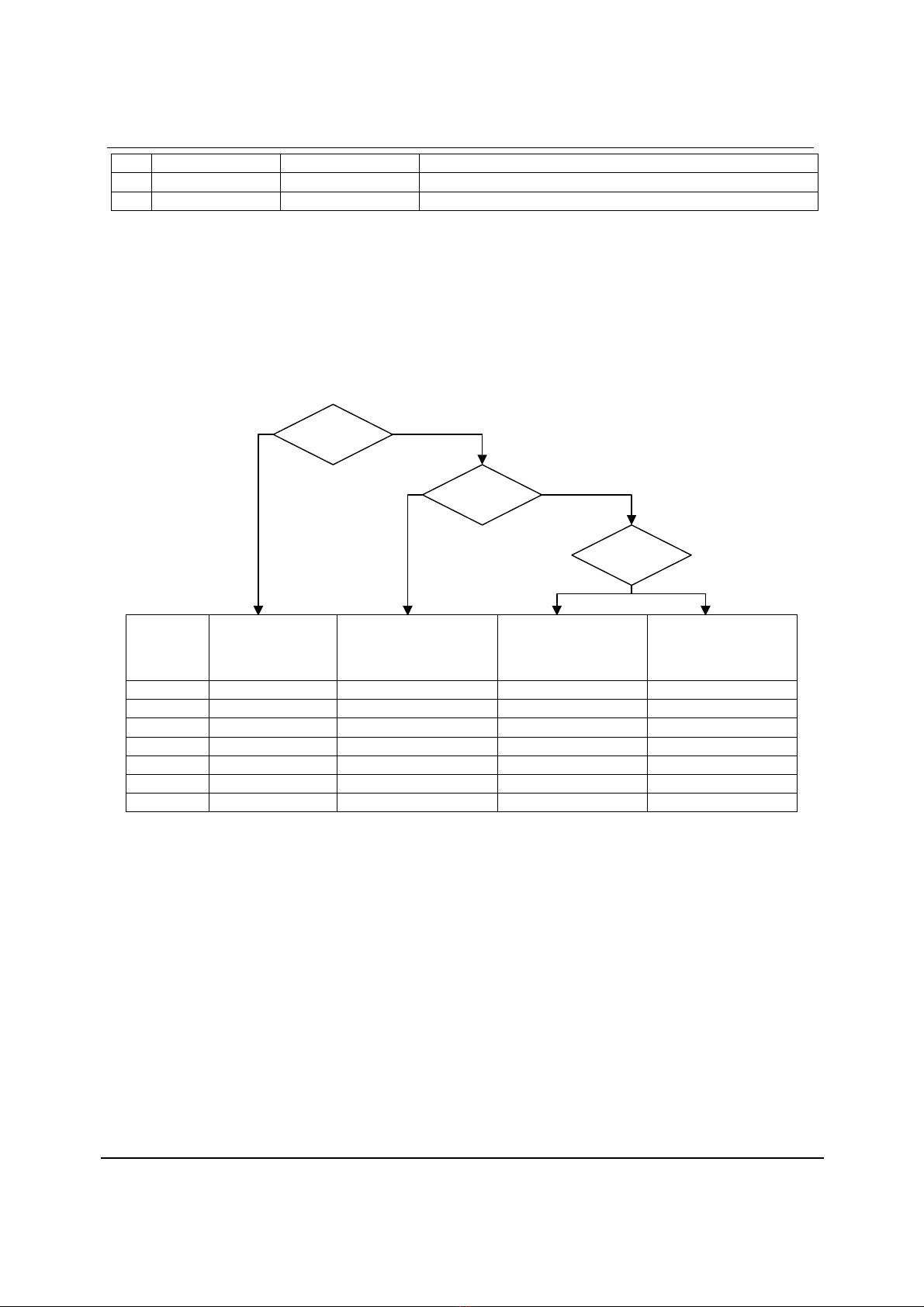

CLOCK SELECTION.................................................................................................................................................................. 40

PHASE-LOCKED LOOPS AND S/PDIF CLOCKING (SOFTWARE MODE)............................................................................... 46

PHASE-LOCKED LOOPS AND S/PDIF CLOCKING (HARDWARE MODE) .............................................................................. 53

S/PDIF TRANSCEIVER ............................................................................................................................................................. 54

S/PDIF TRANSMITTER ............................................................................................................................................................. 55

S/PDIF RECEIVER .................................................................................................................................................................... 58

POWERDOWN MODES ............................................................................................................................................................ 66

INTERNAL POWER ON RESET CIRCUIT................................................................................................................................. 67

HARDWARE CONTROL MODE ................................................................................................................................................ 70

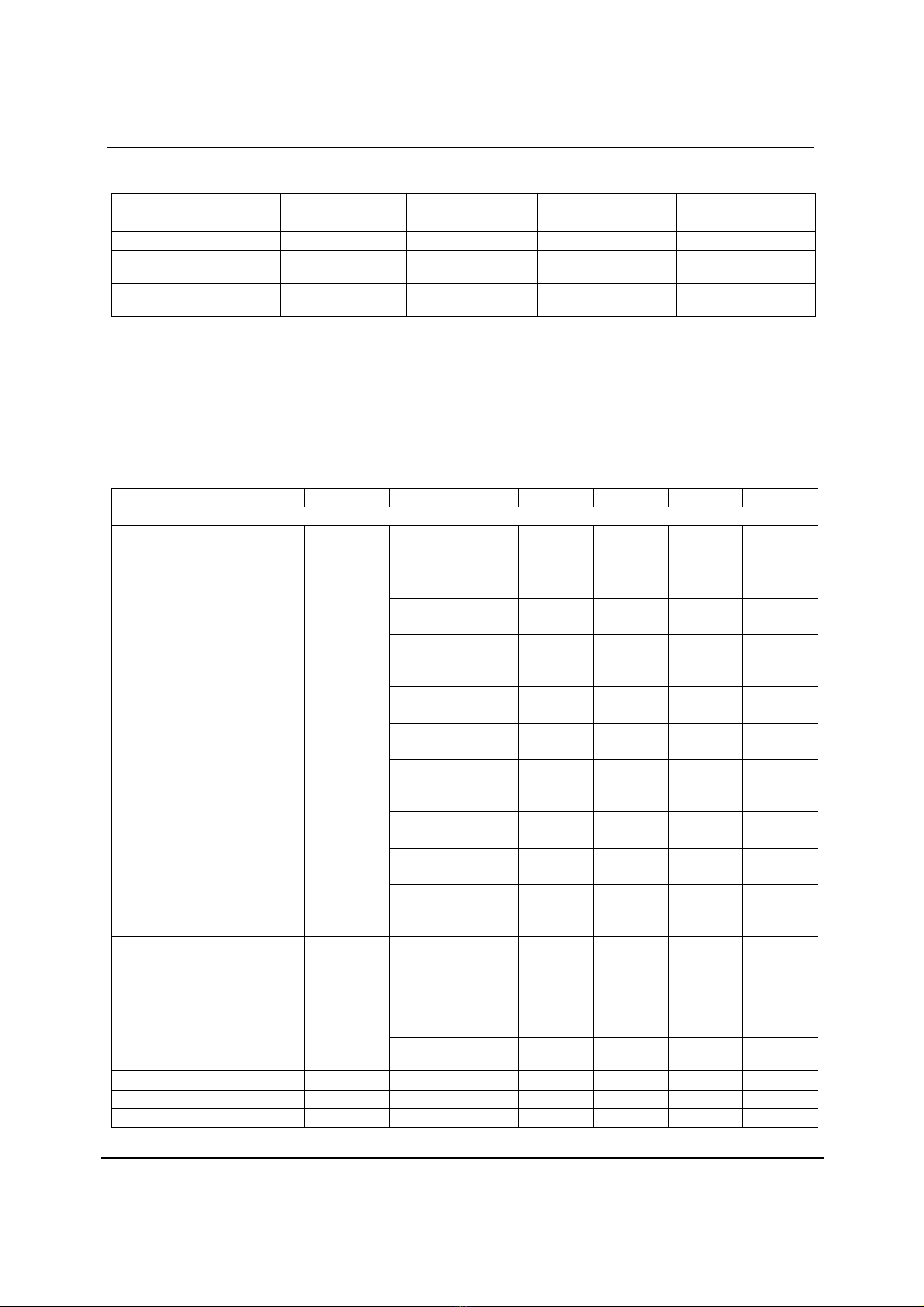

REGISTER MAP ........................................................................................................................................................................ 73

DIGITAL FILTER CHARACTERISTICS.......................................................................................................................................... 88

DAC FILTER RESPONSES ....................................................................................................................................................... 88

DIGITAL DE-EMPHASIS CHARACTERISTICS ......................................................................................................................... 89

ADC FILTER RESPONSES ....................................................................................................................................................... 90

ADC HIGH PASS FILTER .......................................................................................................................................................... 90

RECOMMENDED EXTERNAL COMPONENTS............................................................................................................................. 91

PACKAGE DIMENSIONS............................................................................................................................................................... 93

IMPORTANT NOTICE .................................................................................................................................................................... 94

ADDRESS:................................................................................................................................................................................. 94