Production Data WM8941

wPD, Rev 4.0, August 2008

3

TABLE OF CONTENTS

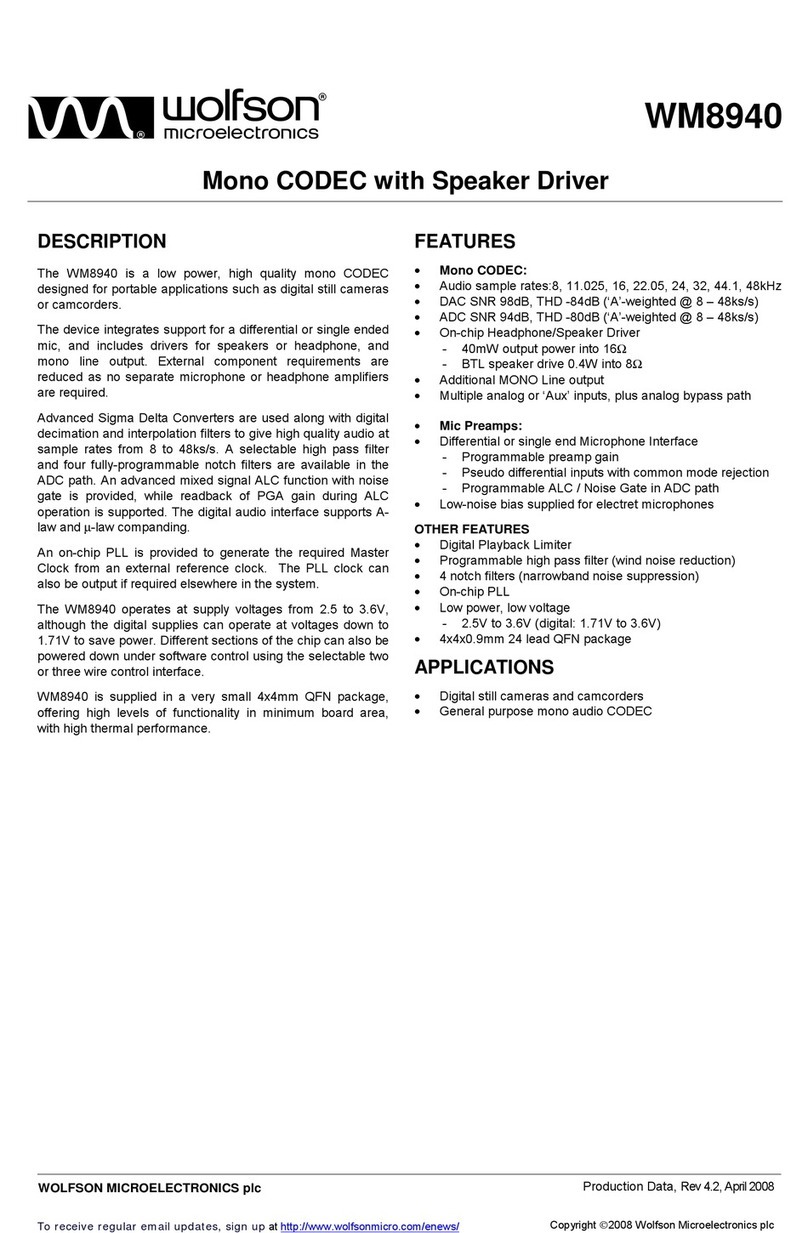

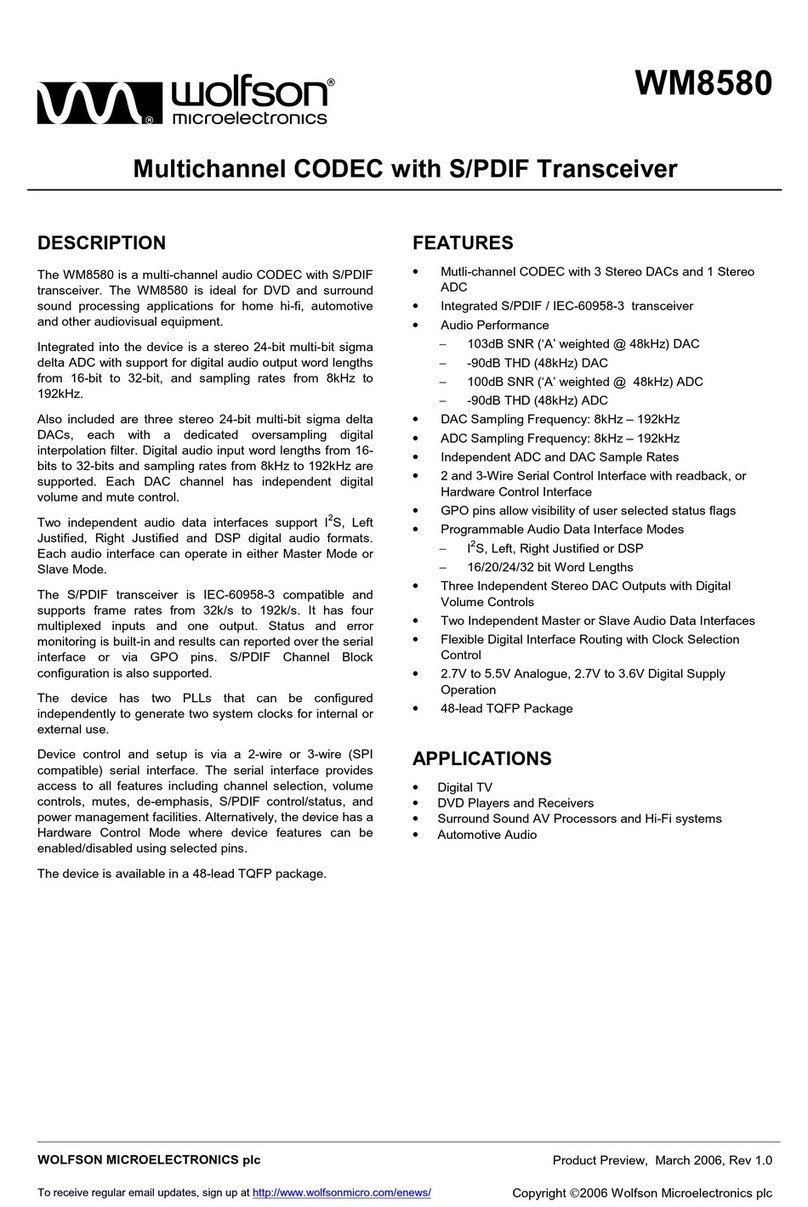

DESCRIPTION................................................................................................................ 1

FEATURES..................................................................................................................... 1

APPLICATIONS.............................................................................................................. 1

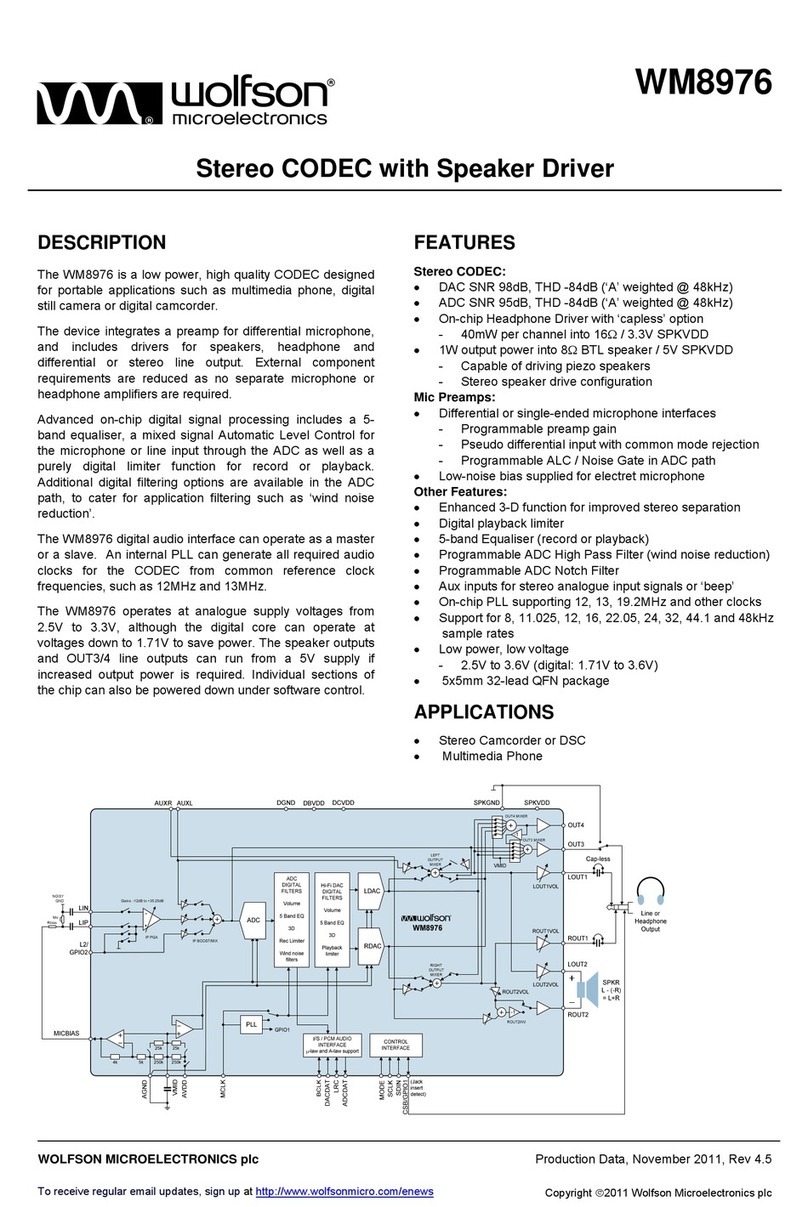

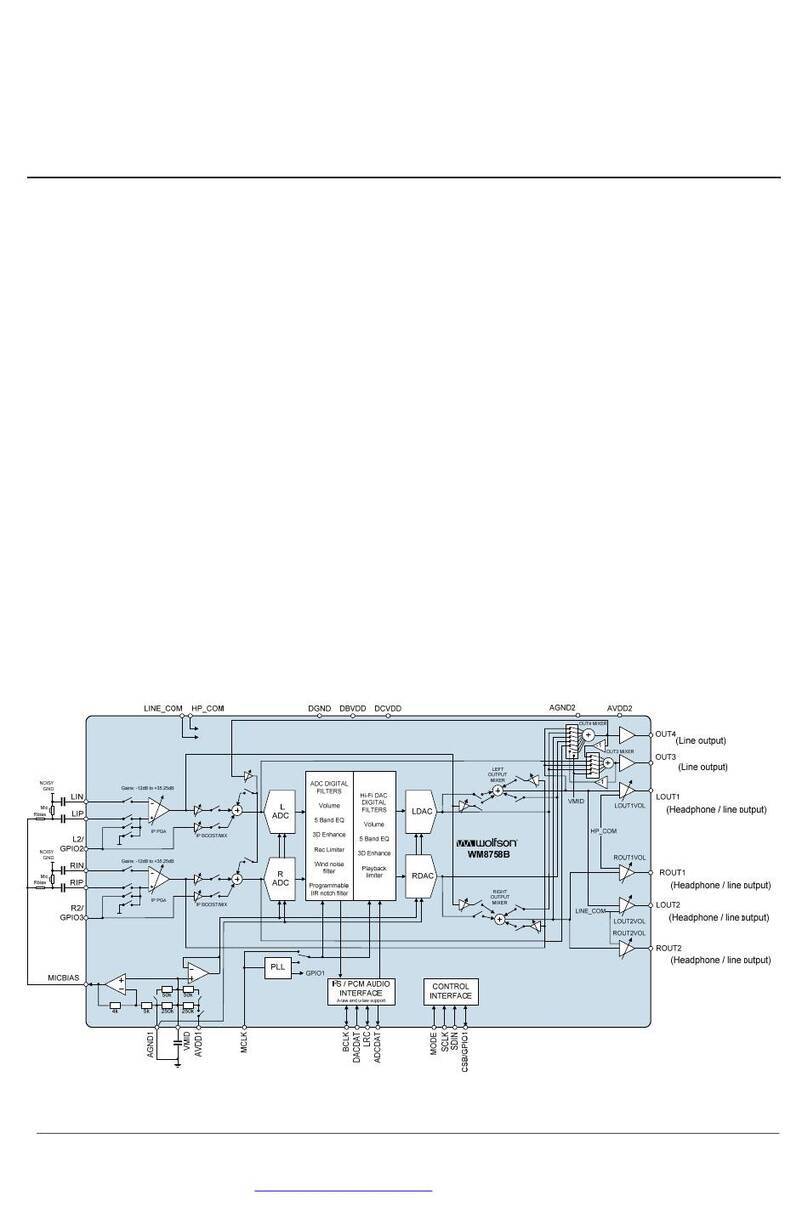

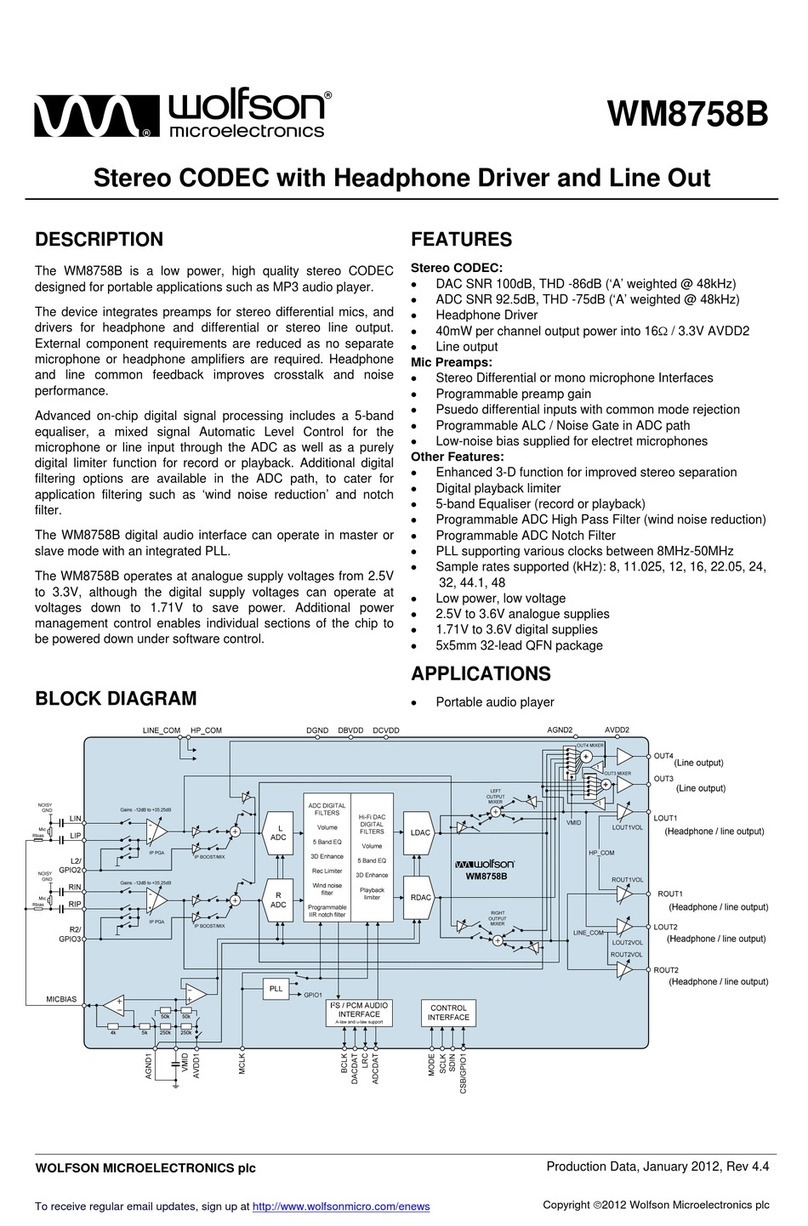

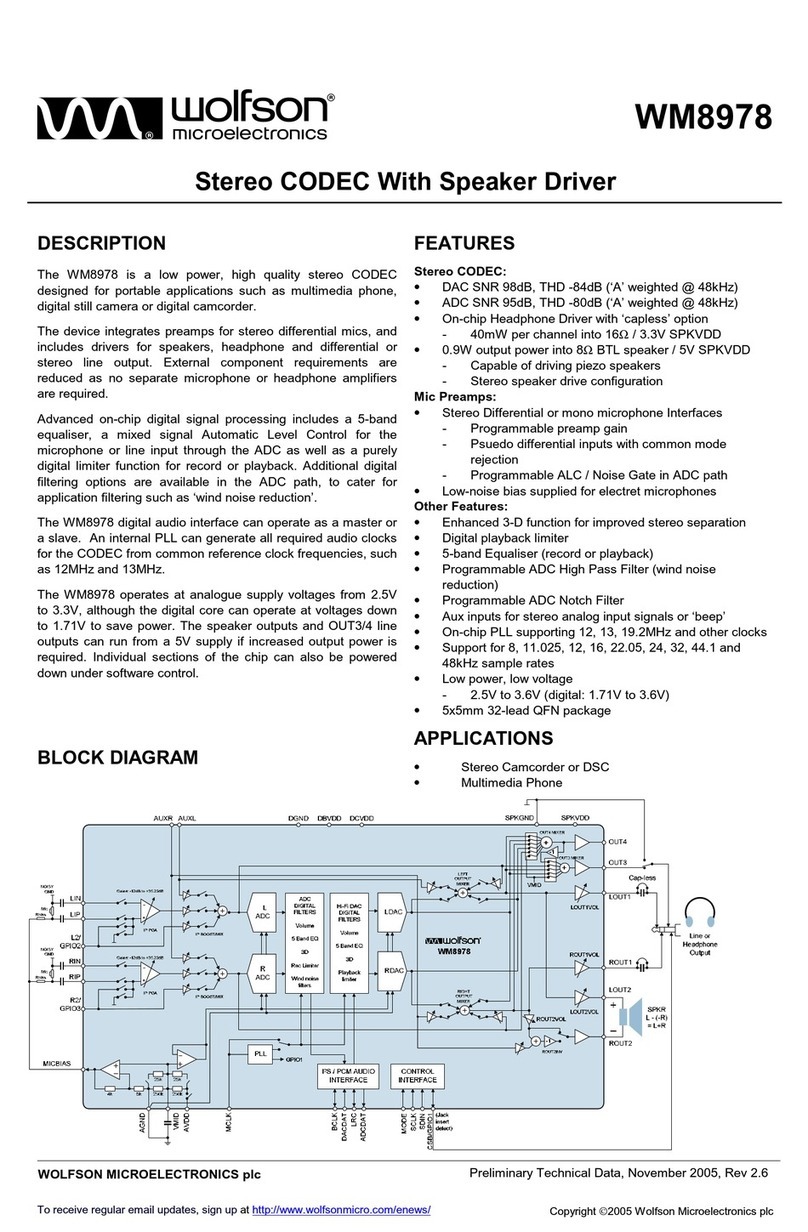

BLOCK DIAGRAM ......................................................................................................... 2

PIN CONFIGURATION ................................................................................................... 5

ORDERING INFORMATION........................................................................................... 5

PIN DESCRIPTION......................................................................................................... 6

ABSOLUTE MAXIMUM RATINGS ................................................................................. 7

RECOMMENDED OPERATING CONDITIONS.............................................................. 7

ELECTRICAL CHARACTERISTICS .............................................................................. 8

TERMINOLOGY ...................................................................................................................... 10

AUDIO PATHS OVERVIEW ......................................................................................... 11

SIGNAL TIMING REQUIREMENTS ............................................................................. 13

SYSTEM CLOCK TIMING .......................................................................................................13

AUDIO INTERFACE TIMING – MASTER MODE....................................................................13

AUDIO INTERFACE TIMING – SLAVE MODE .......................................................................14

CONTROL INTERFACE TIMING – 3-WIRE MODE................................................................15

CONTROL INTERFACE TIMING – 2-WIRE MODE................................................................16

DEVICE DESCRIPTION ............................................................................................... 17

INTRODUCTION ..................................................................................................................... 17

INPUT SIGNAL PATH .............................................................................................................18

ANALOGUE TO DIGITAL CONVERTER (ADC) .....................................................................24

INPUT LIMITER / AUTOMATIC LEVEL CONTROL (ALC)......................................................29

OUTPUT SIGNAL PATH .........................................................................................................42

VOLUME BOOST ....................................................................................................................44

ANALOGUE OUTPUTS...........................................................................................................46

OUTPUT SWITCH...................................................................................................................49

VIDEO BUFFER ......................................................................................................................52

DIGITAL AUDIO INTERFACES...............................................................................................57

AUDIO SAMPLE RATES.........................................................................................................61

MASTER CLOCK AND PHASE LOCKED LOOP (PLL) ..........................................................62

COMPANDING ........................................................................................................................65

GENERAL PURPOSE INPUT/OUTPUT..................................................................................67

CONTROL INTERFACE..........................................................................................................67

3-WIRE SERIAL CONTROL MODE ........................................................................................69

READBACK IN 3-WIRE MODE ...............................................................................................69

2-WIRE SERIAL CONTROL MODE ........................................................................................70

RESETTING THE CHIP ..........................................................................................................70

POWER SUPPLIES.................................................................................................................70

POWER MANAGEMENT ........................................................................................................73

POP MINIMISATION ...............................................................................................................74

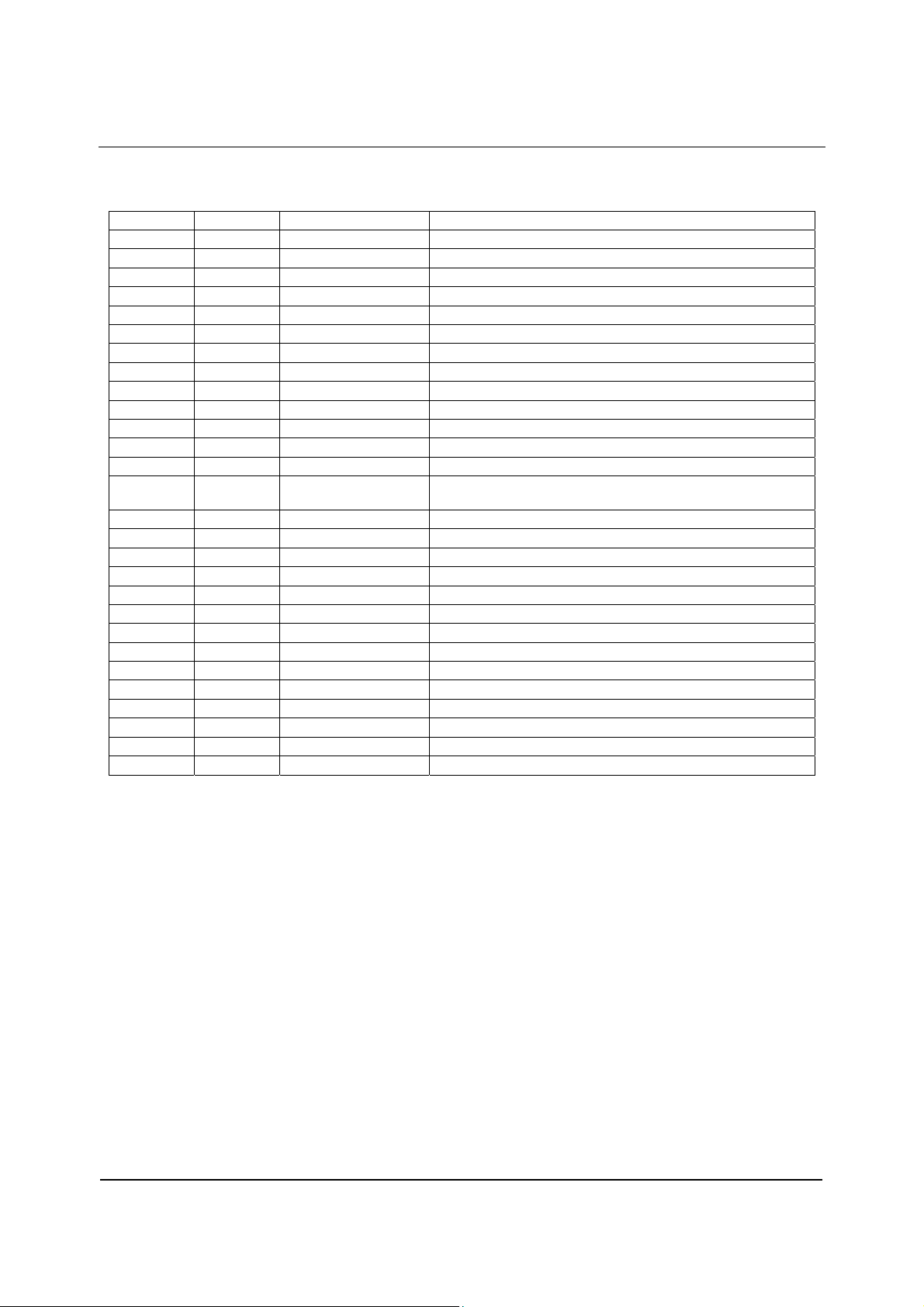

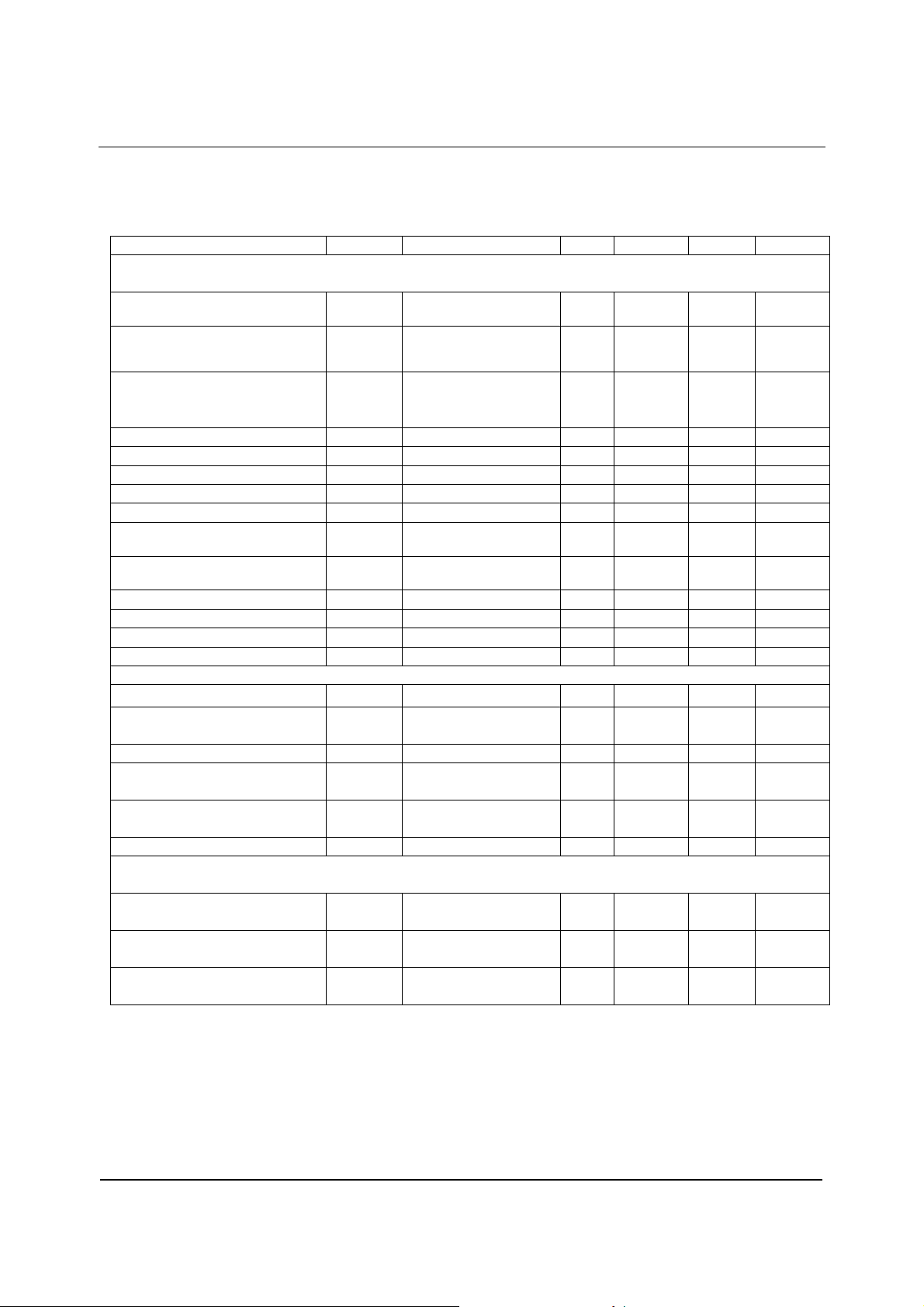

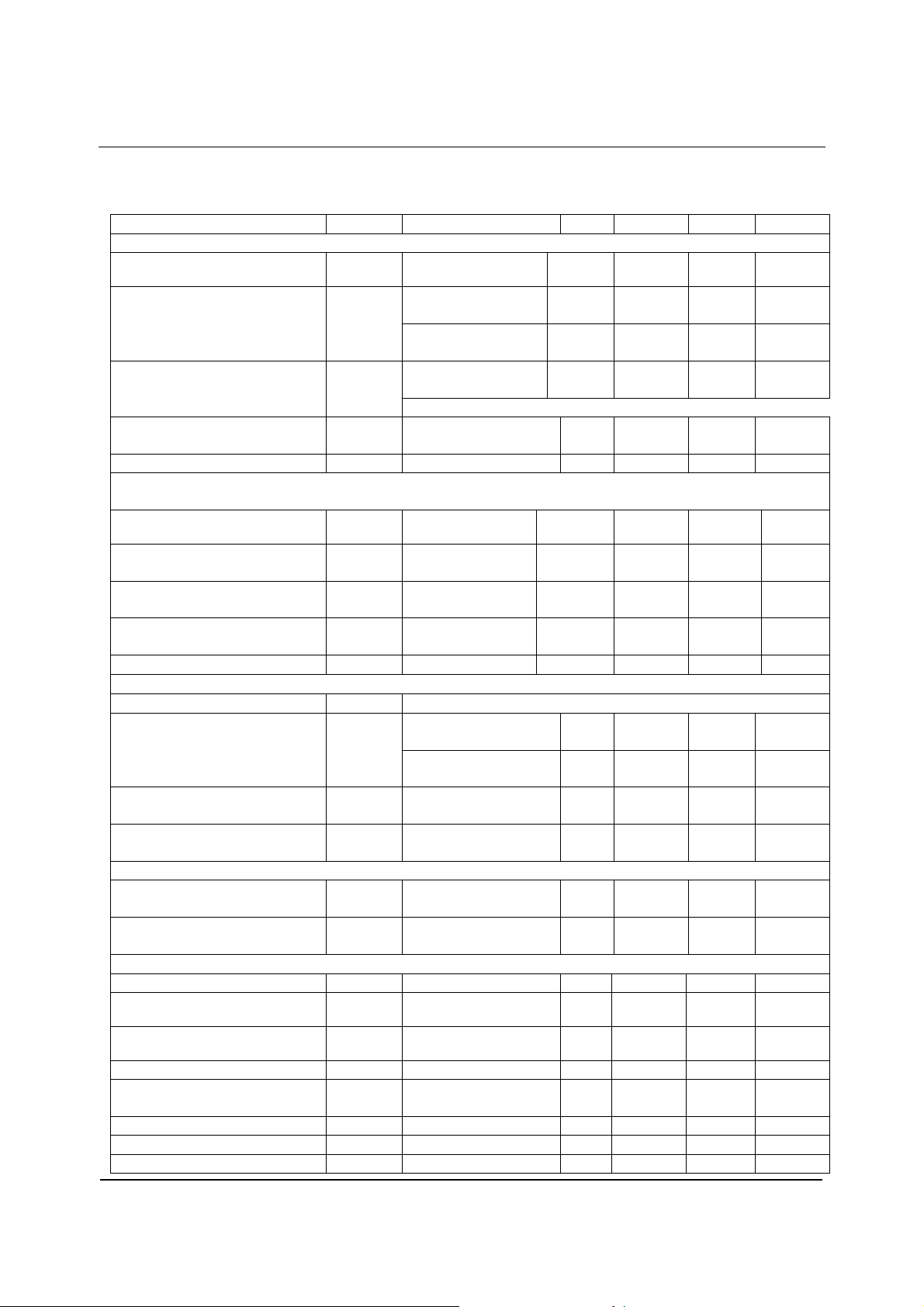

REGISTER MAP........................................................................................................... 75

REGISTER BITS BY ADDRESS .............................................................................................76

DIGITAL FILTER CHARACTERISTICS ....................................................................... 87

TERMINOLOGY ...................................................................................................................... 87

DAC FILTER RESPONSES ....................................................................................................88

ADC FILTER RESPONSES ....................................................................................................88

HIGHPASS FILTER.................................................................................................................89

NOTCH FILTERS AND LOW PASS FILTER...........................................................................90

APPLICATIONS INFORMATION ................................................................................. 92