WM8978 Production Data

w PD, Rev 4.5, October 2011

2

TABLE OF CONTENTS

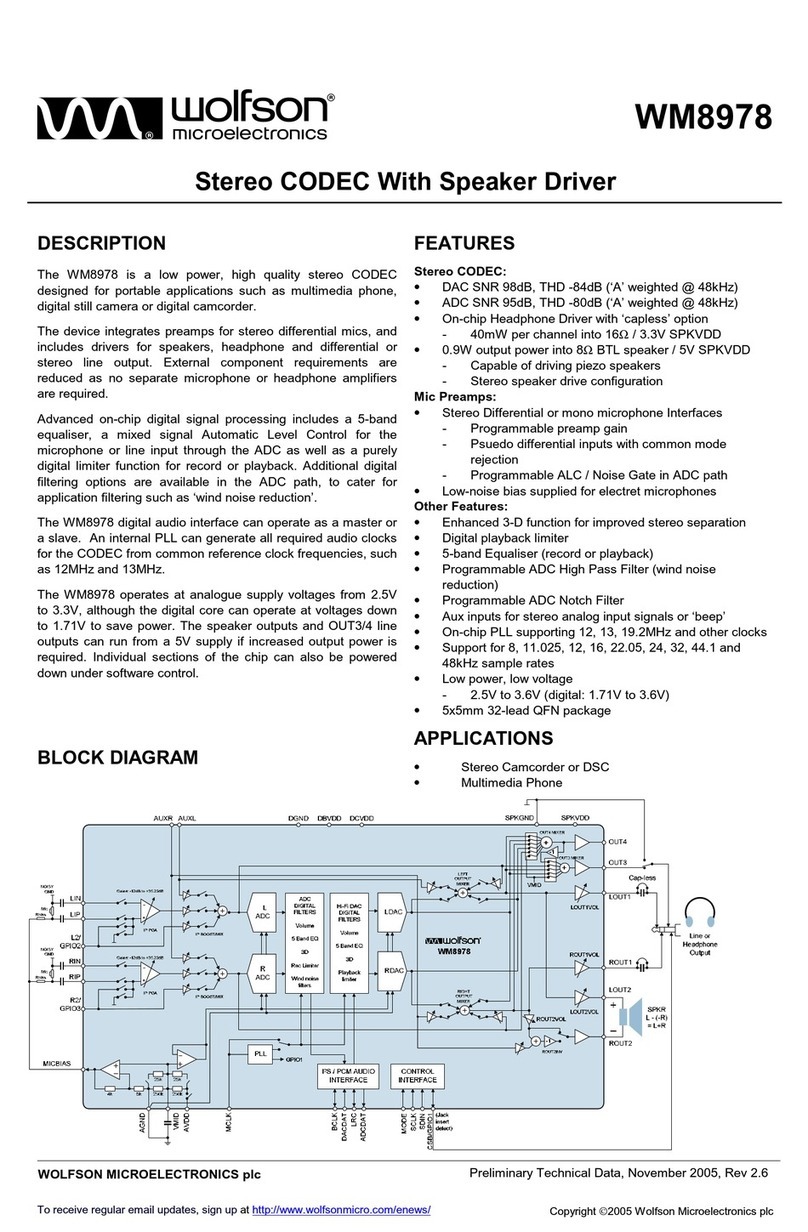

DESCRIPTION....................................................................................................... 1

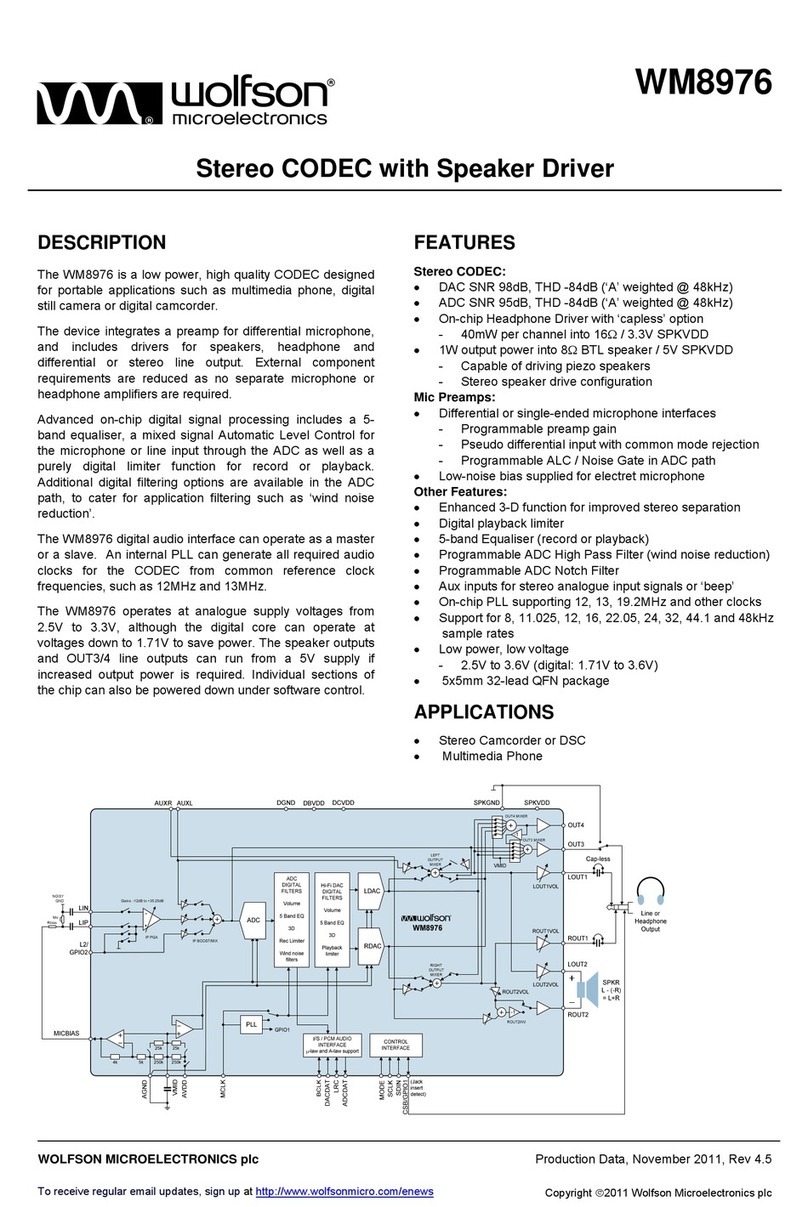

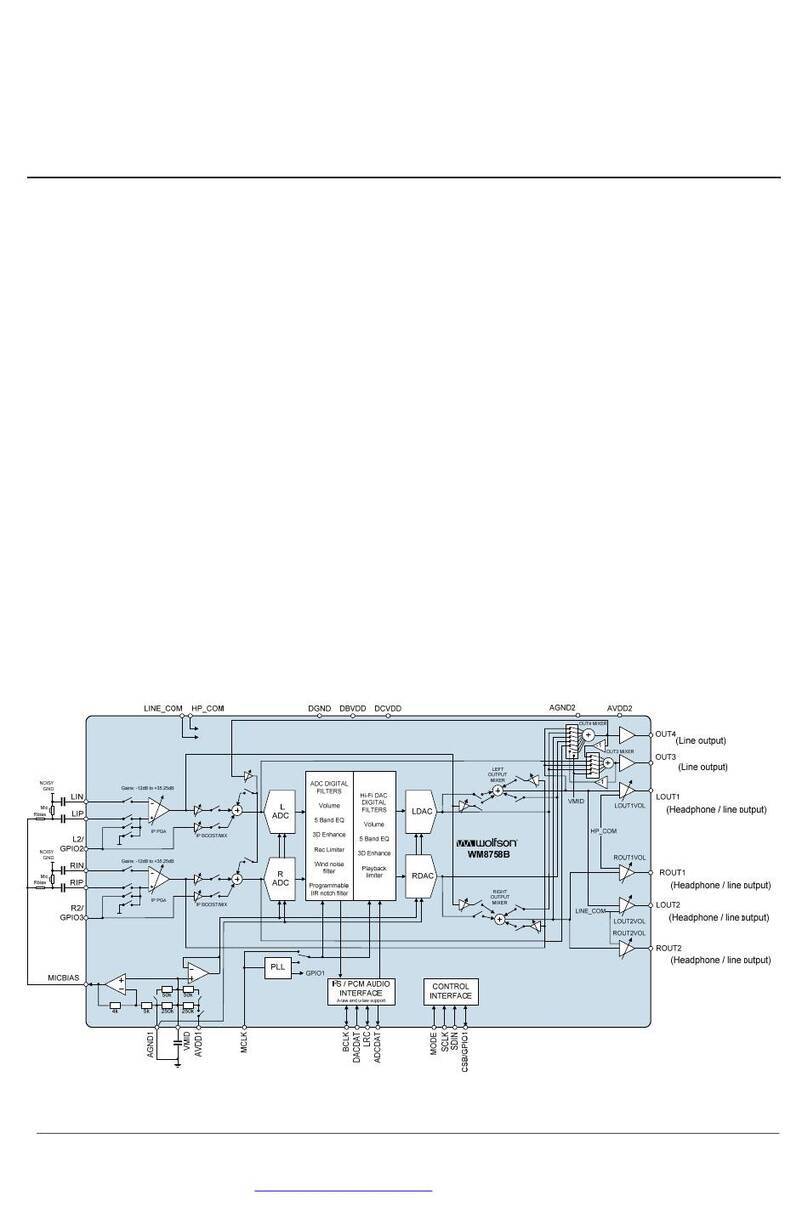

BLOCK DIAGRAM ................................................................................................ 1

FEATURES............................................................................................................ 1

APPLICATIONS..................................................................................................... 1

TABLE OF CONTENTS......................................................................................... 2

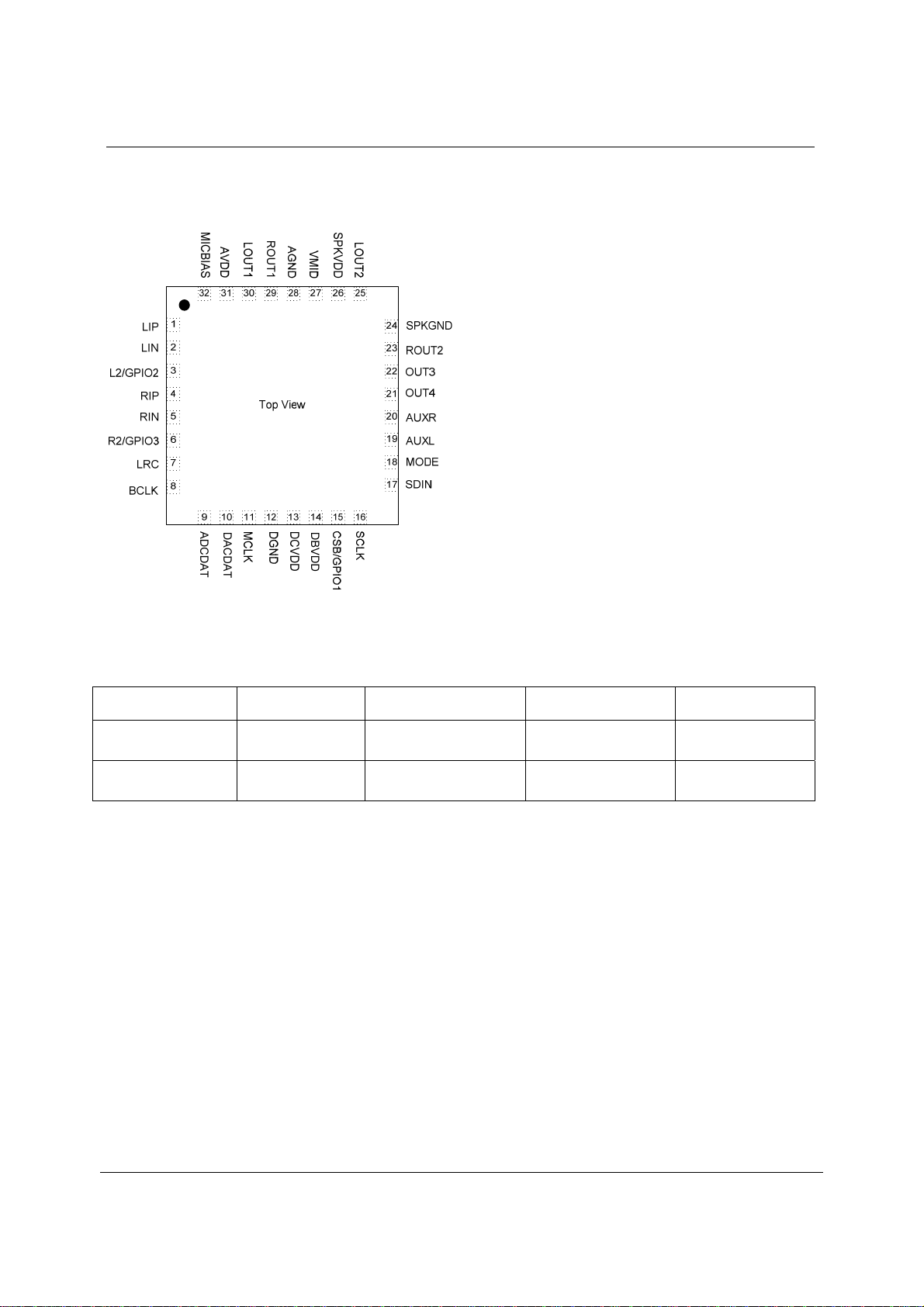

PIN CONFIGURATION.......................................................................................... 4

ORDERING INFORMATION.................................................................................. 4

PIN DESCRIPTION................................................................................................ 5

ABSOLUTE MAXIMUM RATINGS........................................................................ 6

RECOMMENDED OPERATING CONDITIONS..................................................... 6

ELECTRICAL CHARACTERISTICS ..................................................................... 7

TERMINOLOGY ............................................................................................................ 10

SPEAKER OUTPUT THD VERSUS POWER...................................................... 11

POWER CONSUMPTION.................................................................................... 12

AUDIO PATHS OVERVIEW ................................................................................ 14

SIGNAL TIMING REQUIREMENTS .................................................................... 15

SYSTEM CLOCK TIMING ............................................................................................. 15

AUDIO INTERFACE TIMING – MASTER MODE.......................................................... 15

AUDIO INTERFACE TIMING – SLAVE MODE ............................................................. 16

CONTROL INTERFACE TIMING – 3-WIRE MODE ...................................................... 17

CONTROL INTERFACE TIMING – 2-WIRE MODE ...................................................... 18

INTERNAL POWER ON RESET CIRCUIT.......................................................... 19

DEVICE DESCRIPTION ...................................................................................... 21

INTRODUCTION ........................................................................................................... 21

INPUT SIGNAL PATH ................................................................................................... 23

ANALOGUE TO DIGITAL CONVERTER (ADC) ........................................................... 30

INPUT LIMITER / AUTOMATIC LEVEL CONTROL (ALC)............................................ 36

OUTPUT SIGNAL PATH ............................................................................................... 47

3D STEREO ENHANCEMENT...................................................................................... 54

ANALOGUE OUTPUTS................................................................................................. 54

DIGITAL AUDIO INTERFACES..................................................................................... 70

AUDIO SAMPLE RATES............................................................................................... 75

MASTER CLOCK AND PHASE LOCKED LOOP (PLL) ................................................ 75

LOOPBACK ................................................................................................................... 77

COMPANDING .............................................................................................................. 77

GENERAL PURPOSE INPUT/OUTPUT........................................................................ 79

OUTPUT SWITCHING (JACK DETECT)....................................................................... 80

CONTROL INTERFACE................................................................................................ 82

RESETTING THE CHIP ................................................................................................ 83

POWER SUPPLIES....................................................................................................... 83

RECOMMENDED POWER UP/DOWN SEQUENCE.................................................... 83

POWER MANAGEMENT .............................................................................................. 88

REGISTER MAP.................................................................................................. 89

REGISTER BITS BY ADDRESS ................................................................................... 91

DIGITAL FILTER CHARACTERISTICS ............................................................ 108

TERMINOLOGY .......................................................................................................... 108

DAC FILTER RESPONSES ........................................................................................ 109

ADC FILTER RESPONSES ........................................................................................ 109

HIGHPASS FILTER..................................................................................................... 110