WM8978 Preliminary Technical Data

w PTD Rev 2.6 November 2005

2

TABLE OF CONTENTS

DESCRIPTION .......................................................................................................1

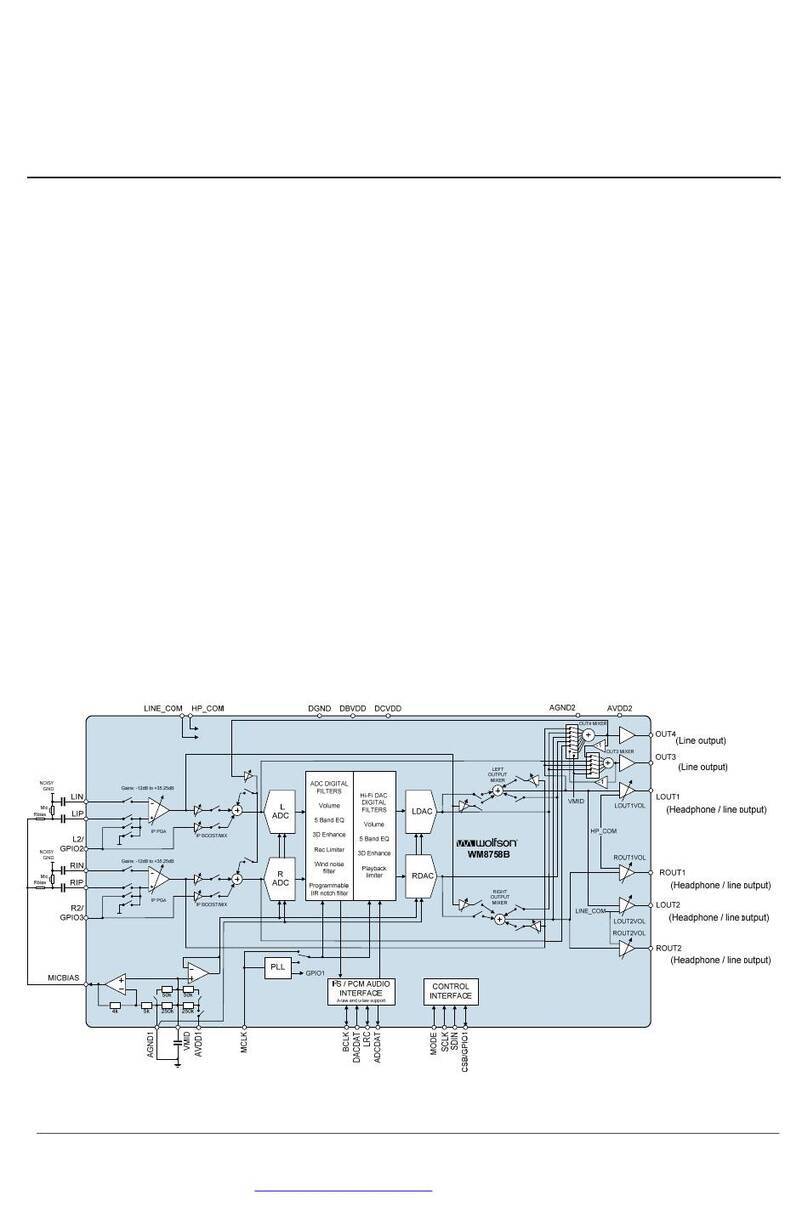

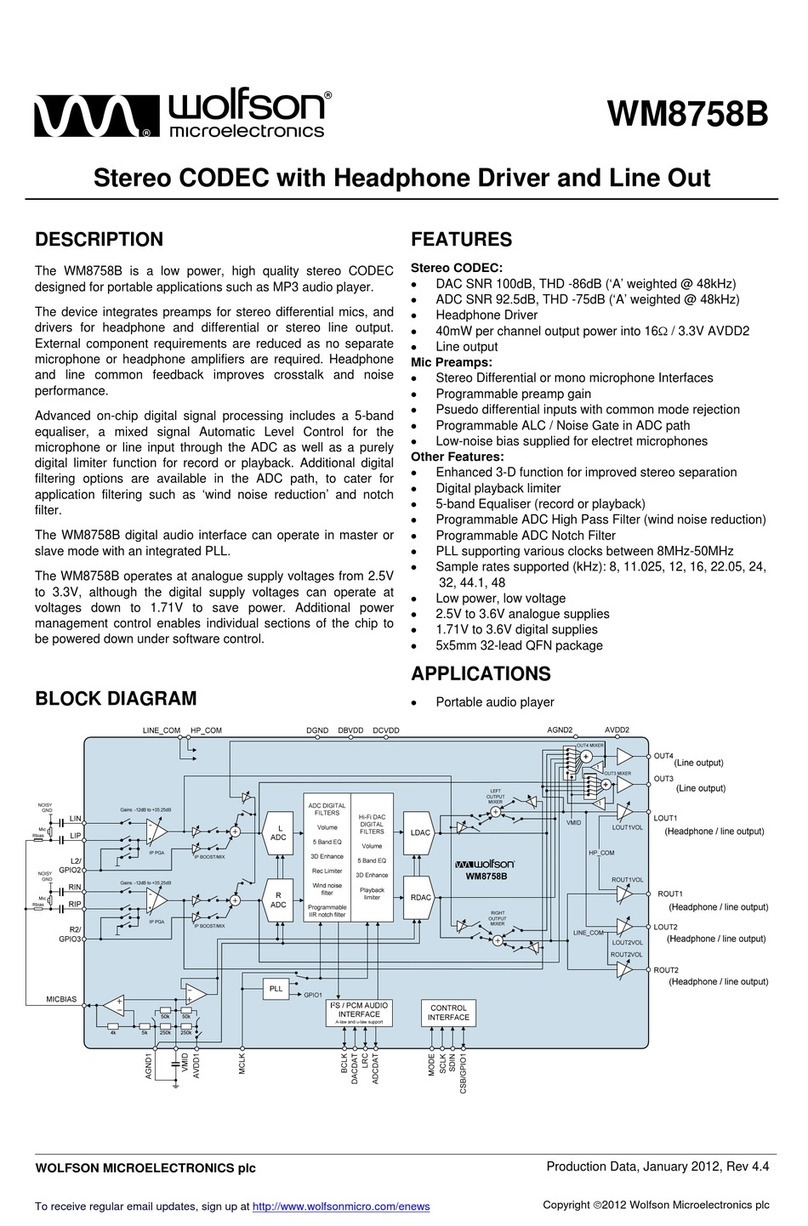

BLOCK DIAGRAM .................................................................................................1

FEATURES.............................................................................................................1

APPLICATIONS .....................................................................................................1

TABLE OF CONTENTS .........................................................................................2

PIN CONFIGURATION...........................................................................................4

ORDERING INFORMATION ..................................................................................4

PIN DESCRIPTION ................................................................................................5

RECOMMENDED OPERATING CONDITIONS .....................................................6

ELECTRICAL CHARACTERISTICS ......................................................................7

TERMINOLOGY .......................................................................................................... 10

SPEAKER OUTPUT THD VERSUS POWER ......................................................11

AUDIO PATHS OVERVIEW .................................................................................14

SIGNAL TIMING REQUIREMENTS .....................................................................15

SYSTEM CLOCK TIMING ........................................................................................... 15

AUDIO INTERFACE TIMING – MASTER MODE ........................................................ 15

AUDIO INTERFACE TIMING – SLAVE MODE............................................................ 16

CONTROL INTERFACE TIMING – 3-WIRE MODE .................................................... 17

CONTROL INTERFACE TIMING – 2-WIRE MODE .................................................... 18

INTERNAL POWER ON RESET CIRCUIT ..........................................................19

RECOMMENDED POWER UP/DOWN SEQUENCE .................................................. 21

DEVICE DESCRIPTION.......................................................................................25

INTRODUCTION......................................................................................................... 25

INPUT SIGNAL PATH ................................................................................................. 27

ANALOGUE TO DIGITAL CONVERTER (ADC).......................................................... 34

INPUT LIMITER / AUTOMATIC LEVEL CONTROL (ALC) .......................................... 38

OUTPUT SIGNAL PATH ............................................................................................. 42

3D STEREO ENHANCEMENT.................................................................................... 49

ANALOGUE OUTPUTS............................................................................................... 49

DIGITAL AUDIO INTERFACES................................................................................... 65

AUDIO SAMPLE RATES............................................................................................. 72

MASTER CLOCK AND PHASE LOCKED LOOP (PLL)............................................... 72

GENERAL PURPOSE INPUT/OUTPUT...................................................................... 74

OUTPUT SWITCHING (JACK DETECT)..................................................................... 75

CONTROL INTERFACE.............................................................................................. 77

RESETTING THE CHIP .............................................................................................. 78

POWER SUPPLIES .................................................................................................... 78

POWER MANAGEMENT ............................................................................................ 79

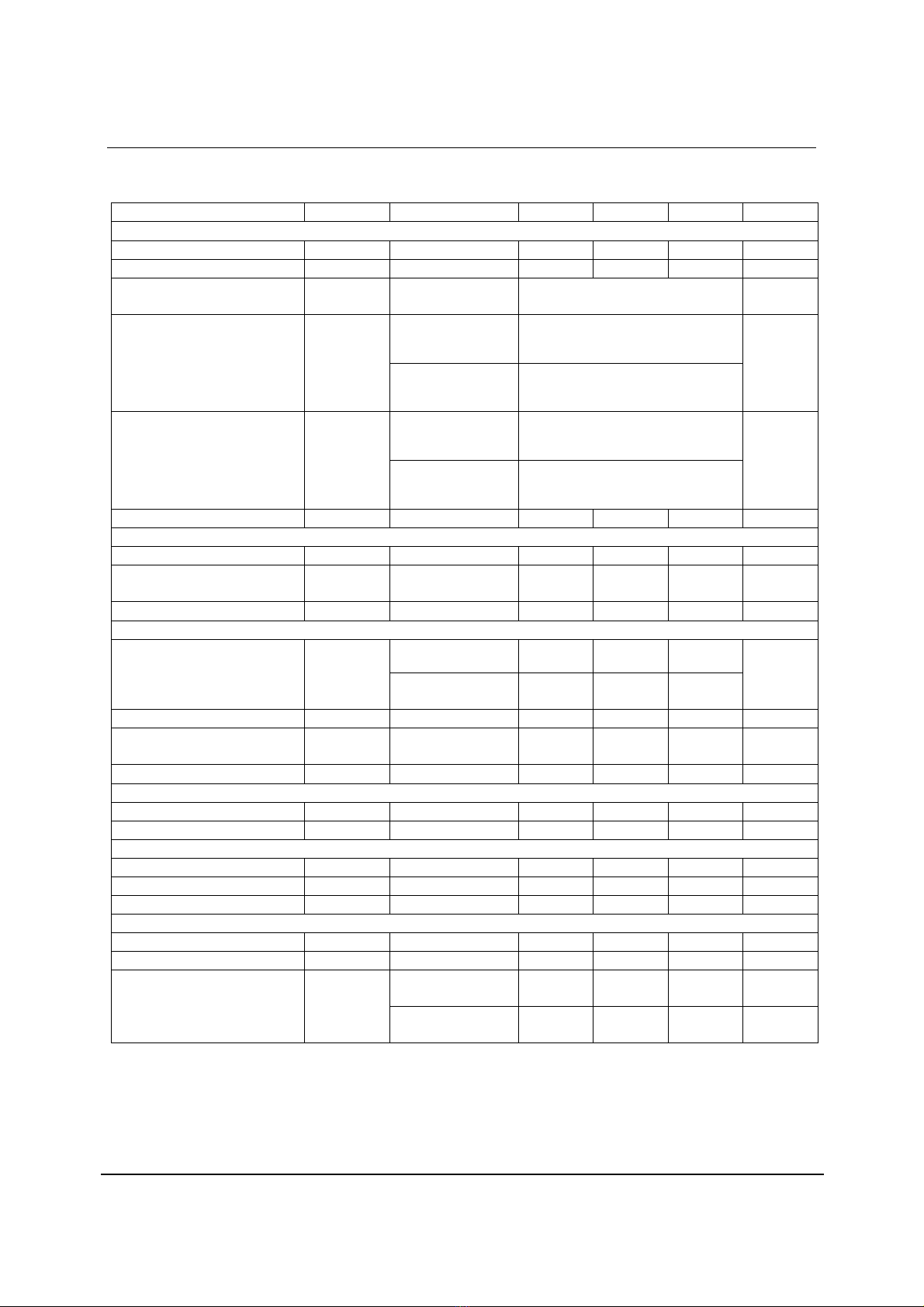

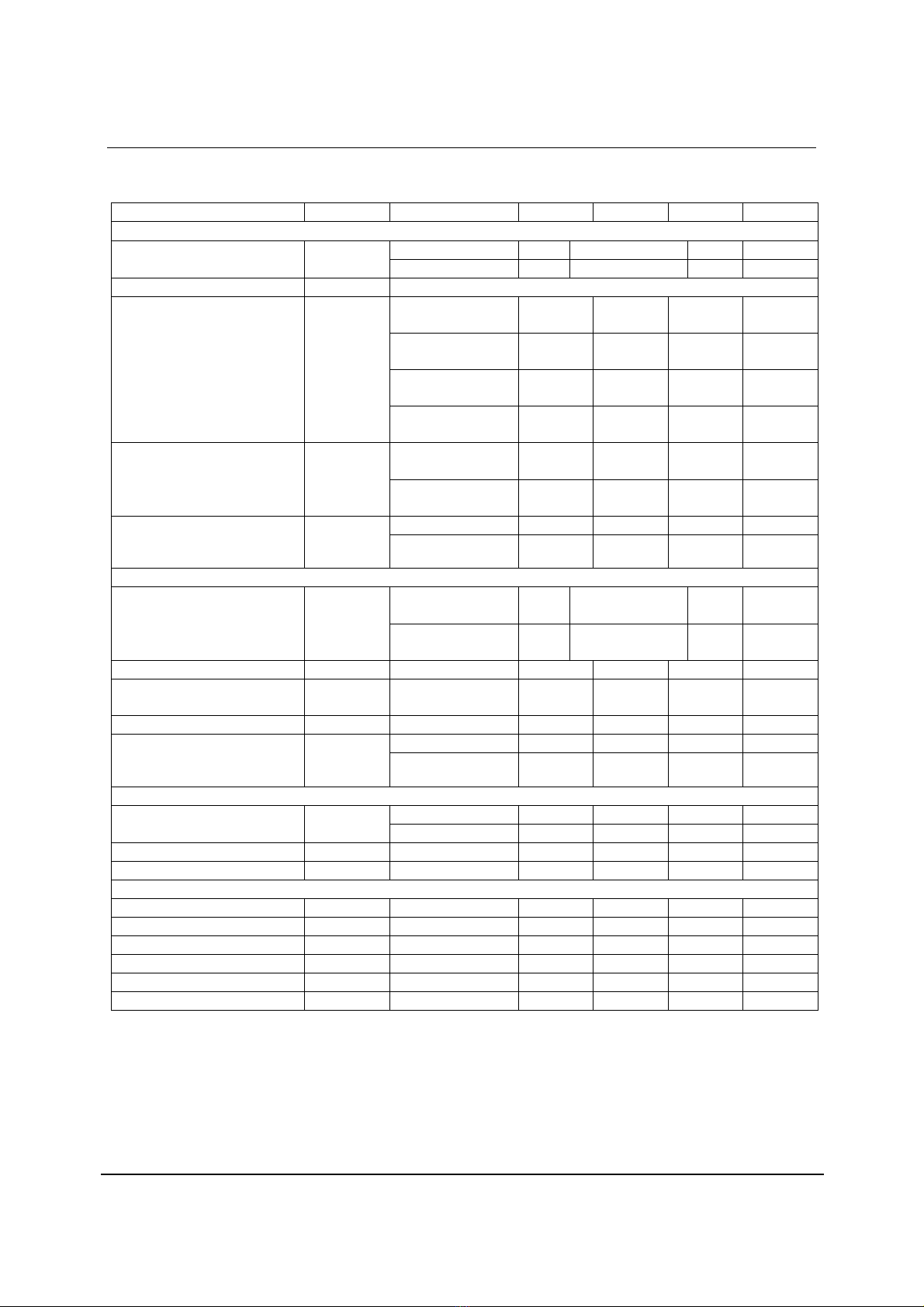

REGISTER MAP...................................................................................................80

REGISTER BITS BY ADDRESS ................................................................................. 82

DIGITAL FILTER CHARACTERISTICS ...............................................................99

TERMINOLOGY .......................................................................................................... 99

DAC FILTER RESPONSES....................................................................................... 100

ADC FILTER RESPONSES....................................................................................... 100

HIGHPASS FILTER................................................................................................... 101

5-BAND EQUALISER ................................................................................................ 102