vi

Figures

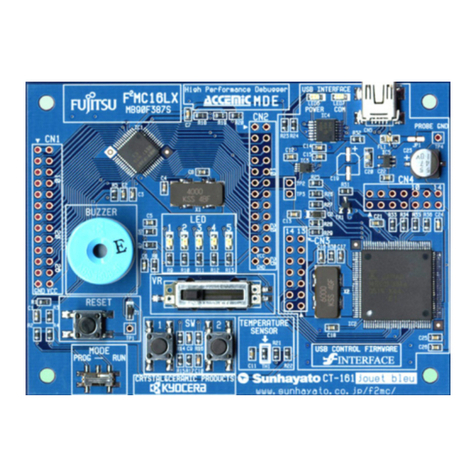

Fig. 1.1 MB89140 series 1-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 1.2 Block Diagram 1-7. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 1.3 Pin Assignment (DIP-64P-M01, MDP-64C-P02) 1-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 1.4 Pin Assignment (FPT-64P-M06, MDP-64C-P01) 1-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 1.5 Input/Output Circuit Configurations 1-14. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.1 Memory Space of MB89140 Series of Microcontrollers 2-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.2 Arrangement of 16-bit Data in Memory 2-5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.3 Arrangement of 16-bit Data during Execution of Instruction 2-5. . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.4 Structure of Processor Status 2-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.5 Rule for Translating Real Addresses at General-purpose Register Area 2-7. . . . . . . . . . . . . . . . .

Fig. 2.6 Register Bank Configuration 2-8. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.7 Memory Map in Various Modes 2-9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.8 Machine Clock Control Block Diagram 2-11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.9 Interrupt Controller Block Diagram 2-22. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.10 Interrupt-processing Flowchart 2-24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.11 Ports 00 to 07 and 10 to 13 2-28. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.12 Ports 14 to 16 2-29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.13 Ports 20 to 23 2-29. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.14 Ports 70 and 71 2-30. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.15 Ports 35 to 32, 30 and 17 2-31. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.16 Port 31 2-32. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.17 Ports 40 to 47, 50 to 57 and 60 to 67 2-33. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.18 BZ 2-33. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.19 Watch Prescaler Block Diagram 2-34. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.20 Watchdog Timer Reset Block Diagram 2-36. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.21 Time-base Timer Block Diagram 2-41. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.22 8-bit PWM Timer (Timer 1) Block Diagram 2-43. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.23 Timer Operation 2-46. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.24 PWM Pulse Output 2-47. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.25 8/16-bit Timer Block Diagram 2-48. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.26 Description Diagram for Internal Clock Mode Operation 2-52. . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.27 Flow Diagram for Timer Setting 2-52. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.28 External Cock Mode Operation Description Diagram 2-53. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.29 Operation Diagram when Timer Stop Bit is Used 2-53. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.30 MPG Block Diagram 2-56. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.31 Transition of DTTI Input 2-59. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.32 Outline of PWM Output 2-63. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.33 Description of PWM Output Operation 2-63. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.34 Flowchart of PWM Operation 2-64. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.35 Outline of MPG Output 2-67. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.36 Description of PPG Output Operation 2-67. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.37 Flowchart of PPG Operation 2-68. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.38 8-bit Serial I/O Block Diagram 2-70. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.39 Shift Start/Stop Timing 2-74. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.40 Input/Output Shift Timing 2-75. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.41 A/D Comverter Block Diagram 2-76. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.42 Buzzer Output Circuit Block Diagram 2-83. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 2.43 External Interrupt Circuit Block Diagram 2-85. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 3.1 Clock Pulse Generator 3-3. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 3.2 Outline of Reset Operation 3-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 3.3 Reset Vector Structure 3-4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Fig. 3.4 Interrupt-processing Flowchart 3-6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .