2 | | EPC – EFFICIENT POWER CONVERSION CORPORATION | WWW.EPC-CO.COM | COPYRIGHT 2018

QUICK START GUIDE EPC9084

DESCRIPTION

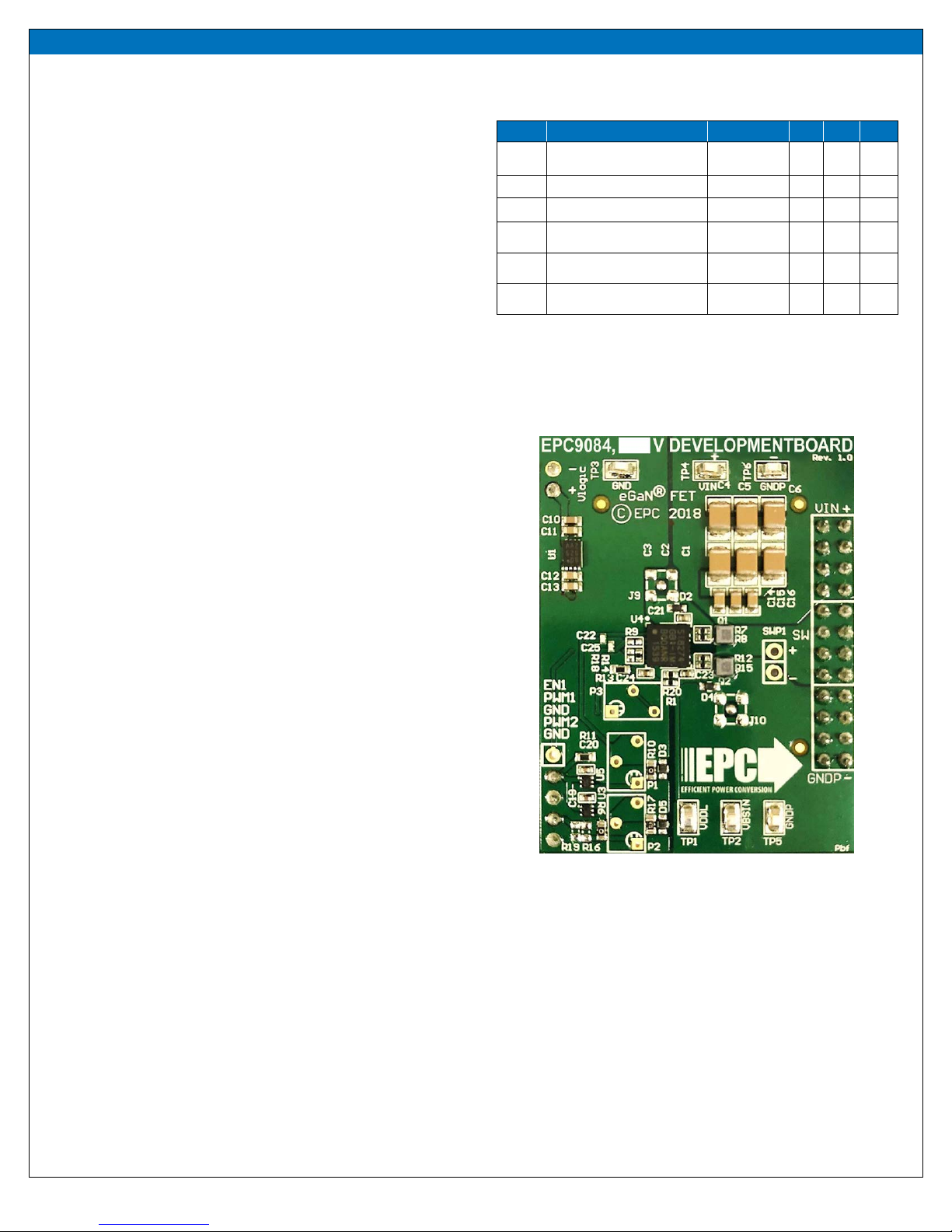

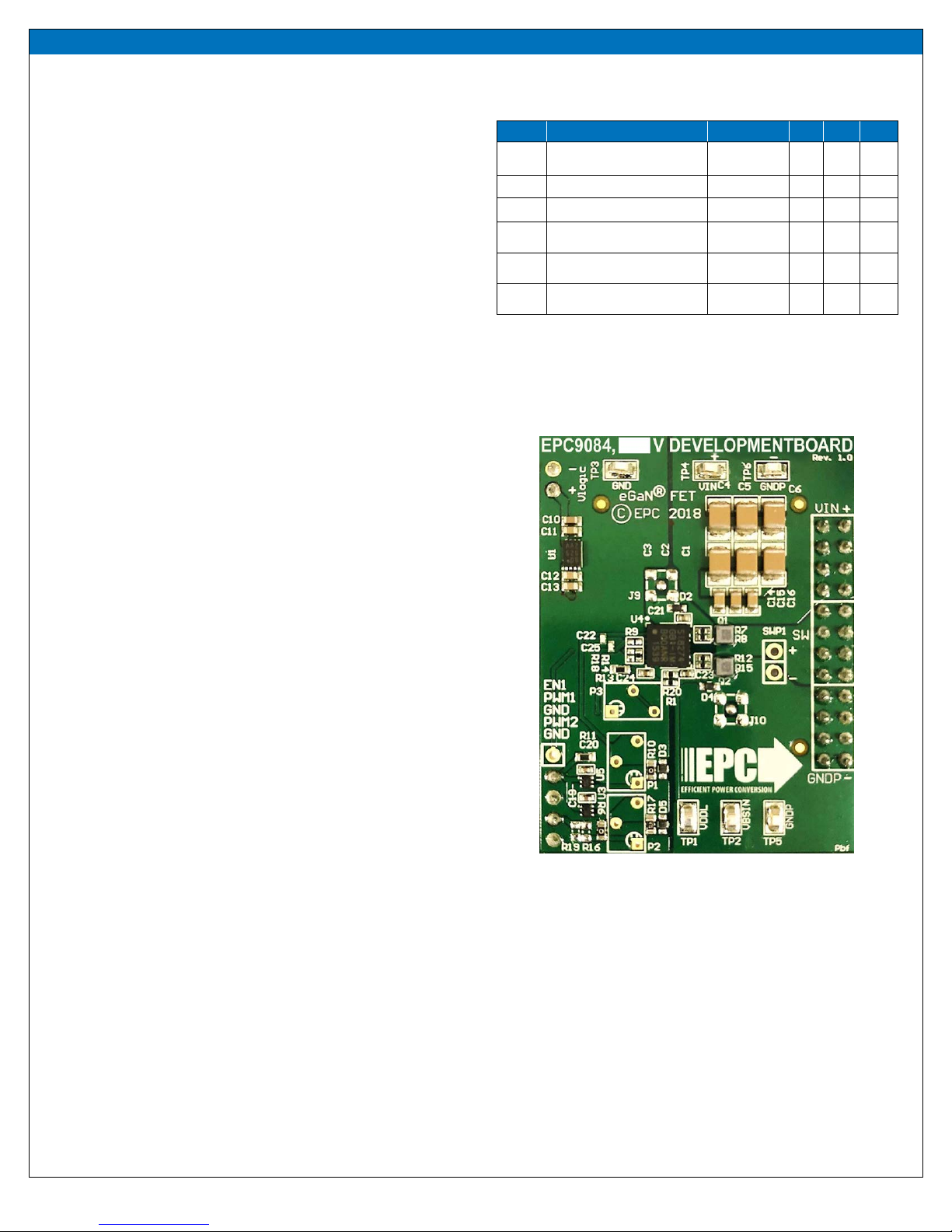

The EPC9084 development board, gure 1, is a 350 V maximum device

voltage, 4 A maximum output current, half bridge with onboard gate

drives, featuring two EPC2050 enhancement mode (eGaN®) eld eect

transistors (FETs). The purpose of this development board is to simplify

the evaluation process of the EPC2050 eGaN FETs by including all the

critical components on a single board that can be easily connected into

any existing converter.

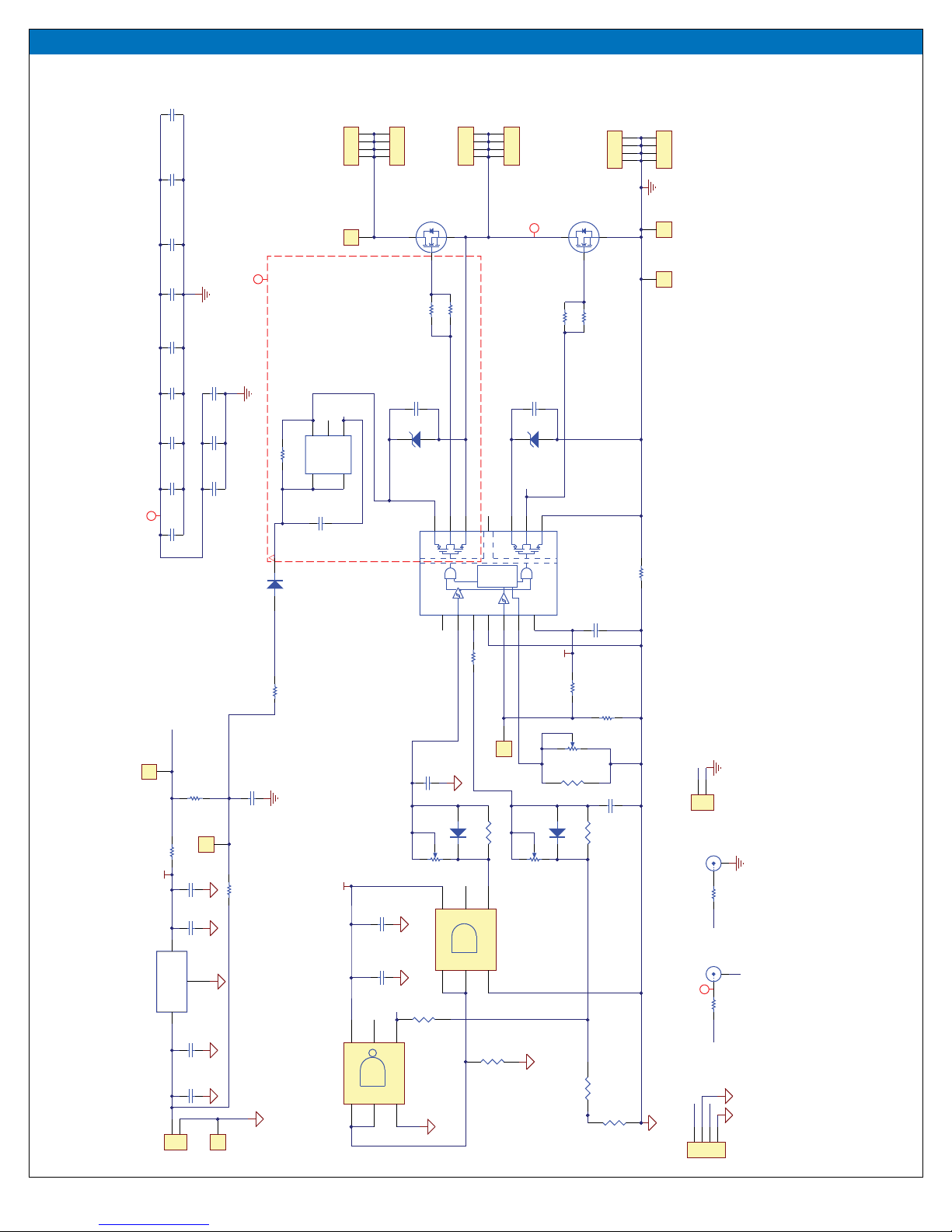

The EPC9084 development board is 1.5” x 2” and contains two

EPC2050 eGaN FETs in a half bridge conguration. As supplied, the

high side gate drive uses a digital isolator and both FETs use the

Silicon Labs SI8274GB1-IM gate driver. The board also contains all

critical components and layout for optimal switching performance.

There are also various probe points to facilitate simple waveform

measurement and eciency calculation, as well as the option to add

trimmer resistors for adjustable deadtime to provide separate high

and low side inputs, and an isolator for the low side gate drive. A block

diagram of the circuit is given in gure 2.

For more information on the EPC2050 please refer to the datasheet

available from EPC at www.epc-co.com. The datasheet should be

read in conjunction with this quick start guide.

QUICK START PROCEDURE

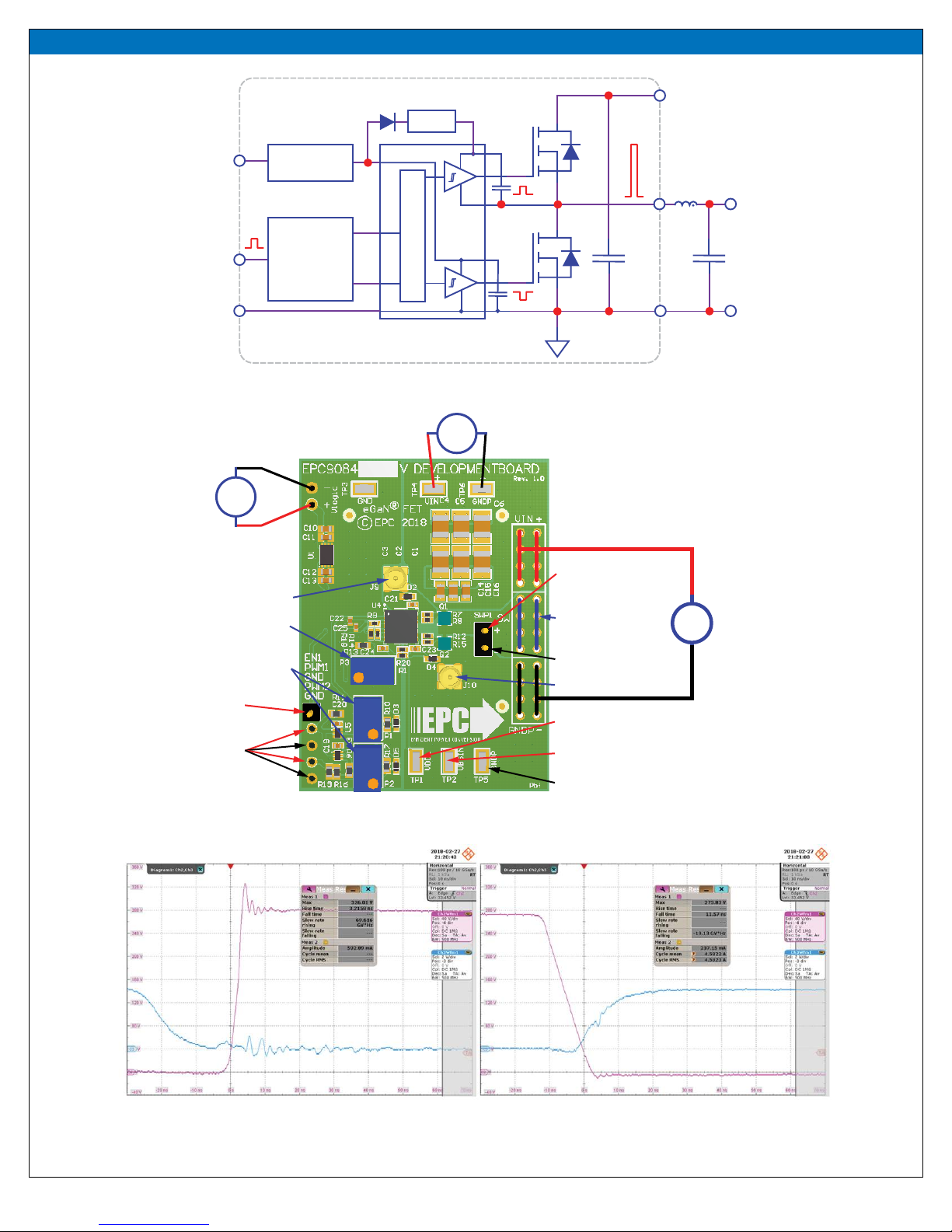

Development board EPC9084 is easy to set up to evaluate the

performance of EPC2050 eGaN FETs. Refer to gure 3 for proper connect

and measurement setup and follow the procedure below:

1. With power o, connect the input power supply bus to +VIN (J5, J6) and

ground / return to –VIN (J7, J8).

2. With power o, connect the switch node (SW) of the half bridge OUT

(J3, J4) to your circuit as required (half bridge conguration).

3. With power o, connect the gate drive power supply to +VDD

(J1, Pin-1) and ground return to –VDD (J1, Pin-2).

4. With power o, connect the input PWM control signal to PWM

(J2, Pin-1) and ground return to any of the remaining J2 pins.

5. Turn on the gate drive supply – make sure the supply is between 7.5 V

and 12 V range.

6. Turn on the controller / PWM input source.

7. Turn on the bus voltage to the required value (do not exceed the

absolute maximum voltage) and probe switching node to see

switching operation.

8. Once operational, adjust the PWM control, bus voltage, and load within

the operating range and observe the output switching behavior,

eciency and other parameters.

9. For shutdown, please follow steps in reverse.

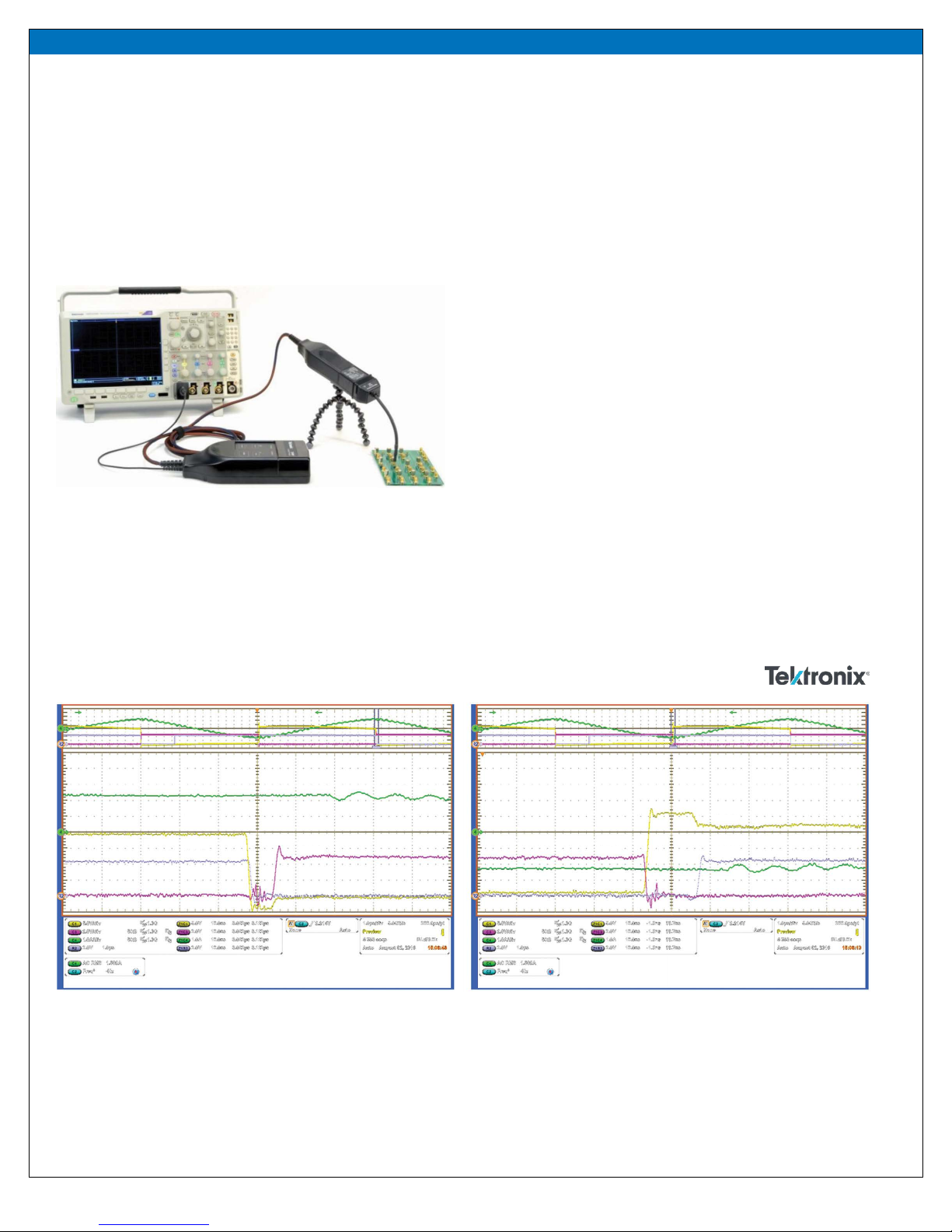

NOTE. When measuring the high frequency content switch node, care

must be taken to provide an accurate high speed measurement. An

optional two pin header (SWP1) is included for switch node measurement.

It is recommended to install measurement point on backside of board to

prevent contamination of the top side components.

For information about measurement techniques, please review the how

to GaN series: HTG09- Measurement

http://epc-co.com/epc/DesignSupport/TrainingVideos/HowtoGaN/

Figure 1: EPC9084 development board

Table 1: Performance Summary (TA= 25°C) EPC9084

Symbol Parameter Conditions Min Max Units

VDD Gate Drive Input Supply Range 7.5 12 V

VIN Bus Input Voltage Range(1) 280 V

IOUT Switch Node Output Current (2) 4 A

VPWM

PWM Logic Input Voltage

Threshold

Input ‘High’

Input ‘Low’

3.5

0

6

1.5

V

V

Minimum ‘High’ State

Input Pulse Width

VPWM rise and

fall time < 10ns 200 ns

Minimum ‘Low’ State Input

Pulse Width (3) VPWM rise and

fall time < 10ns 500 ns

(1) Maximum input voltage depends on inductive loading, maximum switch node ringing must be kept

under 350 V for EPC2050.

(2) Maximum current depends on die temperature – actual maximum current with be subject to

switching frequency, bus voltage and thermal cooling.

(3) Limited by time needed to ‘refresh’ high side bootstrap supply voltage.