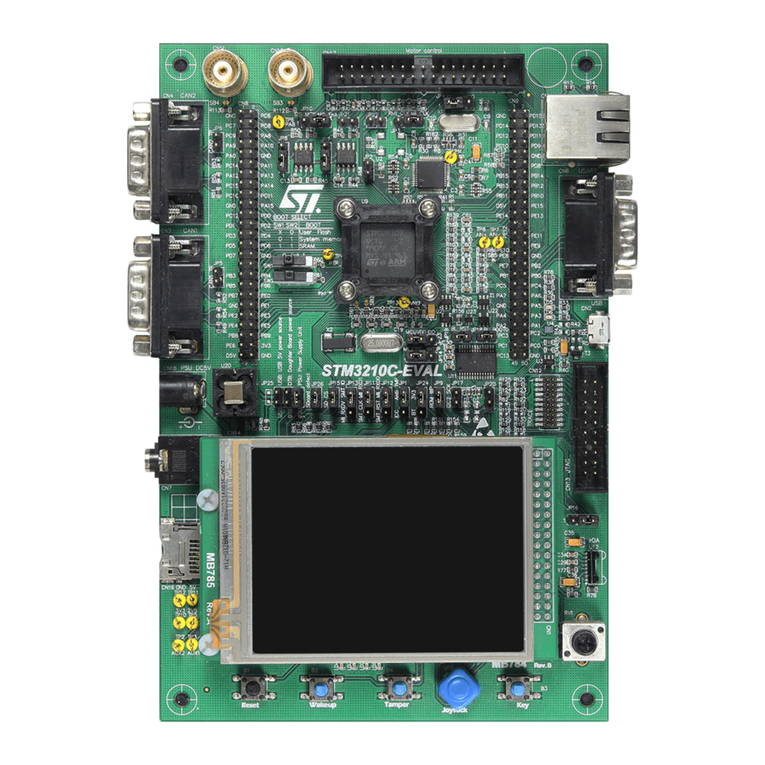

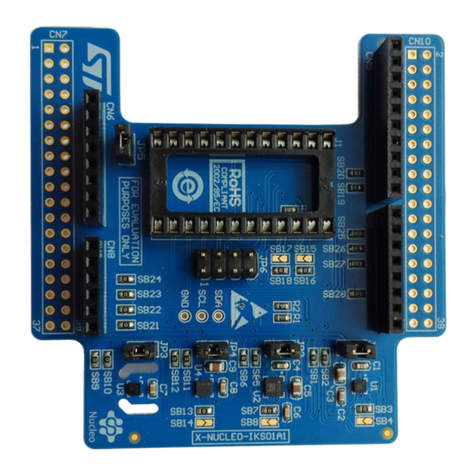

3Connectors

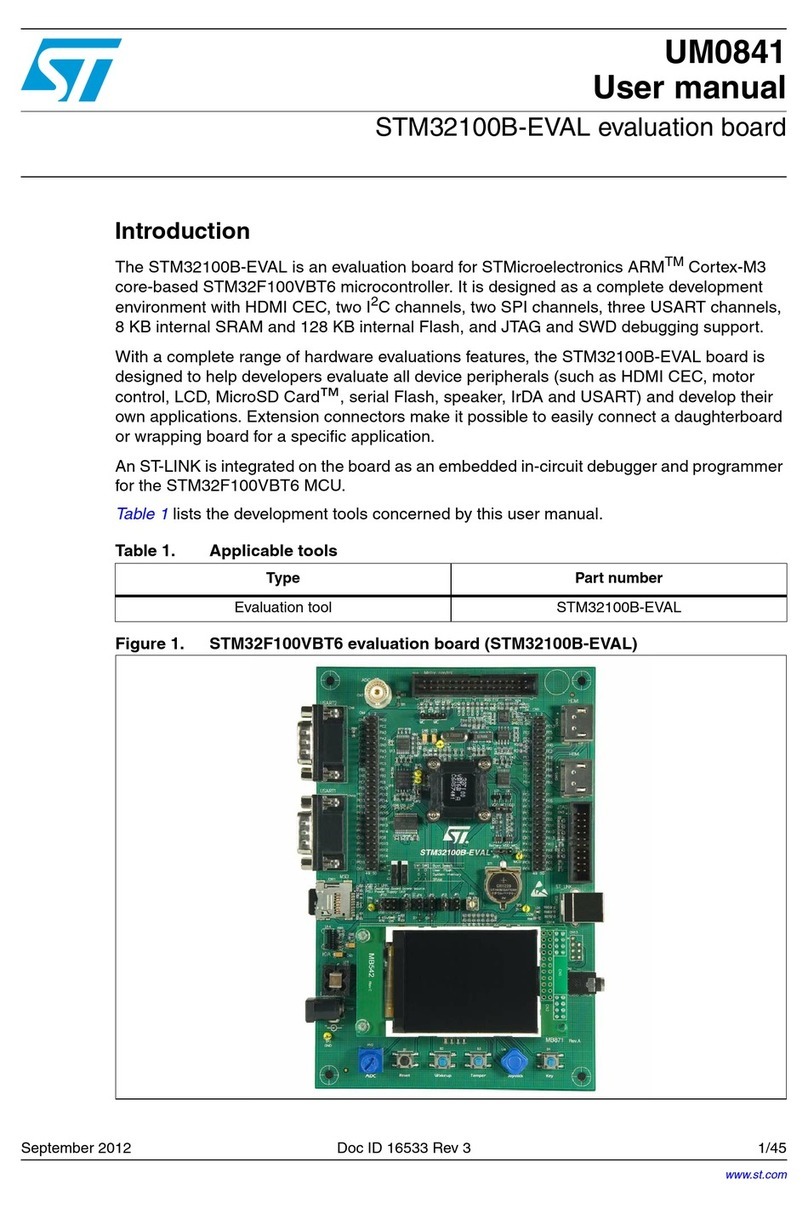

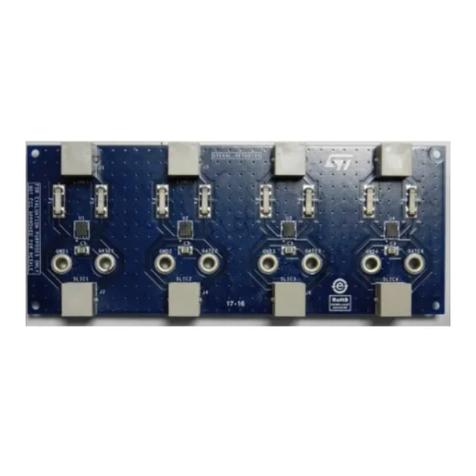

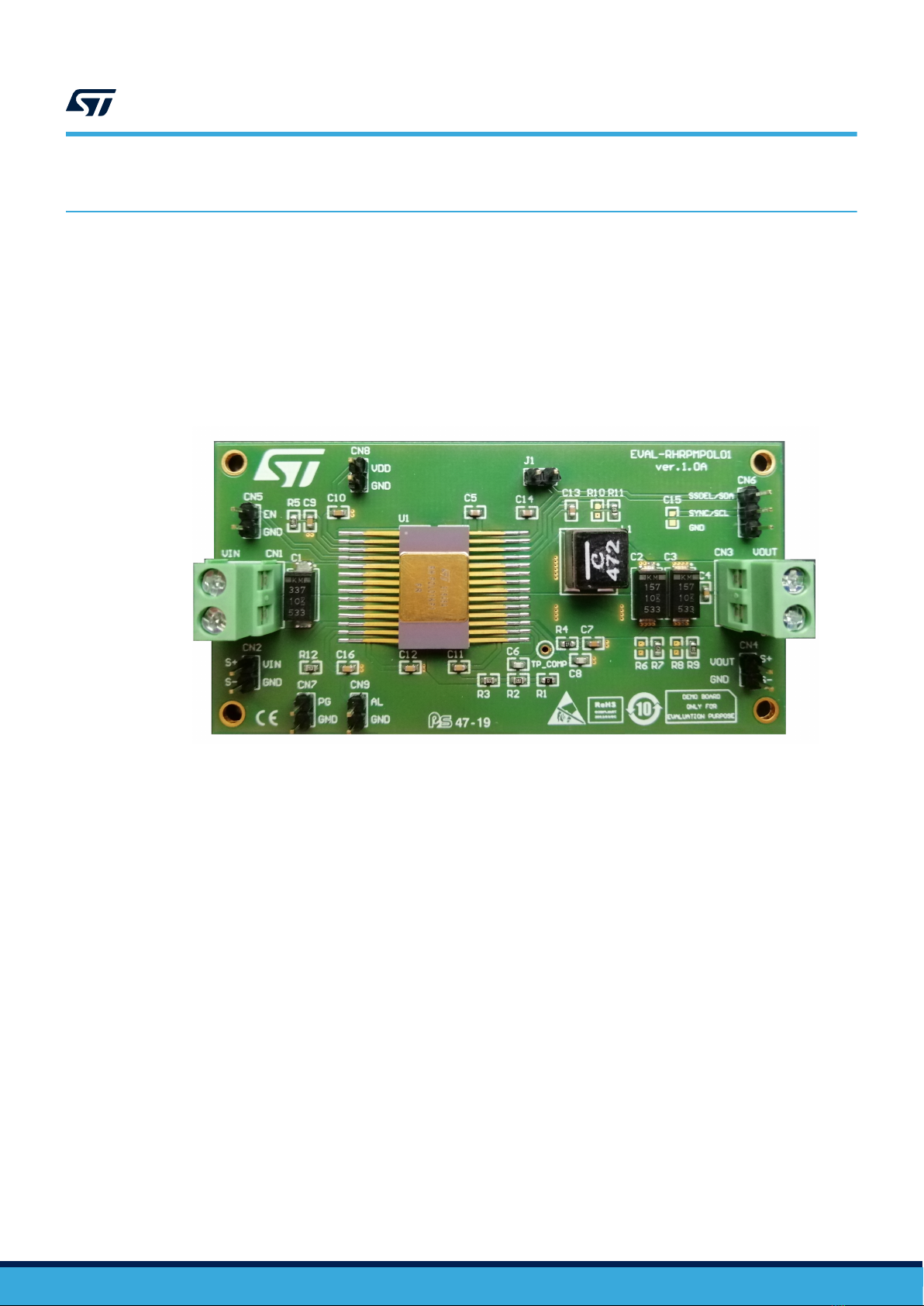

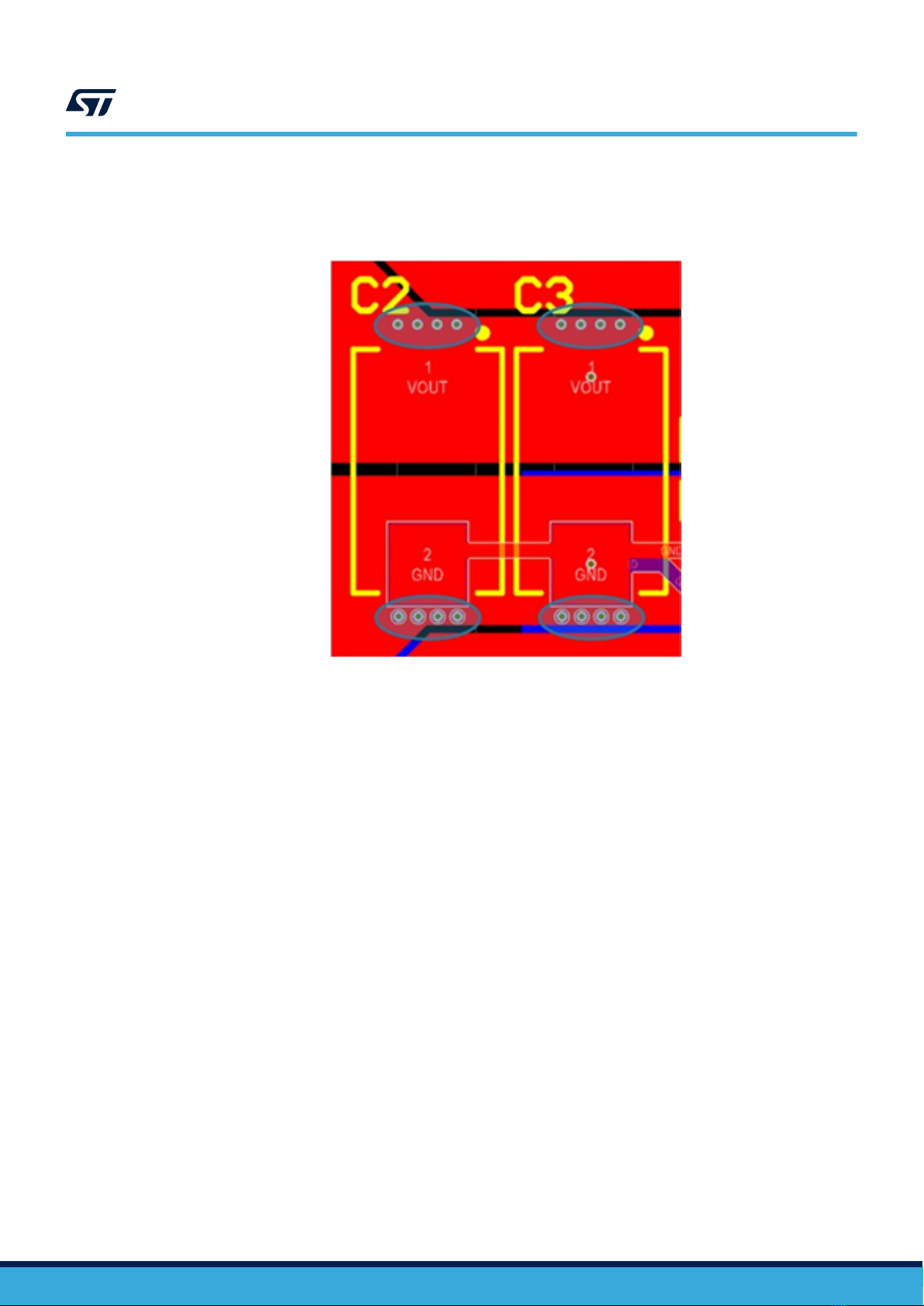

Figure 3. In/out connectors

1. Connect a power supply between VIN power (CN1_1) and GND power (CN1_2) and a power supply

between EN (CN5_1) and GND (CN5_2). The output voltage is present on VOUT pin at the voltage value

set by R1 and R2

2. Connect a multimeter between VIN (S+) (CN2_1) and GND (S-) (CN2_2) for a precise input voltage sensing

3. Connect a multimeter between VOUT (S+) (CN3_1) and GND (S-) (CN3_2) for a precise output voltage

sensing

4. Connect a multimeter between VDD (CN8_1) and GND (CN8_2) for a precise VDD voltage sensing. This pin

outputs a 2.7 V regulated voltage

5. R10 and R11 – SLOPE: the slope compensation ramp is programmed by connecting an external RSLOPE

resistor (R11) between the SLOPE pin and GND. The default internal slope compensation is also

implemented and it can be enabled by pulling up the voltage on SLOPE pin higher then 2 V or, better, up to

VDD by a resistor (R10) or simply by a short. If the SLOPE pin is directly shorted to GND, both ramps,

default current slope and programmed external current slope, are disabled

6. R8 and R9 – ILIM: the default value for the overcurrent threshold is 10 A, with a second level OCP of 13 A

(ILIM pin pulled up to VDD through R8). If a resistor (R9) is connected between ILIM pin and GND the ILIM1

threshold can be set to a lower value, and the ILIM2 will be consequently set at 1.3 x ILIM1

7. R6 and R7 – FSW: the regulator switching frequency can be programmed by connecting an external resistor

(R7) between FSW pin and GND. A voltage of 1 V is present on the FSW pin, so a current of 1 V/RFSW is

set on the resistor. This current is used to charge an internal capacitor (~20 pF). The switching frequency

can range from 100 kHz to 1 MHz. If the FSW pin is connected to a voltage higher than 2 V, (better if it is

shorted to VDD through R6), the external programmability is turned off and the internal default frequency,

tuned at 500 kHz, is enabled. To set “slave mode” configuration, FSW pin must be forced to a voltage lower

than 0.1 V or better shorted to ground. The internal clock is normally present to the SYNC pin with 180 °

phase shifting.

8. CN6 – SSDEL/SYNC: the device can also use the connectors on the demonstration board to directly control

the features through an I²C interface. In order to enable the serial interface the EN pin must be set to -2 V

and J1 has to be left open. Take care about capacitive load on pin SYNC: max. allowed capacitive load

(equivalent) for SLAVE devices is 150 pF

UM2706

Connectors

UM2706 - Rev 1 page 5/19