Texas Instruments DRV8833 User manual

Other Texas Instruments Controllers manuals

Texas Instruments

Texas Instruments DLPC3430 Manual

Texas Instruments

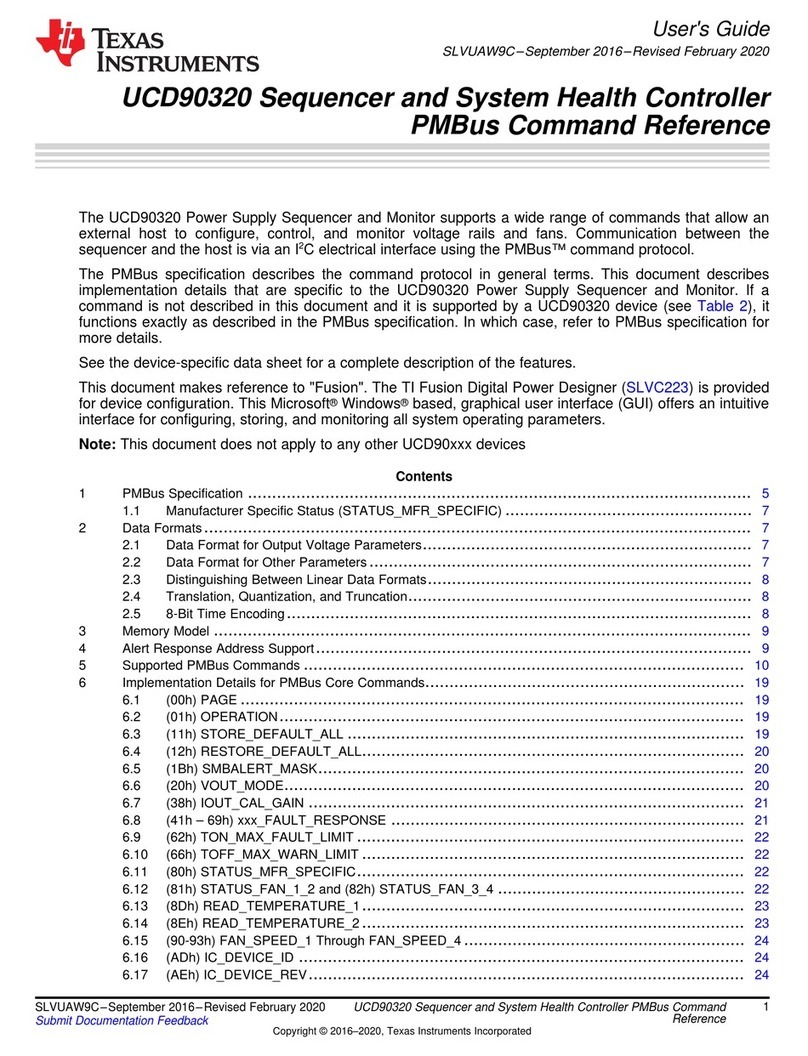

Texas Instruments UCD90320 User manual

Texas Instruments

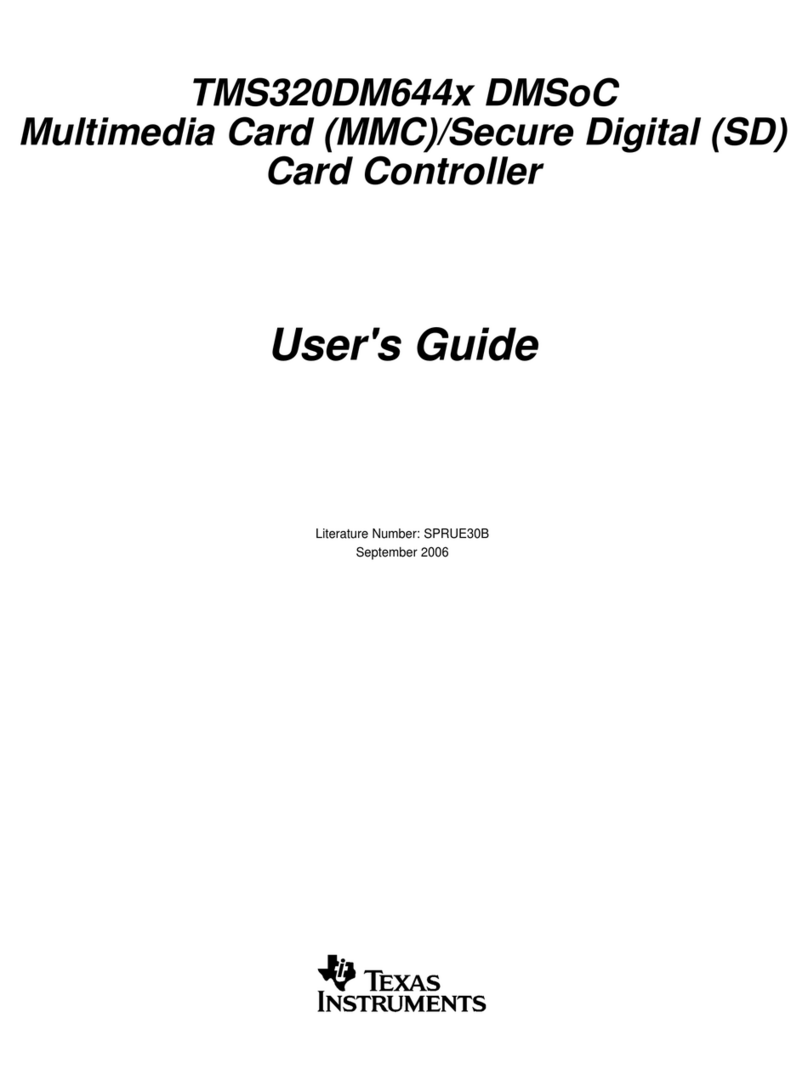

Texas Instruments TMS320DM644x User manual

Texas Instruments

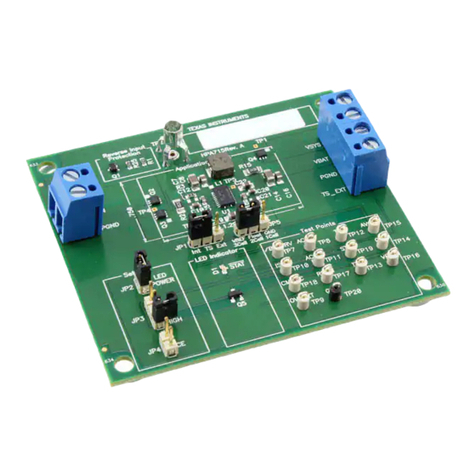

Texas Instruments bq24133EVM User manual

Texas Instruments

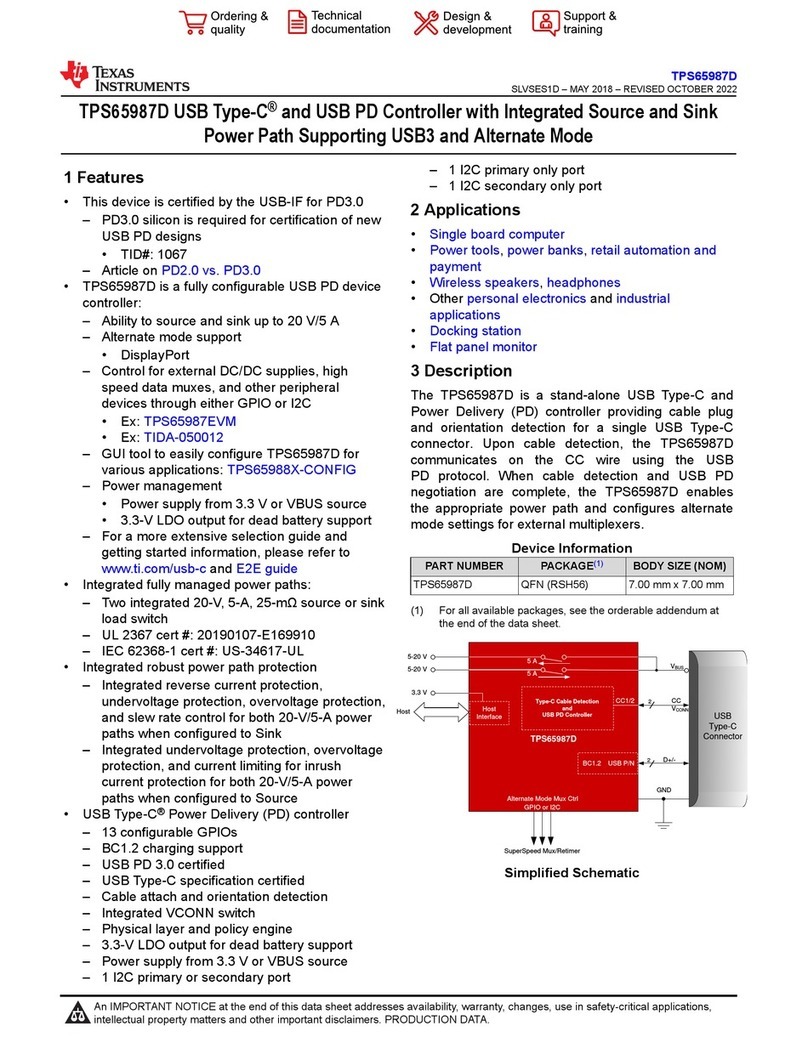

Texas Instruments TPS65987D User manual

Texas Instruments

Texas Instruments TPS40100 User manual

Texas Instruments

Texas Instruments TPS23755 User manual

Texas Instruments

Texas Instruments bq24013 User manual

Texas Instruments

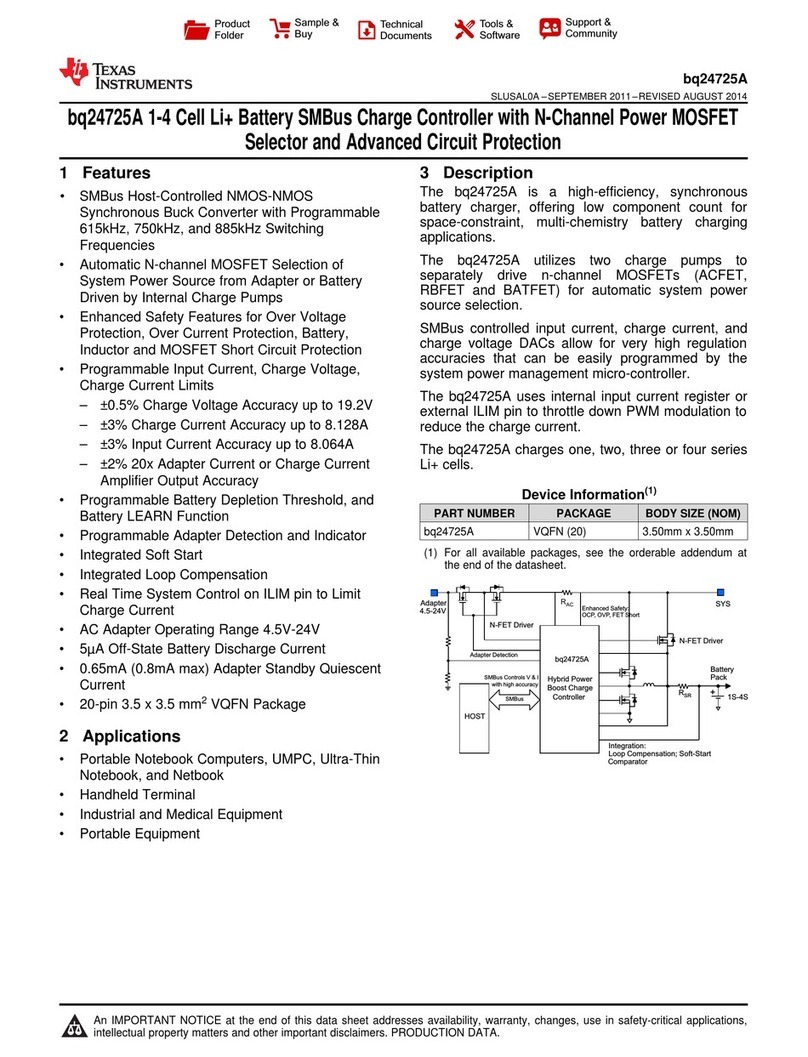

Texas Instruments bq24725A User manual

Texas Instruments

Texas Instruments bq78350-R1 Use and care manual

Texas Instruments

Texas Instruments TMS320x2833 series User manual

Texas Instruments

Texas Instruments TMDSHVMTRPFCKIT User manual

Texas Instruments

Texas Instruments TMS320DM646 Series User manual

Texas Instruments

Texas Instruments DM648 DSP User manual

Texas Instruments

Texas Instruments TSB12LV26 Installation and user guide

Texas Instruments

Texas Instruments PCI7621 Installation and user guide

Texas Instruments

Texas Instruments TPS65981 User manual

Texas Instruments

Texas Instruments LM3429 User manual

Texas Instruments

Texas Instruments TPS51100 User manual

Texas Instruments

Texas Instruments TMS320C2000 User manual

Popular Controllers manuals by other brands

Digiplex

Digiplex DGP-848 Programming guide

YASKAWA

YASKAWA SGM series user manual

Sinope

Sinope Calypso RM3500ZB installation guide

Isimet

Isimet DLA Series Style 2 Installation, Operations, Start-up and Maintenance Instructions

LSIS

LSIS sv-ip5a user manual

Rockwell Automation

Rockwell Automation 1769-L31 installation instructions