Texas Instruments TA 5 42EVM-K Series User manual

Other Texas Instruments Motherboard manuals

Texas Instruments

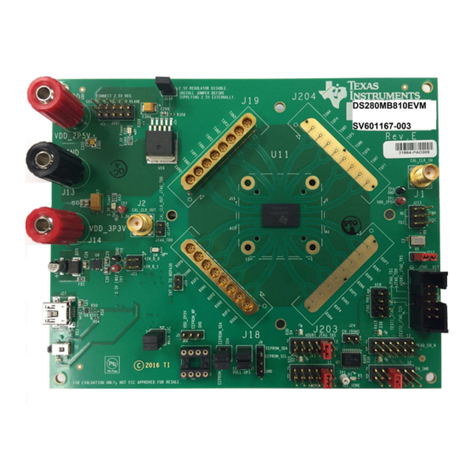

Texas Instruments DS280DF810EVM User manual

Texas Instruments

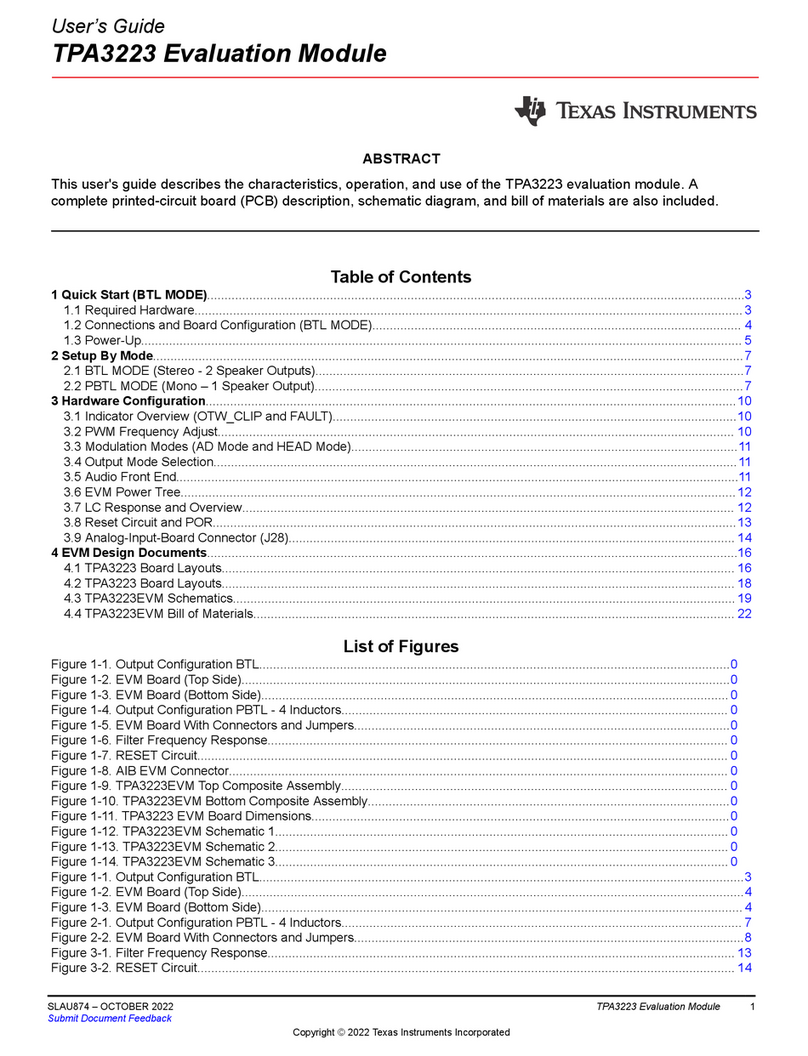

Texas Instruments TPA3223EVM User manual

Texas Instruments

Texas Instruments TRF4900 User manual

Texas Instruments

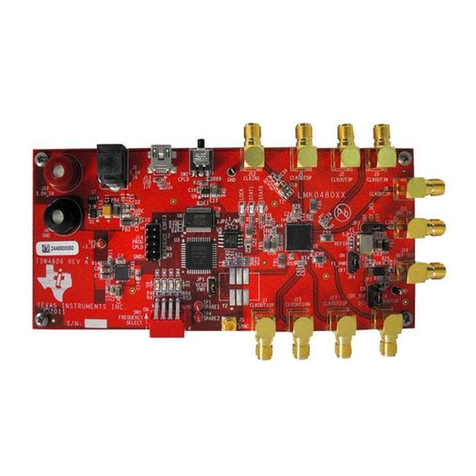

Texas Instruments TSW4806EVM User manual

Texas Instruments

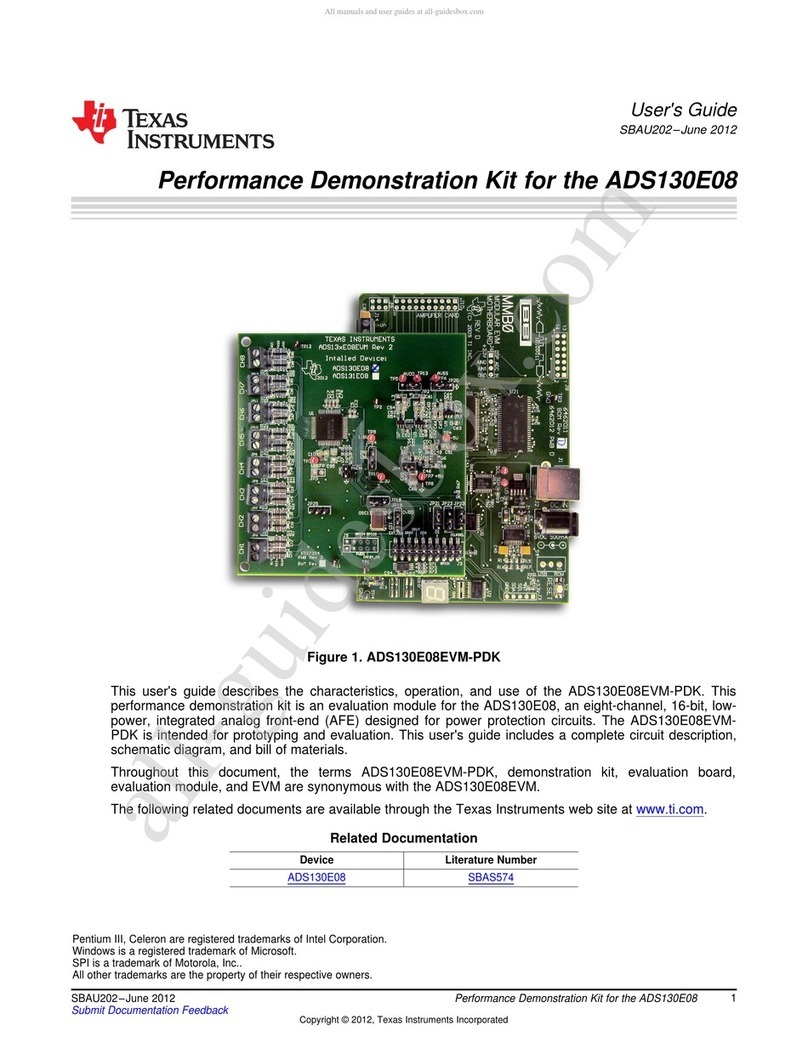

Texas Instruments ADS130E08 User manual

Texas Instruments

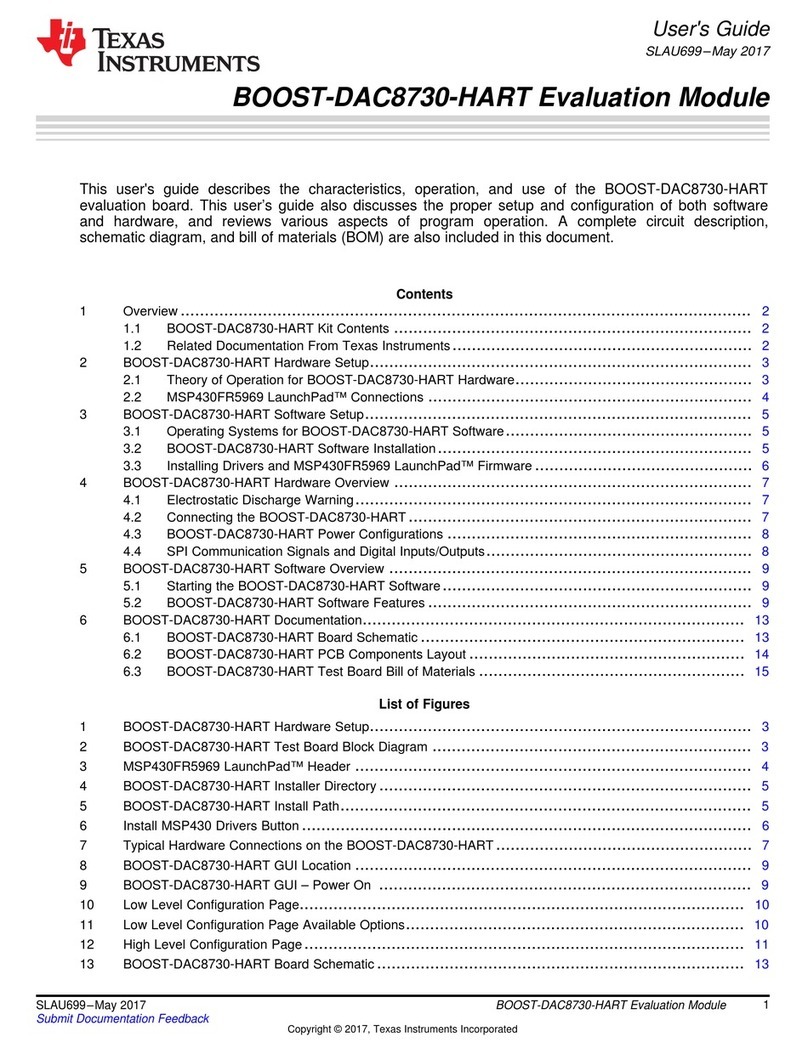

Texas Instruments BOOST-DAC8730-HART User manual

Texas Instruments

Texas Instruments DS90UH949A-Q1EVM User manual

Texas Instruments

Texas Instruments TPS65033-Q1 Series User manual

Texas Instruments

Texas Instruments UCC21220EVM-009 User manual

Texas Instruments

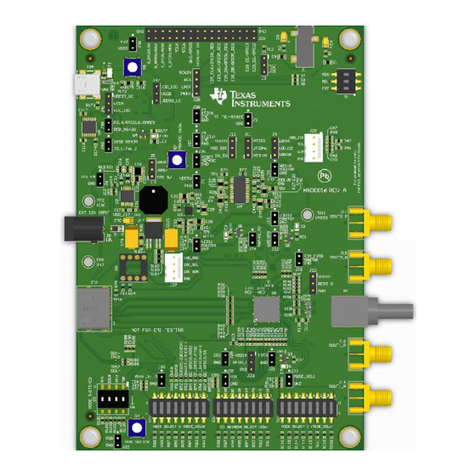

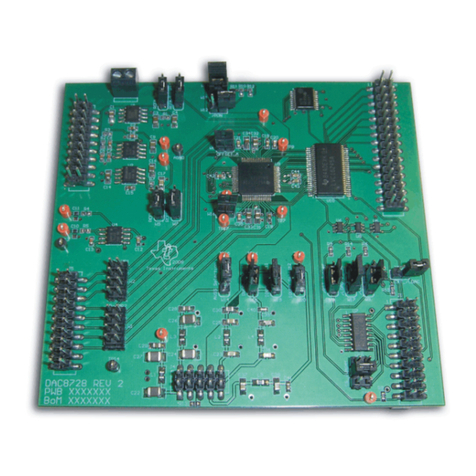

Texas Instruments DAC8728EVM User manual

Texas Instruments

Texas Instruments TAS5731EVM User manual

Texas Instruments

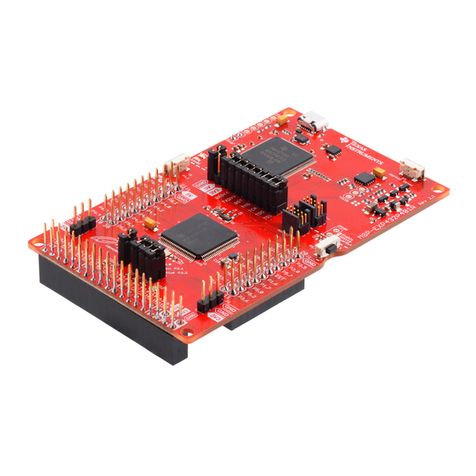

Texas Instruments MSP-EXP432P401R User manual

Texas Instruments

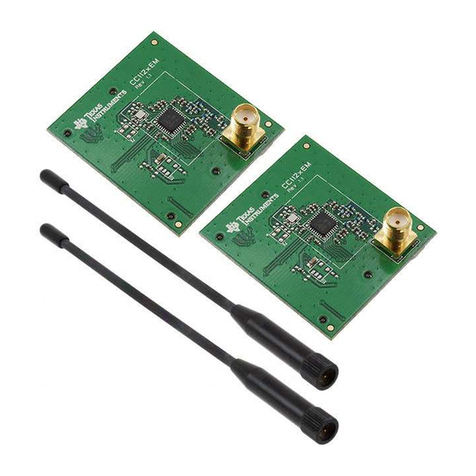

Texas Instruments CC112 Series User manual

Texas Instruments

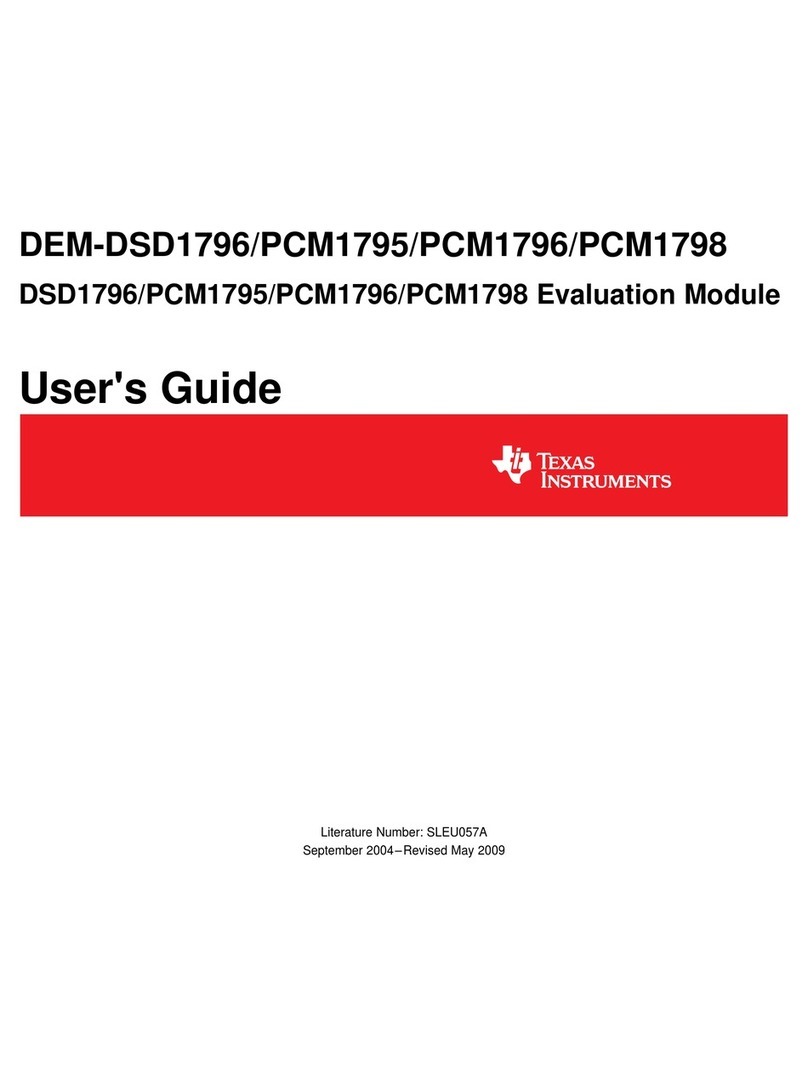

Texas Instruments DEM-DSD1796 User manual

Texas Instruments

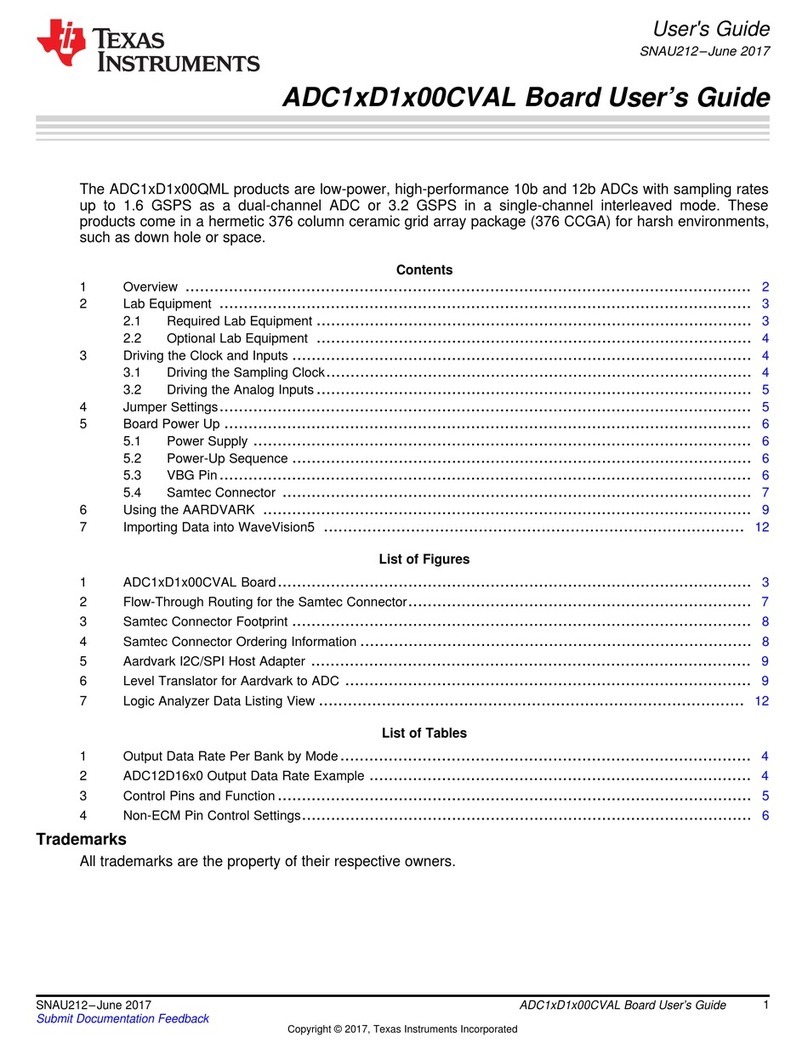

Texas Instruments ADC1xD1x00CVAL Series User manual

Texas Instruments

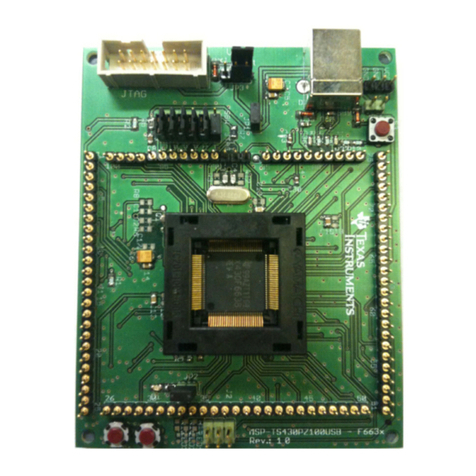

Texas Instruments MSP430F663 Series User manual

Texas Instruments

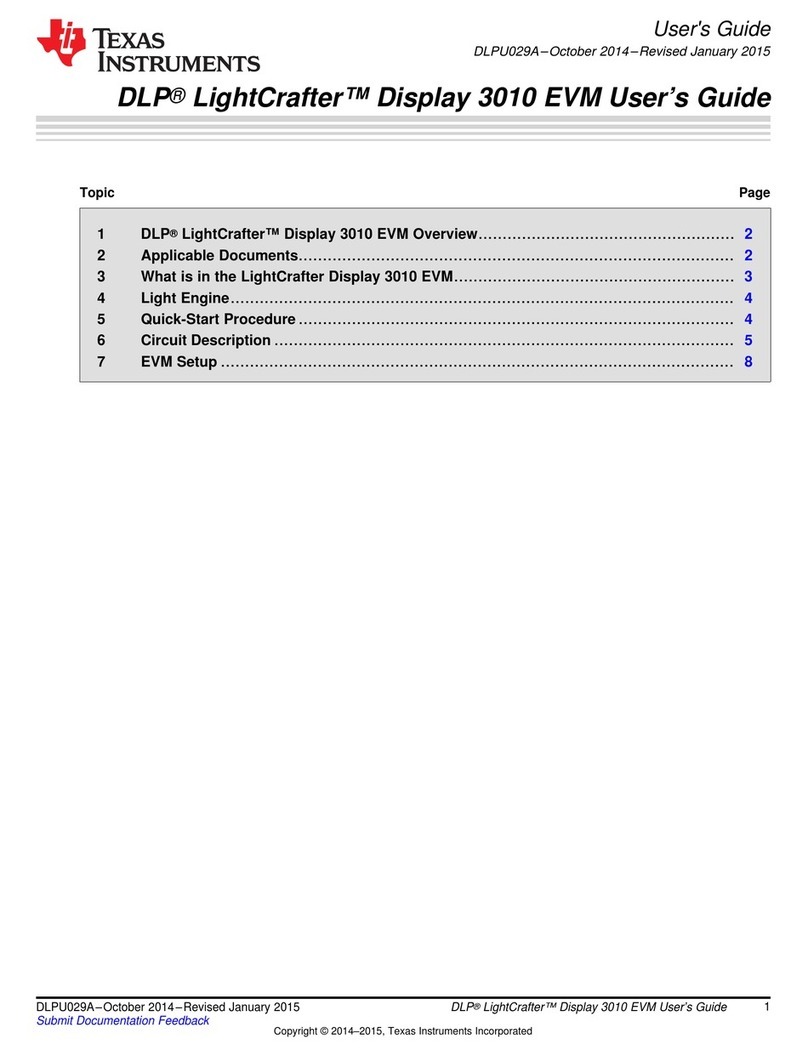

Texas Instruments DLP LightCrafter Display 3010 User manual

Texas Instruments

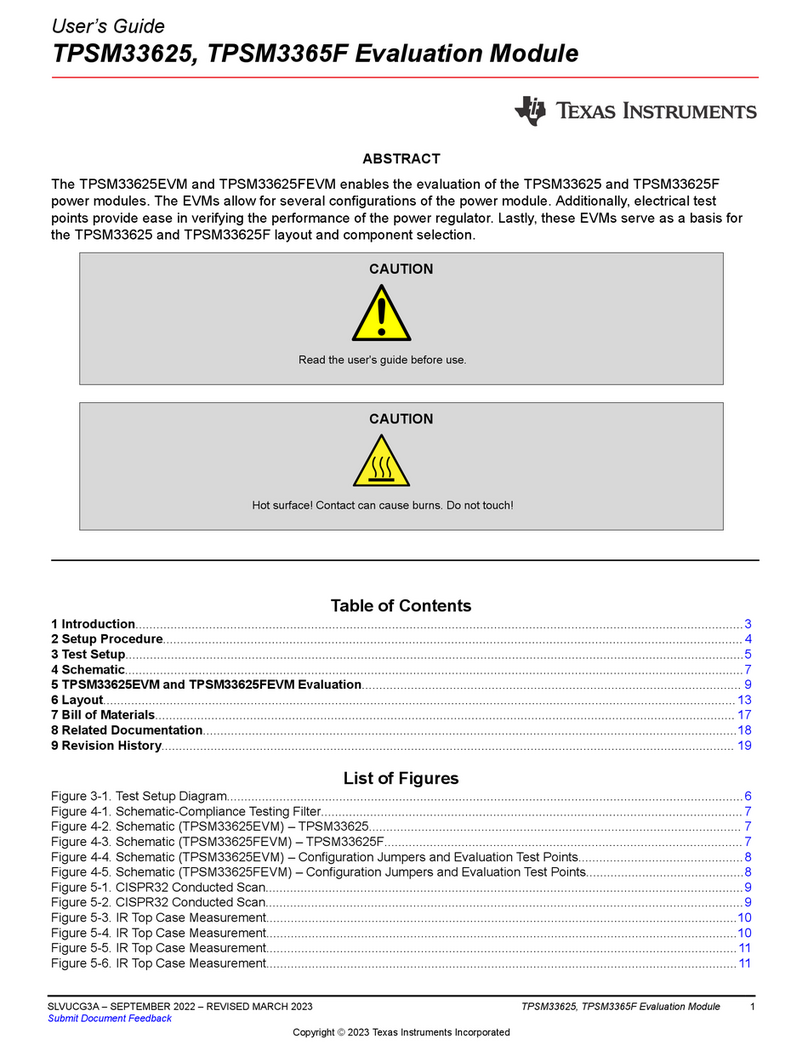

Texas Instruments TPSM33625EVM User manual

Texas Instruments

Texas Instruments ADS1178EVM User manual

Texas Instruments

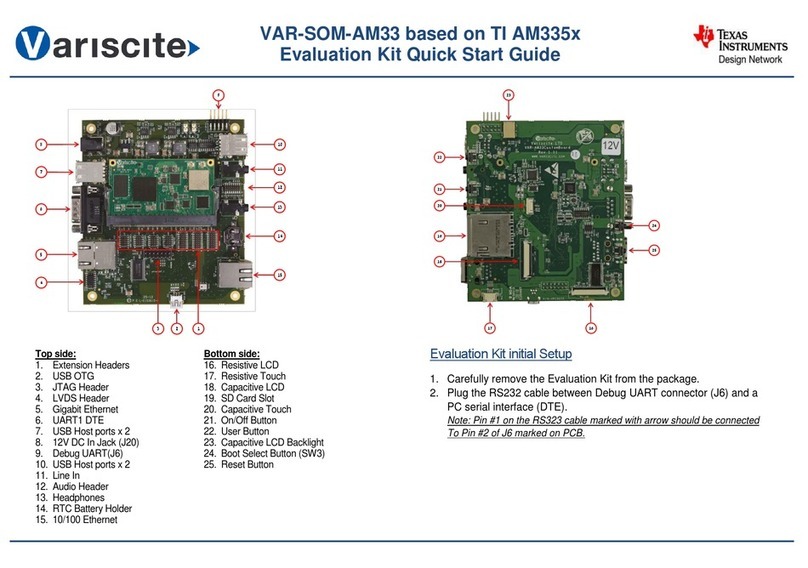

Texas Instruments VAR-SOM-AM33 User manual