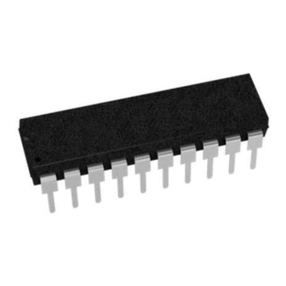

EM78P156EL

OTP ROM

This specification is subject to change without prior notice. 2002/04/195

Table 2EM78P156ELAS Pin Description

Symbol Pin No. Type Function

VDD 15 -* Power supply.

OSCI 17 I* XTAL type: Crystal input terminal or external clock input pin.

* ERC type: RC oscillator input pin.

OSCO 16 I/O * XTAL type: Output terminal for crystal oscillator or external clock input pin.

* RC type: Instruction clock output.

* External clock signal input.

TCC 4I

* The real time clock/counter (with Schmitt trigger input pin), must be tied to

VDD or VSS if not in use.

/RESET 5I

* Input pin with Schmitt trigger. If this pin remains at logic low, the controller

will also remain in reset condition.

P50~P53

18, 19,

2, 3I/O * P50~P53 are bi-directional I/O pins.

* P50 and P51 can also be defined as the R-option pins.

* P50~P52 can be pulled-down by software.

P60~P67

7~14I/O * P60~P67 are bi-directional I/O pins.

* These can be pulled-high or can be open-

drain by software programming.

* P60~P63 can also be pulled-down by software.

/INT 7I* External interrupt pin triggered by falling edge.

VSS 6-* Ground.

Table 3EM78P156ELKM Pin Description

Symbol Pin No. Type Function

VDD 15,16 -* Power supply.

OSCI 18 I* XTAL type: Crystal input terminal or external clock input pin.

* ERC type: RC oscillator input pin.

OSCO 17 I/O * XTAL type: Output terminal for crystal oscillator or external clock input pin.

* RC type: Instruction clock output.

* External clock signal input.

TCC 3I

* The real time clock/counter (with Schmitt trigger input pin), must be tied to

VDD or VSS if not in use.

/RESET 4I* Input pin with Schmitt trigger. If this pin remains at logic low, the controll

will also remain in reset condition.

P50~P53

19, 20,

1, 2I/O * P50~P53 are bi-directional I/O pins.

* P50 and P51 can also be defined as the R-option pins.

* P50~P52 can be pulled-down by software.

P60~P67

7~14I/O * P60~P67 are bi-directional I/O pins.

* These can be pulled-high or can be open-

drain by software programming.

* P60~P63 can also be pulled-down by software.

/INT 7I* External interrupt pin triggered by falling edge.

VSS 5, 6 -* Ground.