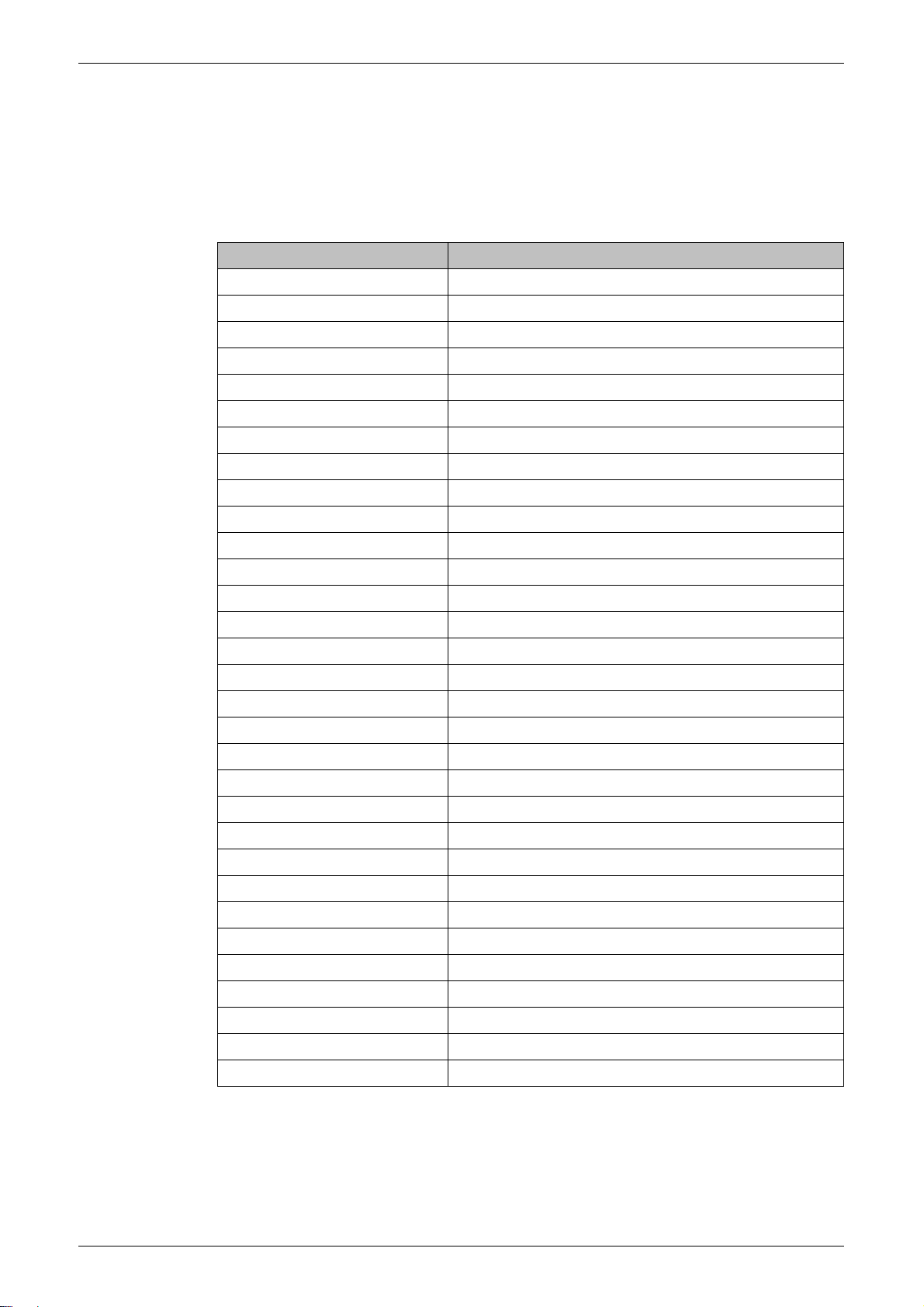

List of Figures

Figure 4-1 Configuring Pin Reuse ..................................................................................................... 11

Figure 5-1 Recommended Pin Connection........................................................................................ 17

Figure 5-2 Power Recycle Timing...................................................................................................... 17

Figure 5-3 Trigger Timing................................................................................................................... 18

Figure 5-4 Connection Diagram for JTAG Configuration Mode......................................................... 20

Figure 5-5 Connection Diagram of JTAG Daisy-Chain Configuration Mode ..................................... 20

Figure 5-6 JTAG Configuration timing................................................................................................21

Figure 5-7 TAP State Machine........................................................................................................... 22

Figure 5-8 Instruction Register Access Timing .................................................................................. 23

Figure 5-9 Data Register Access Timing ...........................................................................................23

Figure 5-10 Flow Chart of Reading ID Code State Machine ............................................................. 25

Figure 5-11 Access Timing of Reading ID Code Instruction - 0x11....................................................25

Figure 5-12 Access Timing of Reading ID Code Data Register......................................................... 25

Figure 5-13 SRAM Configuration Flow ...........................................................................................27

Figure 5-14 Process of Reading SRAM............................................................................................. 29

Figure 5-15 Process of Use Boundary Scan Mode to Program SPI Flash........................................ 36

Figure 5-16 Connection Diagram of Daisy-Chain..............................................................................38

Figure 5-17 SSPI Configuration Timing .............................................................................................40

Figure 5-18 Read ID Code Timing ..................................................................................................... 41

Figure 5-19 Write Enable (0x15) Timing ............................................................................................ 42

Figure 5-20 Write Disable(0x3A00) Timing........................................................................................42

Figure 5-21 Write Data (0x3B) Timing ............................................................................................... 43

Figure 5-22 SSPI Configuration Mode Connection Diagram.................................................................. 45

Figure 5-23 Connection Diagram of Programming External Flash via SSPI..................................... 45

Figure 5-24 The Flow Chart of Flash Configuration via SSPI............................................................ 46

Figure 5-25 Multiple FPGA Connection Diagram 1............................................................................46

Figure 5-26 Multiple FPGA Connection Diagram 2............................................................................47

Figure 5-27 QSSPI Write Data (0x6B) Timing ...................................................................................48

Figure 5-28 The Flow Chart of SRAM Configuration via QSSPI .......................................................49

Figure 5-29 Connection Diagram for CPU Mode...............................................................................50

Figure 5-30 CPU Mode Configuration Timing.................................................................................... 51

Figure 5-31 Connection Diagram for SERIAL Mode..........................................................................52

Figure 5-32 SERIAL Configuration Timing......................................................................................... 52

Figure 5-33 Connection Diagram for I2C Configuration Mode........................................................... 54