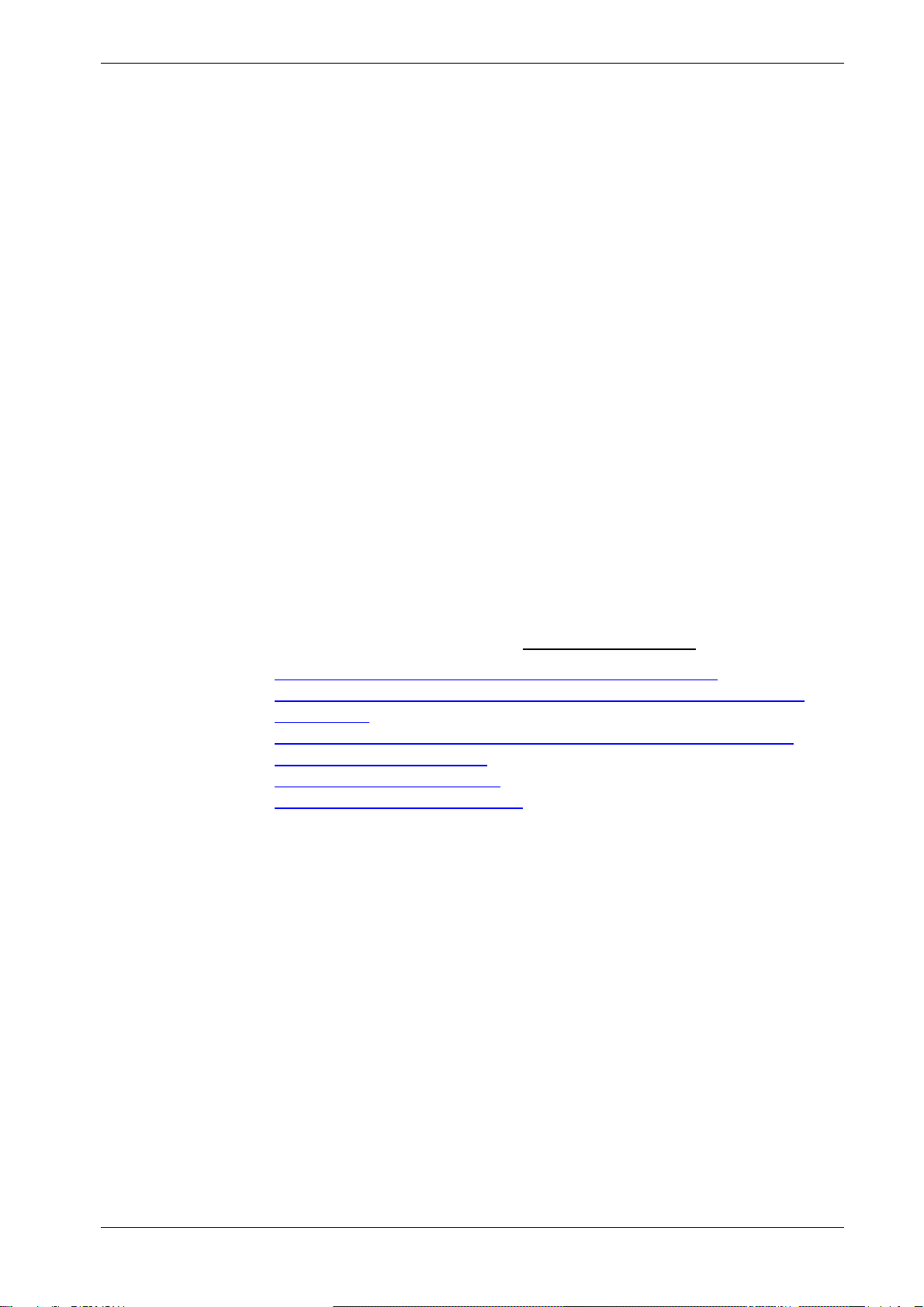

Contents

Contents.................................................................................................................i

List of Figures....................................................................................................iii

List of Tables......................................................................................................iv

1About This Guide ..........................................................................................1

1.1 Purpose .............................................................................................................................. 1

1.2 Related Documents............................................................................................................1

1.3 Abbreviations and Terminology...........................................................................................2

1.4 Support and Feedback ....................................................................................................... 2

2Overview ........................................................................................................3

2.1 PB-Free Package ...............................................................................................................3

2.2 Package and Max. User I/O Information ............................................................................4

2.3 Power Pin ...........................................................................................................................4

2.4 Pin Quantity........................................................................................................................5

2.4.1 Quantity of GW1NS-2 / GW1NS-2C Pins........................................................................5

2.4.2 Quantity of GW1NS-4 / GW1NS-4C Pins........................................................................6

2.5 Pin Definitions.....................................................................................................................7

2.6 Introduction to the I/O BANK .............................................................................................. 9

3View of Pin Distribution.............................................................................. 11

3.1 View of GW1NS-2/GW1NS-2C Pins Distribution ............................................................. 11

3.1.1 View of QN32 Pins Distribution ..................................................................................... 11

3.1.2 View of QN32U Pins Distribution...................................................................................12

3.1.3 View of CS36 Pins Distribution......................................................................................13

3.1.4 View of CS36U Pins Distribution................................................................................... 14

3.1.5 View of QN48 Pins Distribution .....................................................................................15

3.1.6 View of LQ144Pins Distribution.....................................................................................16

3.2 View of GW1NS-4/GW1NS-4C Pins Distribution ............................................................. 17

3.2.1 View of CS49 Pins Distribution......................................................................................17

3.2.2 View of QN48 Pins Distribution .....................................................................................18

3.2.3 View of MG64 Pins Distribution.....................................................................................19