Table of Contents

1. INTRODUCTION.........................................................................................................................................................7

1.1 Purpose .............................................................................................................................................................7

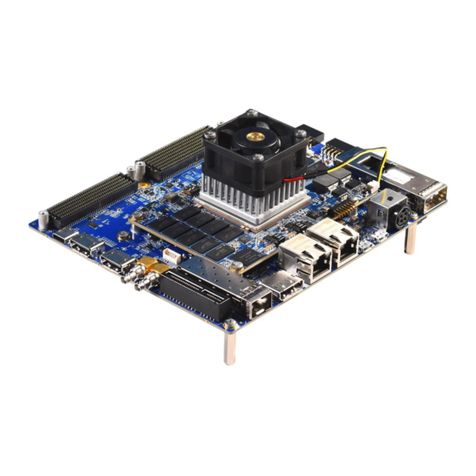

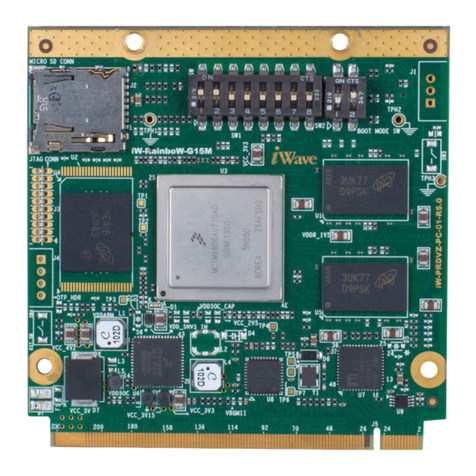

1.2 SOM Overview ..................................................................................................................................................7

1.3 List of Acronyms................................................................................................................................................7

1.4 Terminology Description...................................................................................................................................9

1.5 References ........................................................................................................................................................9

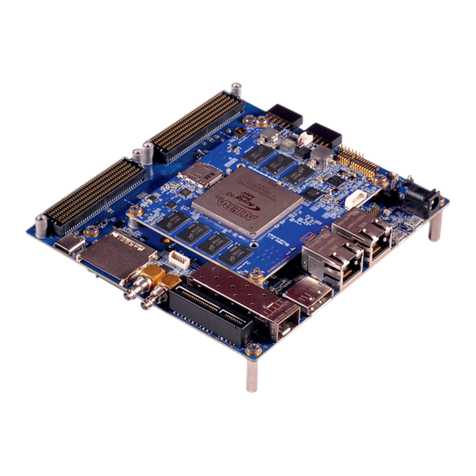

2. ARCHITECTURE AND DESIGN ..................................................................................................................................10

2.1 Versal AI Edge/Prime SOM Block Diagram......................................................................................................10

2.2 Versal AI Edge SOM Features..........................................................................................................................11

2.3 Versal AI Edge .................................................................................................................................................13

2.3.1.1 SoC Power ................................................................................................................................................................16

2.3.1.2 SoC Reset..................................................................................................................................................................16

2.3.1.3 Versal System Monitor.............................................................................................................................................16

2.3.1.4 Versal Configuration Power & Status LEDs..............................................................................................................17

2.3.1.5 Versal Boot Mode Configuration .............................................................................................................................18

2.3.2 Clock Design....................................................................................................................................................19

2.3.2.1 Clock Synthesizer .....................................................................................................................................................19

2.3.3 Versal AI Edge/Prime SOM PMIC’s..................................................................................................................20

2.3.3.1 PMIC Regulator 1 with RTC ......................................................................................................................................20

2.3.3.2 PMIC Regulator 2 without RTC.................................................................................................................................20

2.3.4 SOM Memory..................................................................................................................................................21

2.3.4.1 LPDDR4 SDRAM........................................................................................................................................................21

2.3.4.2 QSPI Flash.................................................................................................................................................................21

2.3.4.3 eMMC Flash .............................................................................................................................................................21

2.4 On SOM Features............................................................................................................................................22

2.4.1 Fan Header..................................................................................................................................................22

2.5 Board to Board Connector1............................................................................................................................23

2.5.1 PL Interfaces................................................................................................................................................26

2.5.2 PL IOs –XPIO BANK 703 ..............................................................................................................................26

2.5.3 PL IOs –XPIO BANK 702 ..............................................................................................................................30

2.5.4 PL IOs –HD BANK 302.................................................................................................................................33

2.5.5 Power Control Output.................................................................................................................................34

2.6 Board to Board Connector2............................................................................................................................35

2.6.1 PS Interfaces................................................................................................................................................39

2.6.2 USB2.0 OTG Interface .................................................................................................................................39

2.6.3 Gigabit Ethernet Interface ..........................................................................................................................40

2.6.4 RGMII/ULPI Interface..................................................................................................................................41

2.6.5 SD/SDIO Interface .......................................................................................................................................42

2.6.6 Debug UART Interface.................................................................................................................................43

2.6.7 I2C Interface................................................................................................................................................43

2.6.8 SPI Interface ................................................................................................................................................44