1.3.2 Procedure to test a typical full charging cycle

The three most important STBC02 functional modes are:

battery mode: VBAT valid range, system up and running, VIN invalid range;

shutdown mode: device supplied by battery but in shutdown mode;

VIN mode: VIN valid range present.

The charger is designed to be used with Li-Ion batteries (Li-Ion nominal battery voltage is

3.7-3.8V). VBAT range is 0 (dead battery) to 4.5 V (overcharged battery). The device input

operating supply voltage is 4.5 to 5.5 VDC.

The procedure to demonstrate this power path charger is:

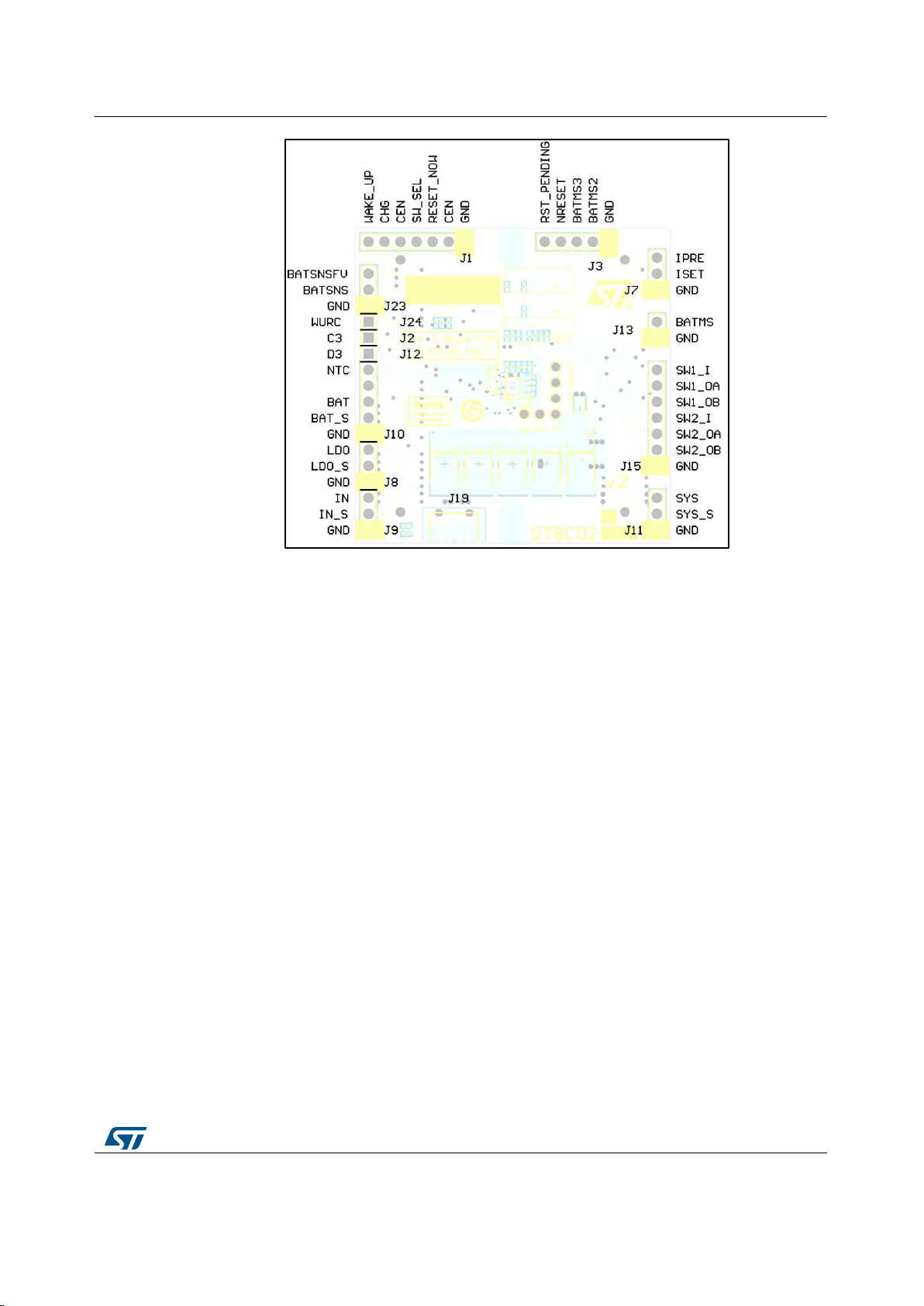

Connect one high impedance probe to J1/pin6 (CHG) vs GND.

Connect one high impedance probe to J10/pin2 (BAT_S) vs. GND.

Place the current probe on the positive battery terminal wire.

Connect (fully discharged) battery (e.g. 2.5 V) to J10/pin3 (VBAT) vs. GND.

Connect power supply ~5.0 V to J9/pin3 (IN) vs GND.

Battery starts charging by IPRE charging current. Verify that IBAT is ~6 mA (10%

of IFAST).

Connect a 33 Ω, ½-W resistor to J8/pin3 (LDO) vs. GND.

With a high impedance probe, verify that LDO (node LDO_S - J8/pin2) output is 3.1

V.

CHG toggles (6 Hz).

When battery voltage level exceeds VPRE (3 V), the charging current changes

from IPRE to IFAST and increases to ~ 60 mA (IFAST setup). During this phase,

CHG is still toggling at the same frequency if no warning/alarm is detected. In this

condition, LDO and system are powered by the power supply.

Verify with high impedance probe that SYS voltage (J11/pin2) is approximately 5 V

(IN node level minus internal MOS drop).

You can stop the charging cycle by a jumper to short CEN to GND (short J1/pin2 to

J1/pin1) just to verify CEN pin is functional.

Verify that the charger stops.

CHG changes state and its level goes low.

Remove short CEN to GND to continue charging.

Charge the battery fully

At a certain battery level (typical 4.2 V), charging current starts falling and battery

voltage level remains constant at VFLOAT level.

Battery charging is automatically stopped when battery charging current drops

under 5 % of IFAST.

Disconnect charger to observe device behavior in battery mode.

Battery starts discharging to supply the load connected to LDO output; the current

probe measures a negative value (~VLDO/resistive load).

Verify through high impedance probe that SYS_S voltage (J11/pin2) is VBAT voltage

minus VBAT equal to VSYS MOSFET RDSON multiplied by load current.

Remove resistive load from the LDO output.