7.8 Interrupt enable accept timing.............................................................................................63

7.9 Interrupt service routine address ........................................................................................63

7.10 Saving/restore general purpose registers...........................................................................63

7.11 Interrupt timing....................................................................................................................64

7.12 Interrupt register overview ..................................................................................................64

7.12.1 Interrupt Enable Register (IE, IE1, and IE2)...........................................................64

7.12.2 Interrupt Priority Register (IP and IP1)...................................................................64

7.12.3 External Interrupt Flag Register (EIFLAG0 and EIFLAG1)....................................65

7.12.4 External Interrupt Polarity Register (EIPOL0L, EIPOL0H, and EIPOL1)...............65

7.12.5 Register map..........................................................................................................65

7.12.6 Interrupt register description...................................................................................66

8Clock generator............................................................................................................................69

8.1 Clock generator block diagram ...........................................................................................69

8.2 Register map.......................................................................................................................70

8.3 Register description ............................................................................................................70

9Basic interval timer.......................................................................................................................71

9.1 BIT block diagram...............................................................................................................71

9.2 BIT register map..................................................................................................................71

9.3 BIT register description.......................................................................................................72

10 Watchdog timer............................................................................................................................73

10.1 Setting window open period of watchdog timer ..................................................................74

10.2 WDT block diagram ............................................................................................................75

10.3 Register map.......................................................................................................................75

10.4 Register description ............................................................................................................76

11 Timer 0/1/2...................................................................................................................................78

11.1 Timer 0................................................................................................................................78

11.1.1 8-bit timer/counter mode ........................................................................................78

11.1.2 8-bit PWM mode.....................................................................................................80

11.1.3 8-bit capture mode .................................................................................................82

11.1.4 Timer 0 block diagram............................................................................................84

11.1.5 Register map..........................................................................................................84

11.1.6 Register description................................................................................................85

11.2 Timer 1................................................................................................................................87

11.2.1 16-bit timer/counter mode ......................................................................................87

11.2.2 16-bit capture mode ...............................................................................................89

11.2.3 16-bit PPG mode....................................................................................................91

11.2.4 16-bit Complementary PWM mode (Dead Time)...................................................93

11.2.5 16-bit timer 1 block diagram...................................................................................95

11.2.6 Register map..........................................................................................................95

11.2.7 Register description................................................................................................96

11.3 Timer 2................................................................................................................................99

11.3.1 16-bit timer/counter mode ......................................................................................99

11.3.2 16-bit capture mode .............................................................................................101

11.3.3 16-bit PPG mode..................................................................................................103

11.3.4 16-bit timer 2 block diagram.................................................................................105

11.3.5 Register map........................................................................................................105

11.3.6 Register description..............................................................................................106

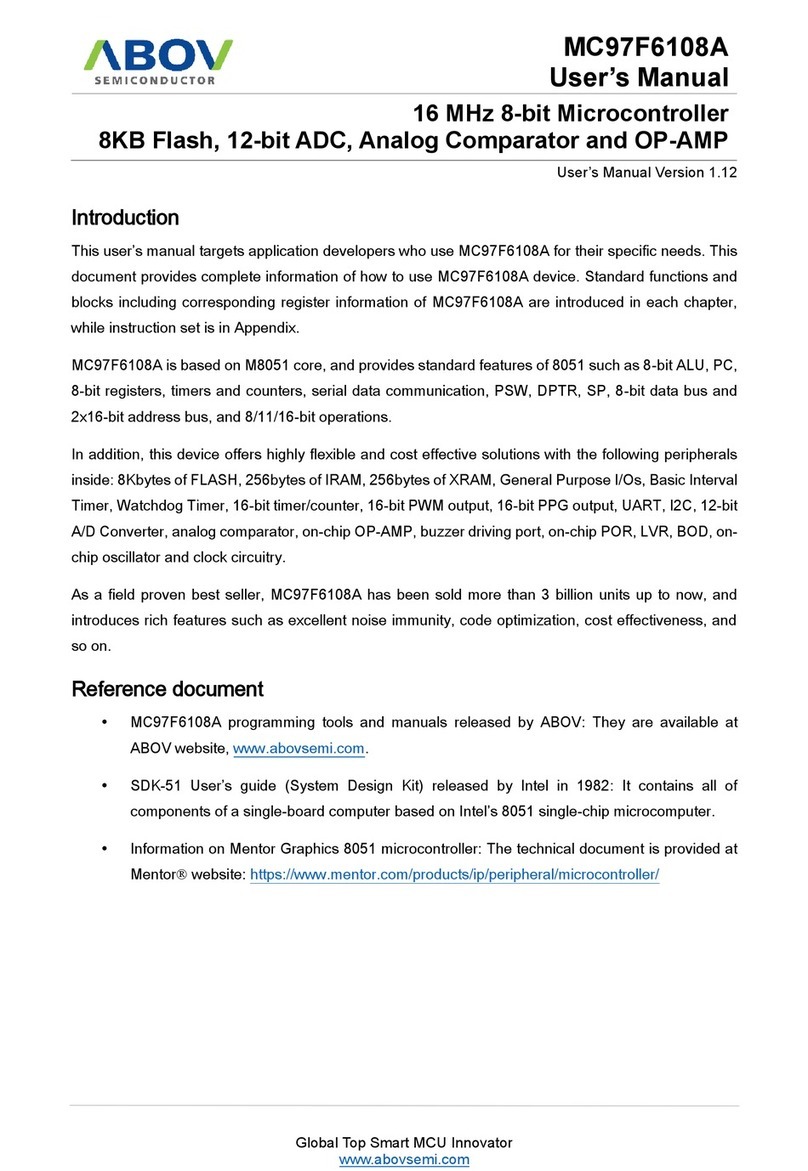

12 12-bit ADC..................................................................................................................................108

12.1 Conversion timing .............................................................................................................108

12.2 Block diagram ...................................................................................................................109