MC96FR116C

6 November, 2018 Rev.1.8

9.2 Register Description...................................................................................................................................49

10. Interrupt Controller.........................................................................................................................................55

10.1 Overview..................................................................................................................................................55

10.2 External Interrupt.....................................................................................................................................56

10.3 Block Diagram.........................................................................................................................................57

10.4 Interrupt Vectors......................................................................................................................................58

10.5 Interrupt Sequence ...................................................................................................................................58

10.6 Effective time of Interrupt Request..........................................................................................................59

10.7 Multiple Interrupts ...................................................................................................................................60

10.8 Interrupt Service Procedure .....................................................................................................................61

10.9 Generation of Branch Address to Interrupt Service Routine(ISR)...........................................................61

10.10 Saving and Restoring General Purpose Registers..................................................................................62

10.11 Interrupt Timing.....................................................................................................................................63

10.12 Interrupt Registers..................................................................................................................................63

11. Peripheral Units..............................................................................................................................................70

11.1 Clock Generator.......................................................................................................................................70

11.2 Basic Interval Timer (BIT) ......................................................................................................................72

11.3 Watch Dog Timer (WDT)........................................................................................................................75

11.4 TIMER/PWM ..........................................................................................................................................77

11.5 Watch Timer with event capture function (WT)....................................................................................106

11.6 IR Capture Control (IRCC)....................................................................................................................112

11.7 Carrier Generator...................................................................................................................................116

11.8 Key Scan................................................................................................................................................124

11.9 UART ....................................................................................................................................................127

11.10 I2C........................................................................................................................................................141

12. POWER MANAGEMENT ..........................................................................................................................158

12.1 Overview................................................................................................................................................158

12.2 PERIPHERAL OPERATION IN SLEEP/STOP/BOD MODE.............................................................158

12.3 SLEEP mode..........................................................................................................................................158

12.4 STOP mode............................................................................................................................................159

12.5 BOD mode.............................................................................................................................................161

12.6 Register Map..........................................................................................................................................164

12.7 Register Description...............................................................................................................................164

12.8 Power Sequence.....................................................................................................................................164

13. RESET..........................................................................................................................................................165

13.1 Overview................................................................................................................................................165

13.2 Reset source...........................................................................................................................................165

13.3 Block Diagram.......................................................................................................................................165

13.4 Noise Canceller for External Reset Pin..................................................................................................166

13.5 Power-On-RESET .................................................................................................................................166

13.6 External RESETB Input.........................................................................................................................168

13.7 Brown Out Detector...............................................................................................................................169

13.8 Register Map..........................................................................................................................................171

13.9 Register Description...............................................................................................................................171

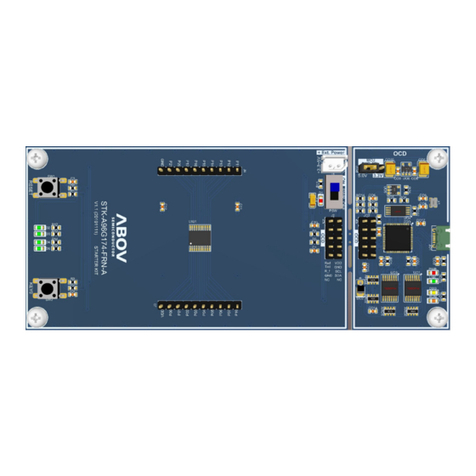

14. On-chip Debug System.................................................................................................................................174

14.1 Overview................................................................................................................................................174

14.2 Two-pin external interface.....................................................................................................................175

15. FLASH Memory Controller .........................................................................................................................179