3)

Hardware installation

3-1) Hardware installation procedure

There are three procedures for hardware installation.

CD

Perform

hardware

installation

during

user

diagnosis.

(2)

Press

ENTER

key

when

"Invalid

Configuration

Information"

error,

etc.

occurs.

(;ll Press CTRL +ALT+SET UP keys during setup operation.

3-2. Hardware installation

-0

Bisplay configuration

-{:;

Display mode: VGAlEGAlCGAlMDAlHGC

Used to

set

built-in VGA.

-(:;

Display adaptor: Internal

VGAlCGABO/CGA40/MDAlOthers

Used to

set

the display adaptor state when the expansion box

is

connected.

By

this setting, the display adaptor can

be

used

instead of the

built~in

VGA when the builHn VGA is

not

used

and

the

expansion

box

is

connected.

If the expansion box is not connected, the

built~in

VGA is used

regardless

of

this setting.

€)

Drive

assignment

-{:;

Drive

A:

OptionaI3.5"FDD External 5.25"FDD

-{:;

Drive B: External 5.25FDD" Optional 3.5"FDD

Used to

set

FDD assignment. When the expansion FDD is not

connected, the option FDD is assigned to Drive A regardless

of

this setting.

'"

Drive C: Internal HDD ROM disk

-{:;

Drive D: None Internal HDD

Used to set the internal

HOD

and ROM disk assignment and

to

set the booting drive assignmentwhen FD is not inserted.

o

1/0

configuration

Used to set hardware

1/0

port.

-{:;

Parallel Port: PORT1/PORT2/DISABLE

Used to

set

port address

of

the internal parallel port.

-{:;

Internal SIO Port: PORT1/PORT2/DISABLE

'"

Optional SIO Port: PORT1/PORT2IDISABLE

Used to set SIO port address.

-{:;

ROM disk

1/0

port: 1?BH

-1?BH

(?:O-F)

Used to set

1/0

port address used by the ROM disk.

ROM disk port address is effective even though ROM disk is

set to NONE.

ROM disk

110

port address

may

be changed to

pr~vent

butting

when a card is inserted into the expansion box.

-{:;

EMS

1/0

port: 2?BH -2?BH (?: either of

0,

1,4,

5,

6,

A,

B,

E)

EMS

1/0

port is effective even though EMS is not used.

EMS port address may

be

changed to prevent butting when a

card is inserted into the expansion box.

-7-

10

Memory configuration -

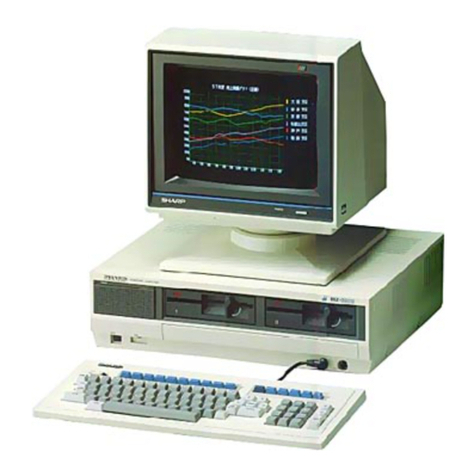

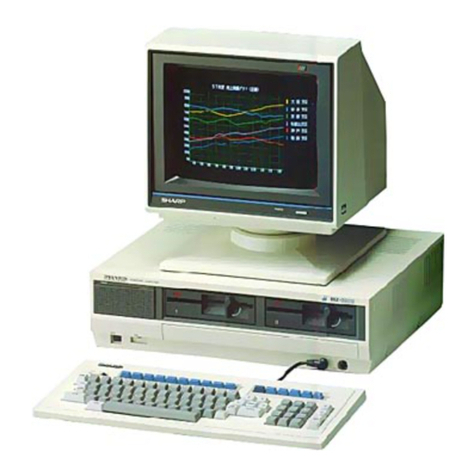

PC-6220

For memory setting, commercially available

memory

can

be

used

for

the expansion box. Therefore, the user must register the size

of

internal memory connected currently.

-{:;

Internal memory size: XX MB 1 -

3MB

The user must register the total size

of

Sharp memory.

Each memory capacity is assigned

and

displayed according

to

this total memory.

-{:;

Boundary address: XXXXXXXH

Used to set boundary of releasing memory address to the

expansion box. According to this -value,- the sizes

of

1

Mb

memory and EMS memoryare determined.

-{:;

With the above items,

the

following items are displayed.

o Main

memory:

640KB

Main memory capacity is displayed. It is fixed to 640KB.

o Extended memory: XXXXXX KB

(XX.x

MB)

The memory capacity

over

1

MB

is displayed. Memory in the

expansion box is not displayed. Only Sharp memory is dis-

played.

o Expandedmemory: XXXXXX KB (XX.X MB)

EMS memory capacity is displayed. Memory in the expansion

box is not displayed. Only Sharp memory is displayed.

o Disabled memory: XXXXX KB

Depending on the memory boundary

set

value, 256KB

memory maybe disabled.

4) Others

4-1) Default values

of

hardware installation and setup

To

reset parameters

of

hardware installation and setup

to

the default

values, press CTRL + SPACE keys. Then the displayed parameters

will

be

reset to their default values.

To

reset all the parameters, press

CTRL + SPACE keys for each of hardware installation and setup

screens. Data and Time, however, will

not

be reset

to

the default

values.

4-2) Starting

ROM

disk

Press CTRL + ALT + SETUP keys and periorm setup. While setup is

executed, press CTRL + ALT +SETUP keys again,

the

set

goes into

hardware installation.

Then set drive C to ROM disk, and drive D

to

hard disk, and start the

set again.

4-3)

When the screen is not clear

on

starting

The PC-6220 stores the pallet value on power off. Therefore, some

pallet value setting just before power off may result in unclear screen.

In

this case, press

Fn

+SETUP.