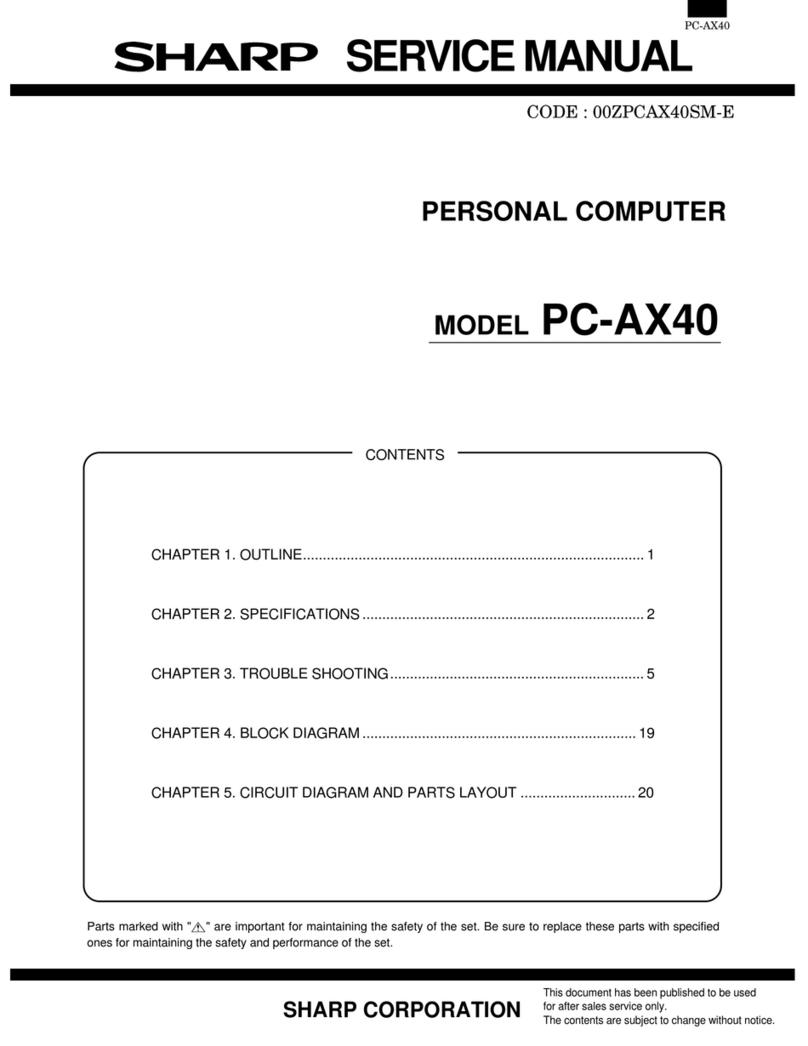

CONTENTS

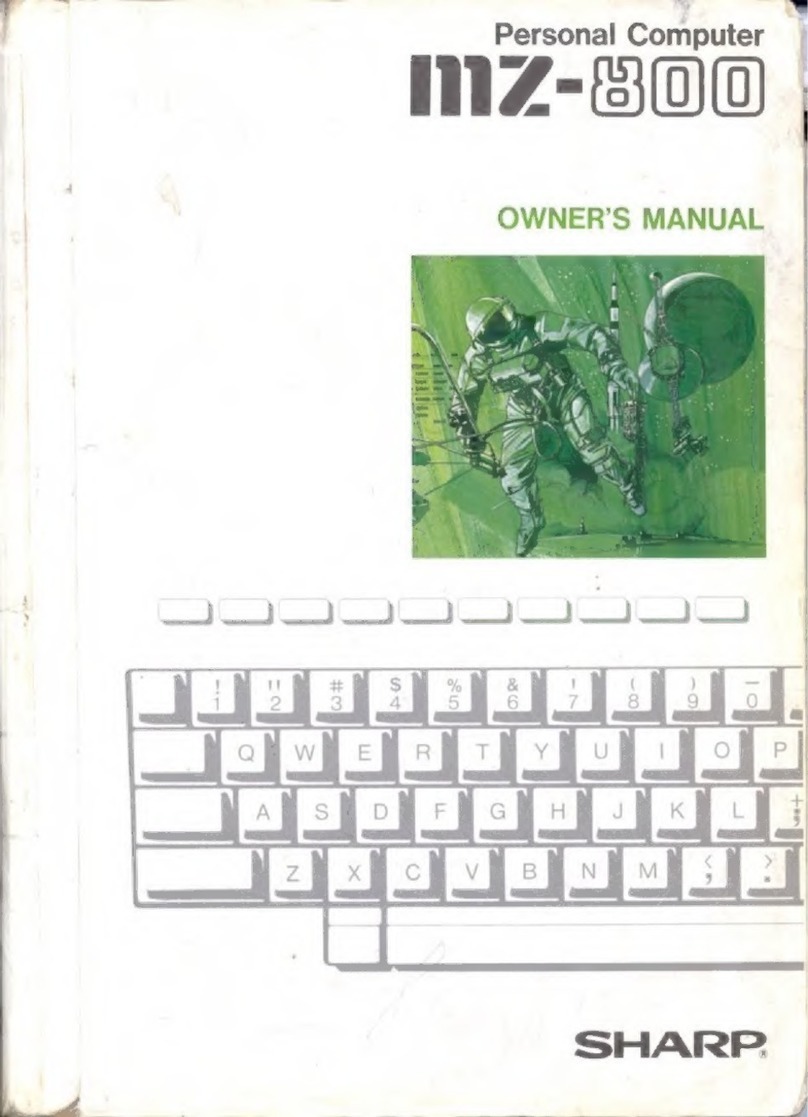

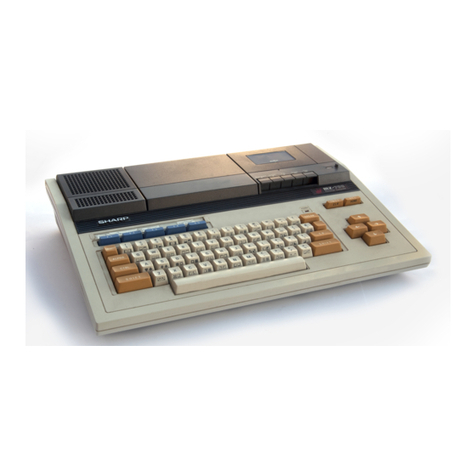

MZ-800

HARDWARE

1

System

description ······························ ························································· 1

2 Block

diagram

2

3

Memory

map

······

···············

·········

································································

·· 3

4

Custom

LSI

·•

···············································

·······

··········································· 6

4-1

Memory controller ····························································································· 6

4-2 1/0 controller ··································································································· 6

4-3 Clock generator

and

timing generator ···········.......................................···········

··

9

4-4 Display address generator ················································································· 9

4-5 Scroll ············

··

·············

··

··

··

········

··

···

··

············

··

·············

··

·····

··

·····

··

·······

··

······

··

···

10

4-6 VRAM data input/output circuit ·························

··

············································· 12

4-7 Register functions ···········································································-················· 17

4-8 Pallet ····································································································-···-·-· 22

4-9

CRTC

register map ··································-······················································· 23

4-10

ROM

configuration ··························································································

24

5

8255

Programmable

Peripheral Interface

.........................................................

24

6

8253

Programmable

Interval

Timer

·······················

·····

····················

..................

28

7

Printer

interface

··································································

···························

28

8

Programmable

sound generator

·····································································

31

9

Joystick

····

····················

·····

··

······

··

······

·····

····································

······

·········· 32

1

0

Power

supply ····························································································· 33

10-1 Block diagram ································································································ 33

10-2 Operational description ············-·····························-·········································

34

10-3 Maintenance ··································································································· 34

10-4 Problem determination

and

sequence

··································································

34

11

MZ-1P16

···································································································

35

11-1 Installation ······································································································ 35

11-2 Block· diagram ................................................................................................ 36

11-3 At power

on

··································································································· 36

11-4 Colour change operation ···················································································· 36

11-5

Pen

change operation ······················································································· 36

11-6

Pen

exchange method ······················································································· 37

11-7 Stepping motor driving signal ··········································································· 37

11-8 Colour position detector ···················································································· 37

11-9 Character set ···································································································

37

11-10 Colour plotter printer control

LSI

········································································

38

11-11 Interfacing with the MZ-800 ·············································································· 39

11-12 Block diagram ................................................................................................ 39

11-13 Colour plotter printer control

codes

·····································································

40

11-14 Graphic mode commands ·················································································

41

11-15 Specification ··································································································· 42

11-16 Circuit ············································································································ 42

12

CPU P.W.B. Circuit

·······················································································

43

ii