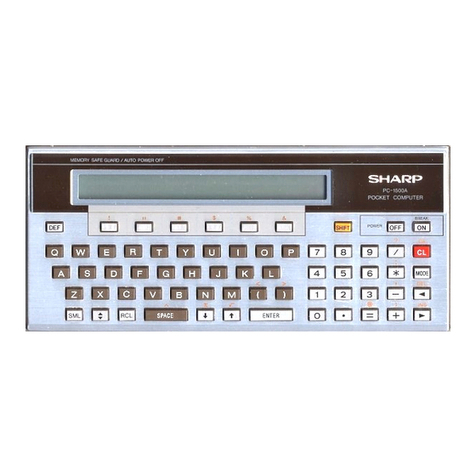

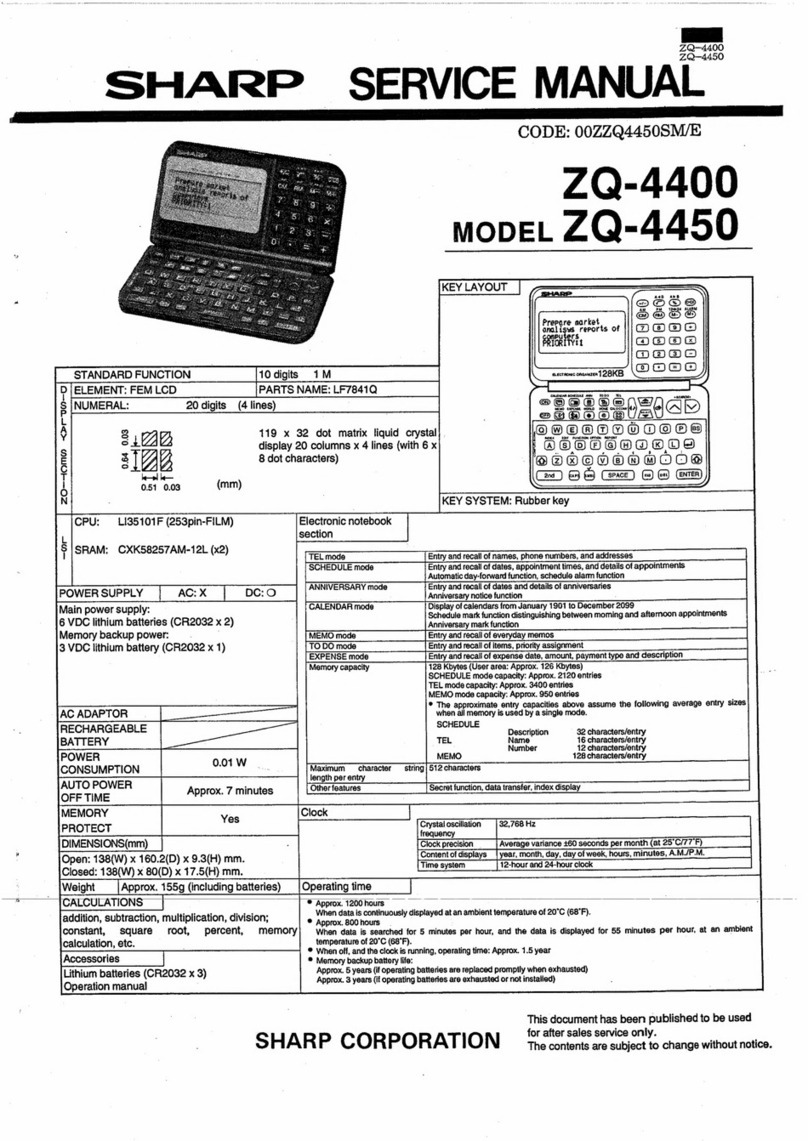

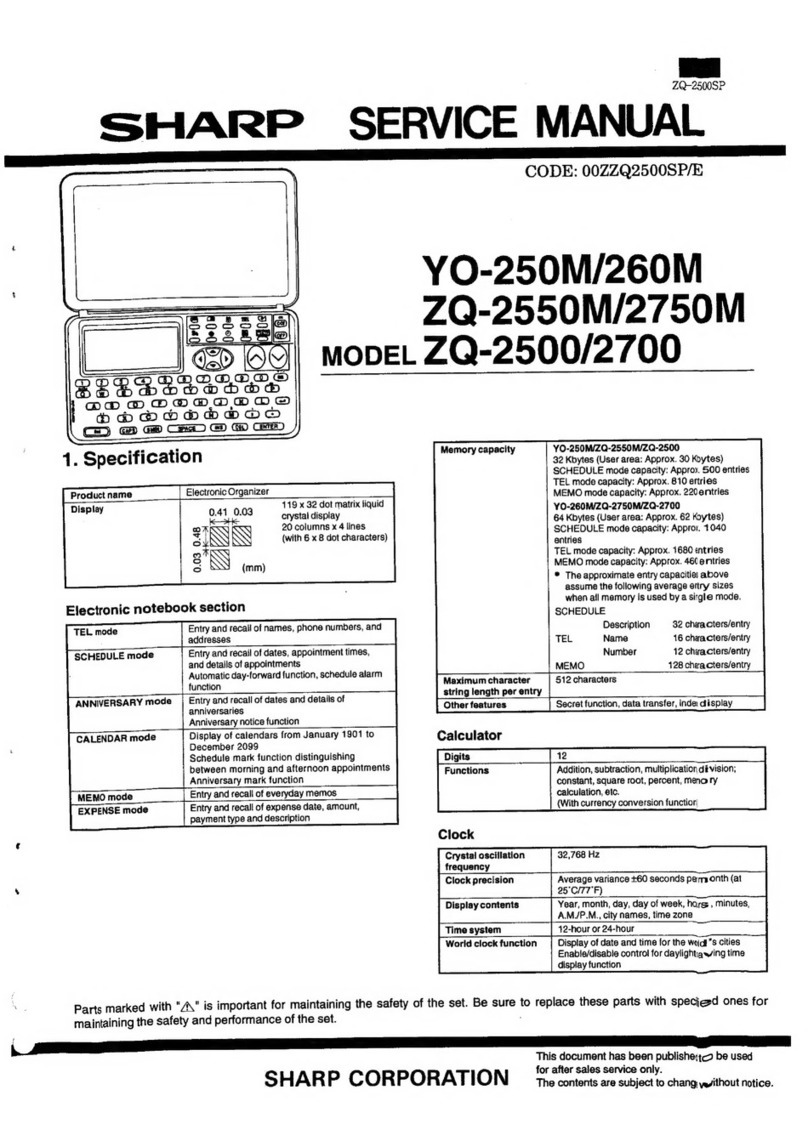

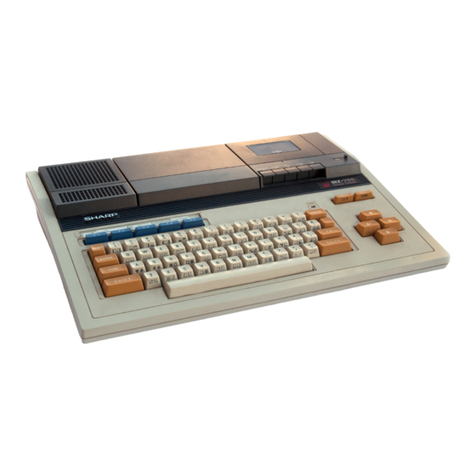

SHARP

SERVICE MANUAL

CODE:

OOZMZ8OOIIIIE

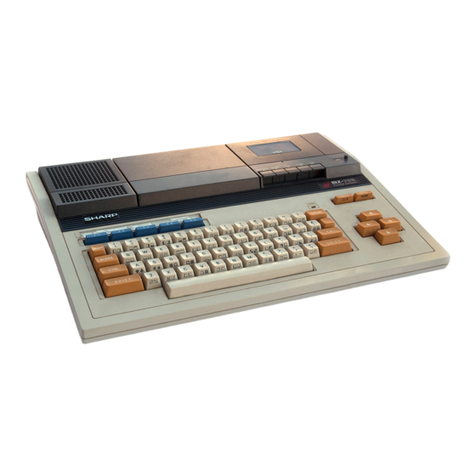

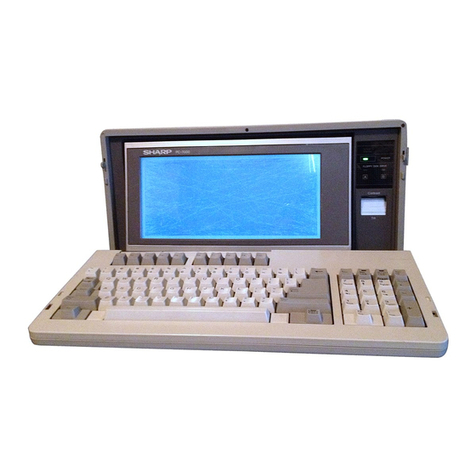

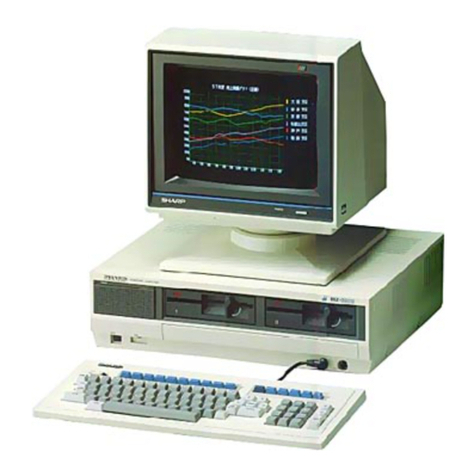

PERSONAL COMPUTER

MODEL

MZ-800

MZ-1P16

MZ-1E20

Table of contents

t,

Specification

..

2.

Parts identification

..

3.

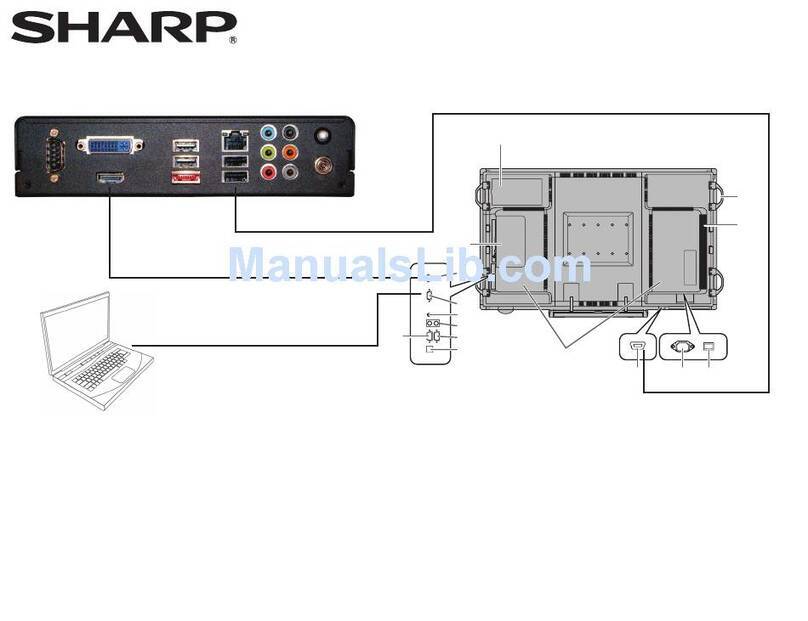

Systemdiegram

..

4.

Systemdescriplion

..

4·',

Memorymep

..

4-2.

CustomLSI

.....

4-2-1.

Memoryconlroller

...

4-2-2.

VOcontroller

..

4-2-3. Clock generator end

timing

generator

..

4-2-4. Display address generator

...

4-2-5. Scroll control circuit .....

..................................... 4

................................................... 6

..

9

9

9

.

.......................

12

.. ......... 12

..

.....

13

. ......................................... 15

4·2·6. VRAMdeta

inputloutpulcircuil

..

4-2-7. Register functions

....

.............................................................. 20

4-2-8. Pal1etcircuit .....

..

...........

25

4-2-9.

CRTC

register

map

•.

.

................................

26

4-2-10.

ROMconfigufation

...

............................................... 27

4-3. 8255 Programmable Peripheral Interface

...

4-4. 8253 Programmable Interval

Timer

..

.........

................................ 27

..

......

31

4-5. Printer interface

..

4-6. Programmable sound generator

.•

4-7. Joystick

..

4-8.Systemswitchsetups

...

5.

Powersupply

.....

MZ-1P16

.....

. ..................................................

31

.................................................................. 34

.........

35

. .....................................................

35

..

......................................................... 35

. ...................................................

35

SHARP CORPORATION