Sharp MZ-3500 User manual

Other Sharp Desktop manuals

Sharp

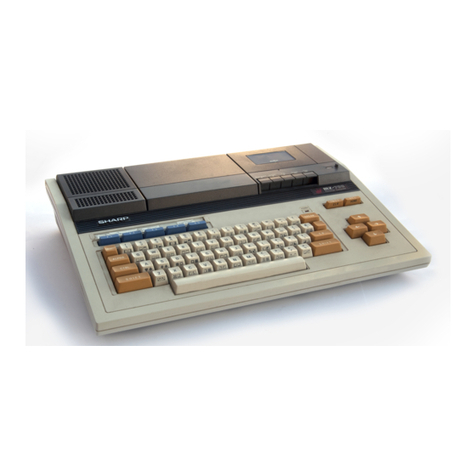

Sharp MZ-700 Series User manual

Sharp

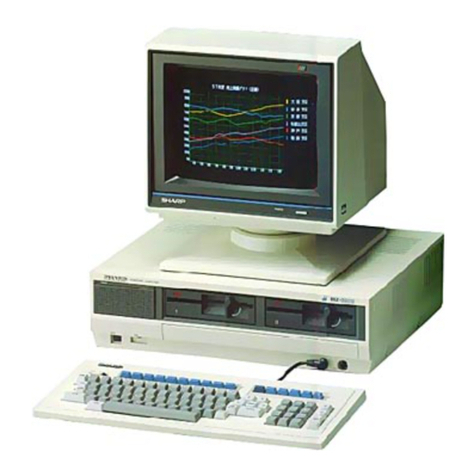

Sharp MZ-3500 User manual

Sharp

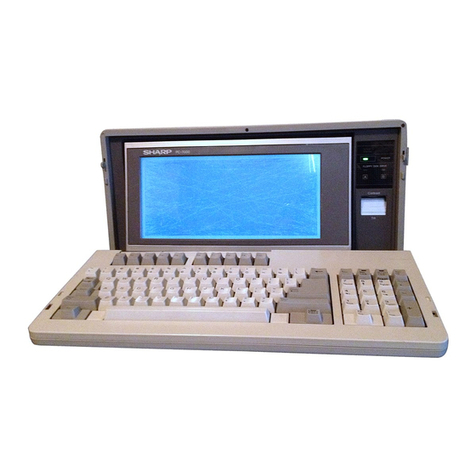

Sharp PC-6220 User manual

Sharp

Sharp MZ-800 User manual

Sharp

Sharp ZQ-3000 User manual

Sharp

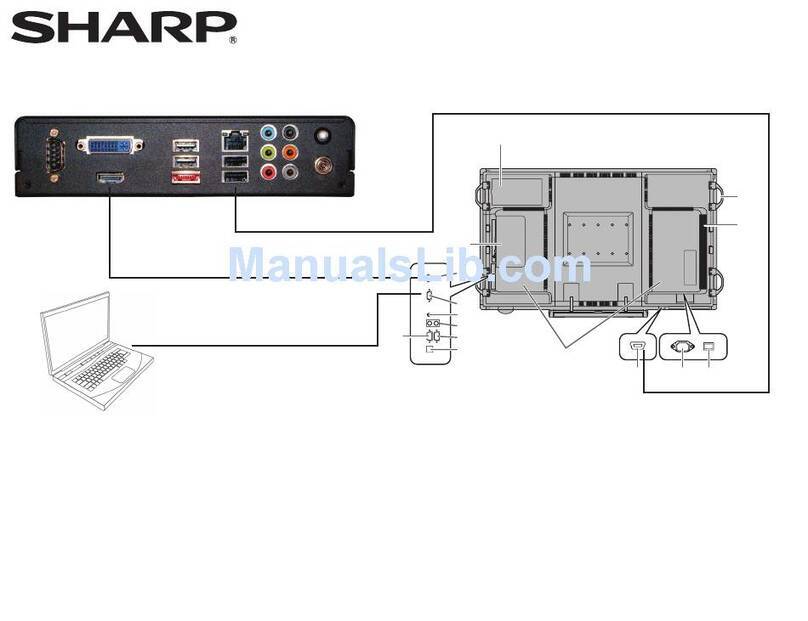

Sharp PN-L602B User manual

Sharp

Sharp PN-TPCi7W7 User manual

Sharp

Sharp PN-TPC1W User manual

Sharp

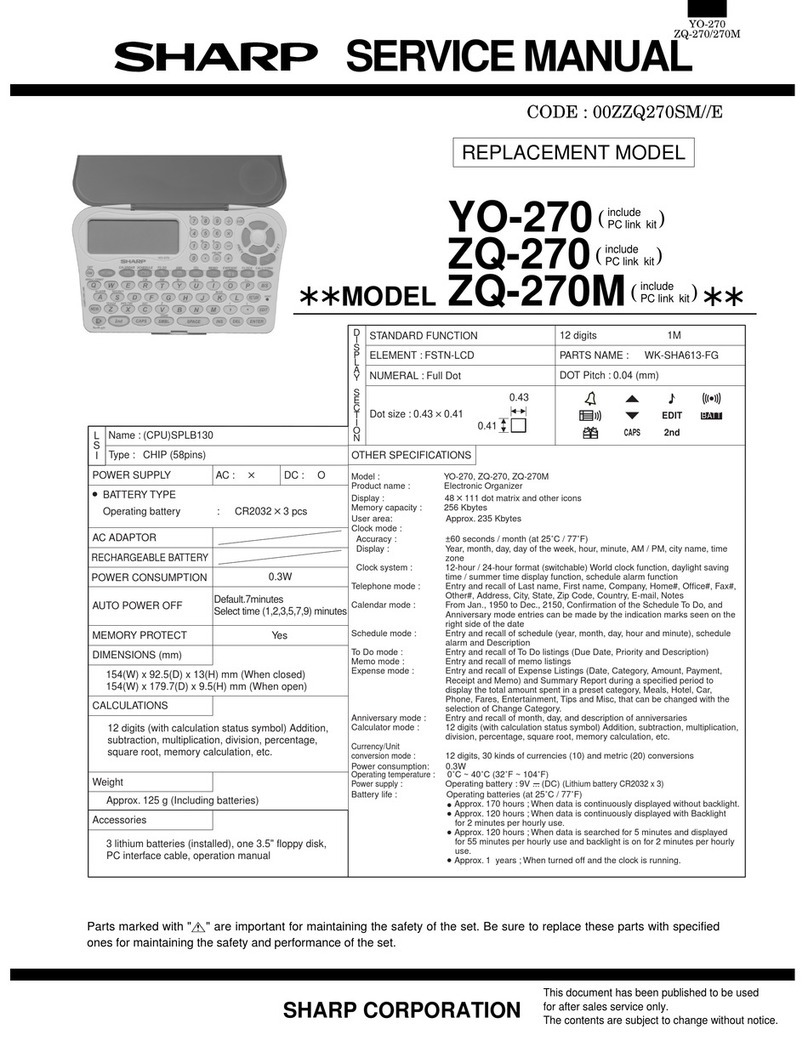

Sharp YO-270 User manual

Sharp

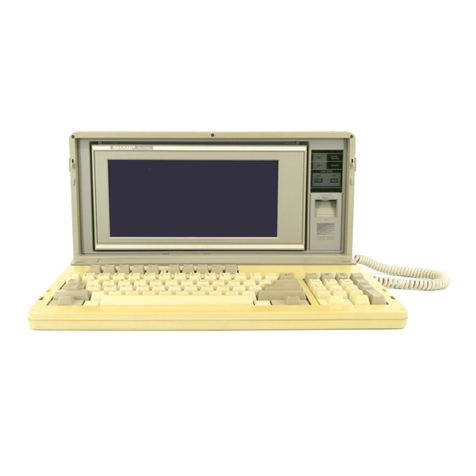

Sharp PC7000A User manual

Sharp

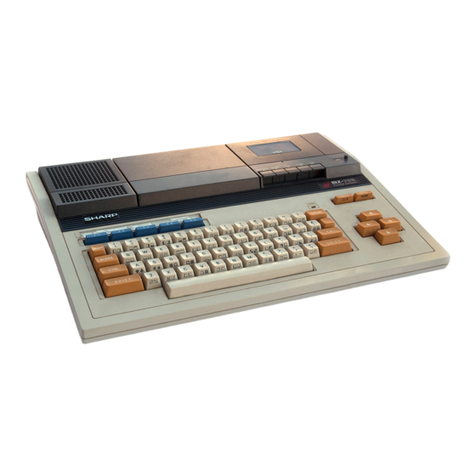

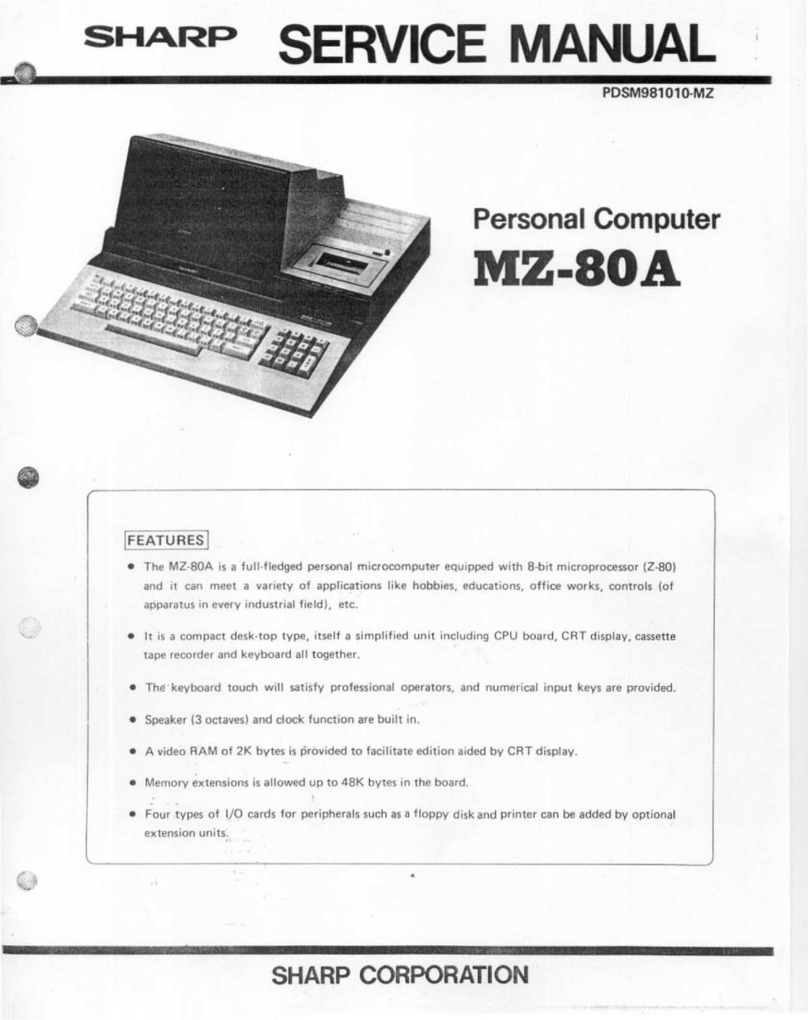

Sharp MZ-80A User manual

Sharp

Sharp ZQ-4450M User manual

Sharp

Sharp MZ-80B User manual

Sharp

Sharp PC-AX40 User manual

Sharp

Sharp MZ-80B User manual

Sharp

Sharp SCR3042FB User manual

Sharp

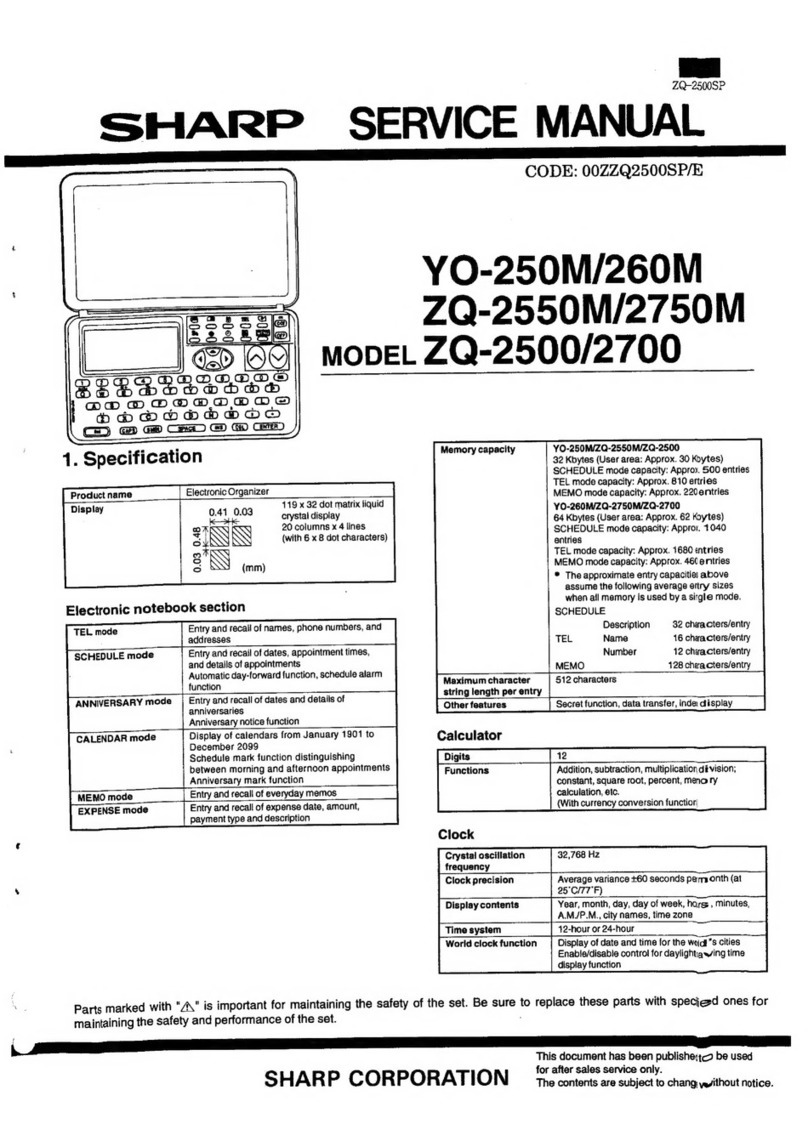

Sharp YO-250M User manual

Sharp

Sharp PN-L602B Instruction Manual

Sharp

Sharp PC-7200 User manual

Sharp

Sharp MZ-700 Series User manual