\

""'

'I

J

'It

l

')

-.

•

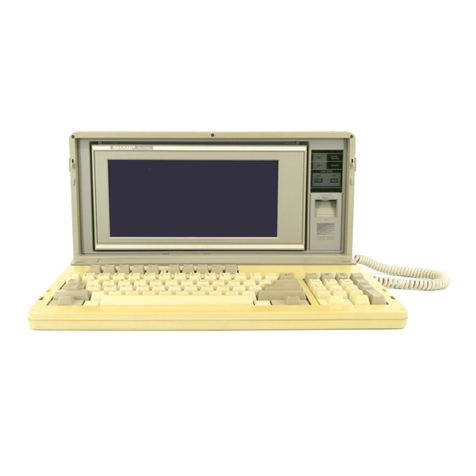

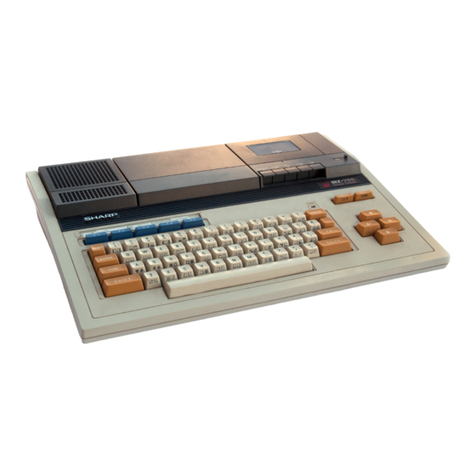

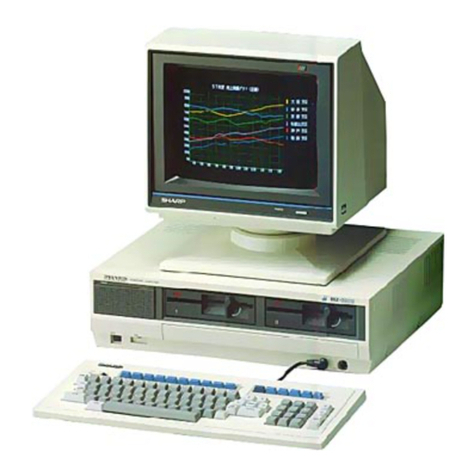

MZ-3500

SHARP

SERVICE

MANUAL

CODE:

OOZMZ

3500SM/E

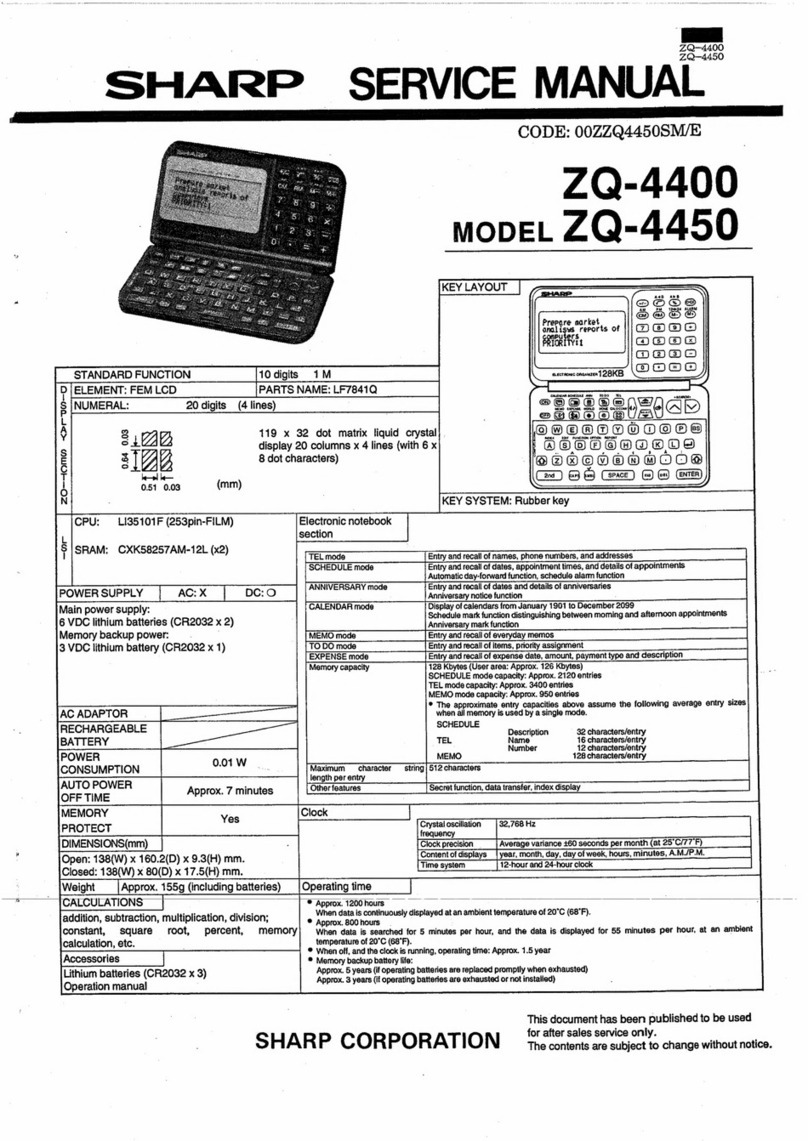

PERSONAL

COMPUTER

MODEL

MZ-3500

-------------CONTENTS

-------------..,

1. Specifications . . . . . . . . . . . . . . . . . . . . . • . . . . . . . • . • . . . • • • . . • . . . • • • • • • • • • • • . . .

..

1

2. Software (Memory) Configuration

..............•....................•..........

7

3.

CPU

and memory

...........................................•..•.•........

12

4. CRT

display.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . • . . . . . • . . • • • . . . . . . . . . . . . • . . . .

..

25

5.

MFD

interface

..................................•.....•.....•....•.......

52

6. R232C interface

......

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . • . . . . . . • . . . . . . . . . .

..

72

7. Printer interface

.......................................•.....•............

78

8. Other interface . . . . . . . . .

..

..,

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . • . .

..

81

9. Power circuit discnption . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . • . . . . . . . . .

..

87

10. Keyboard controller circuit discriptlOn . . . . . . . . . . . . . . . . . . . • . . . . . • . . . . • . • • . . • . . . .

..

90

11. Self check

functions.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

..

94

12. IPL flow chart

...........................................................

103

13. Circuit diagram & P.W.S

Parts list & Guide

SHARP

CORPORATION