CHAPTER

1.

graphic character fonts.

• Standard 640K·byte O·RAM. -

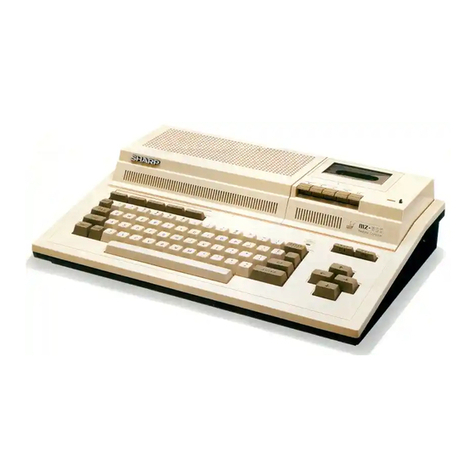

PC-7200

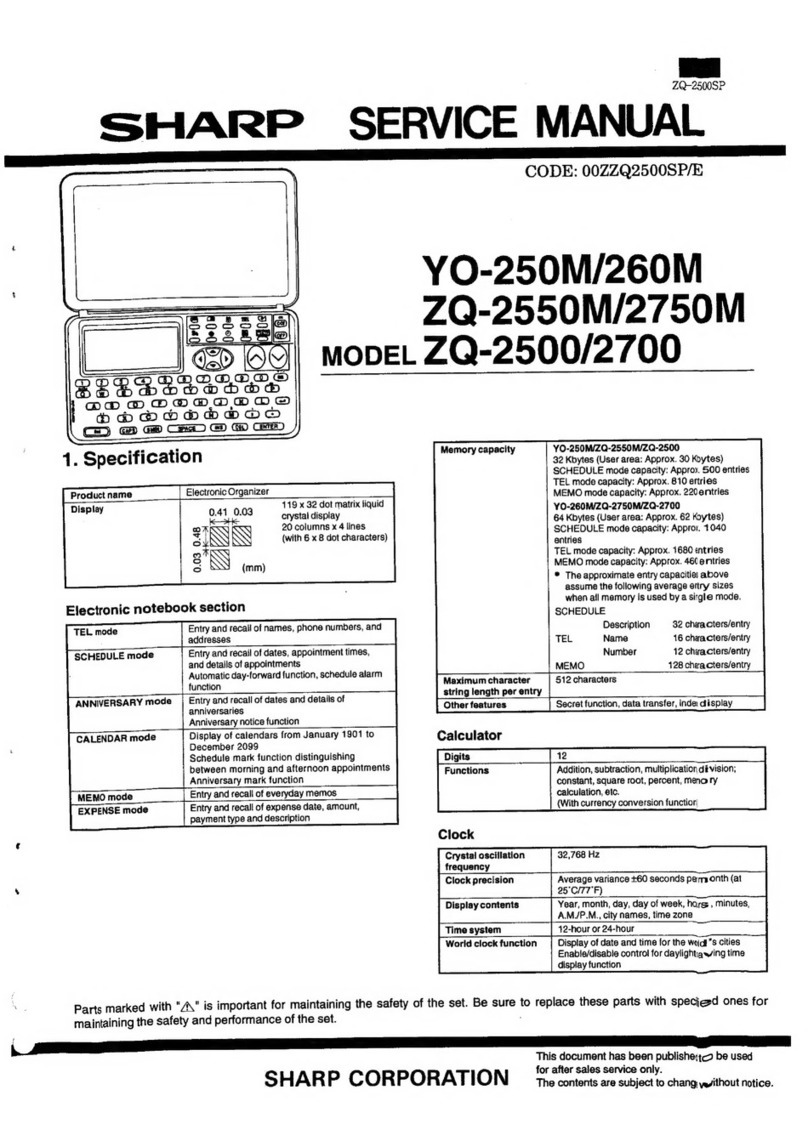

SVST-EM-SP-E-GlF-ICAT-ION~-

1-1. FEATURES

----

--.

-Reaf-time--eleek-{-R:r.c}...which storss-Jnformatioo related to the

The

PC~7200,

provided with numerous special features and

functions, can be used as a single·user or multi-user computer. It

is a powerlul office tool that can satisfy the diverse demands for

high-speed data processing and large-scale memory management

for

the

high-end personal computer

and

low-end multi-user

configuration.

80286 Microprocessor

The computer's central processing unit (CPU) has an 10MHz i6-bit

80286 microprocessor, permitting upward compatibility with 6088/

8086 processor operation. It performs versatile data processing at

a faster speed than the 8088/8086 processors.

Memory

The computer has 640K bytes of Random Access Memory (RAM)

and 64K bytes of system Read Only Memory (ROM). ROM contains

IPL, BIOS, and diagnostic programs as well as graphics character

fonts.

LCD

Display

A large-capacity LCD with 640x 200 pixel configuration.

Features a backlight and adjustable tilt feature for better visibility.

Built-in Interfaces

For the input/output

of

data to and from the computer, various

peripherals have been provided, including a

5-114",

high-density

floppy disk drive, a built-in 20M byte hard disk and hard diskcontroller

(PC-7221 only), and a RS-232C interfaces, and a Centronics-com-

patible printer interface.

Functional Expandability

Besides the standard features above, the functions

of

the computer

can be expanded by mounting optional devices such as the 80287

Numeric Processor Extension, or by installing any of various option

boards in the internal options slots.

Modem Card

Designed exclusively for the PC-7200, and directly attaches to the

main board.

Operating System

A DOS (Disk Operati,ng System) allows the user to communicate

with the computer and its peripheral devices, performing data

transfer and managing the memory resources of the various

equipment.

In

the single-user system configuration

of

DOS, MS-DOS version

3.2 is used. This version permits use of a wide range of commercially

available application programs. The computer can also be run under

XENIX 286 Version (multi-user configuration) and GW-BASIC,

version 3.2.

IBM Compatibility

Most of the application software, peripherals and options designed

for the IBM PC,

Xl,

and

AT

can also be used with the PC-7200.

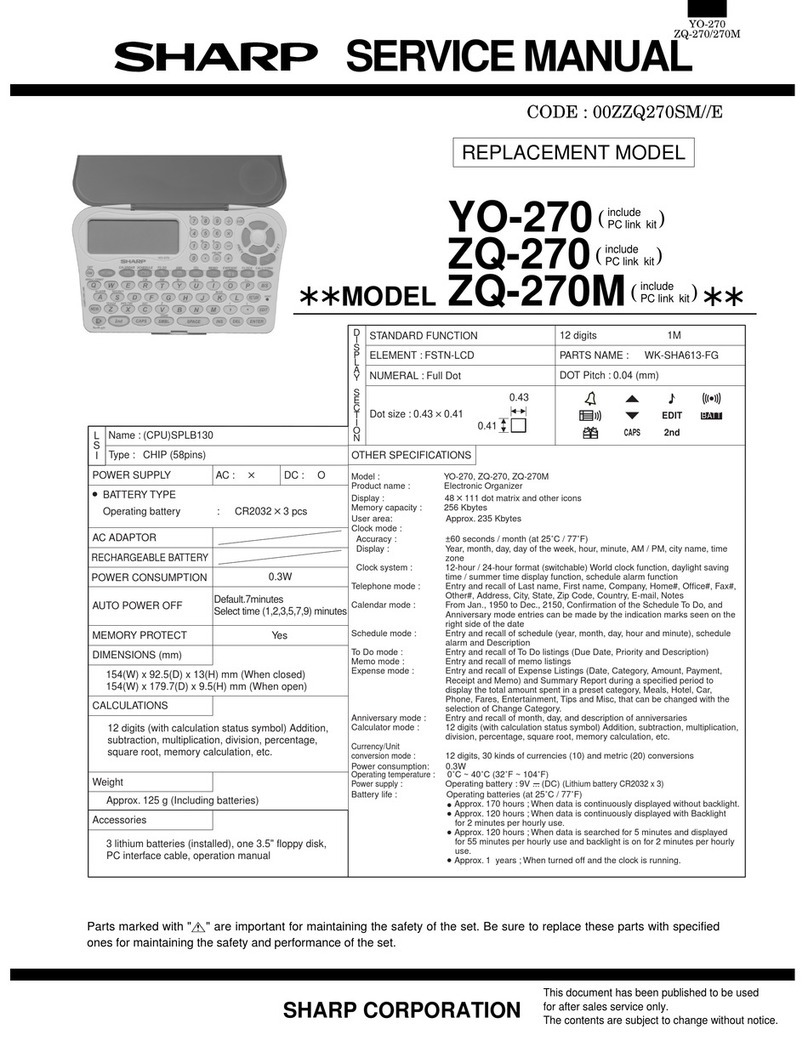

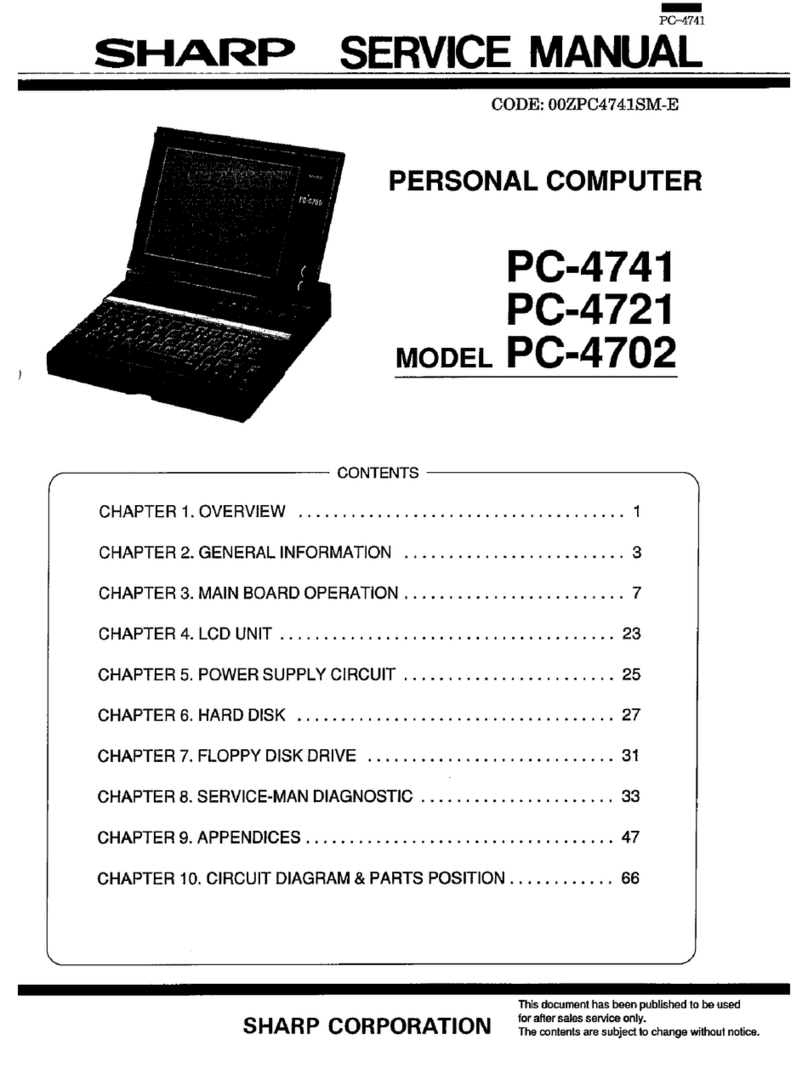

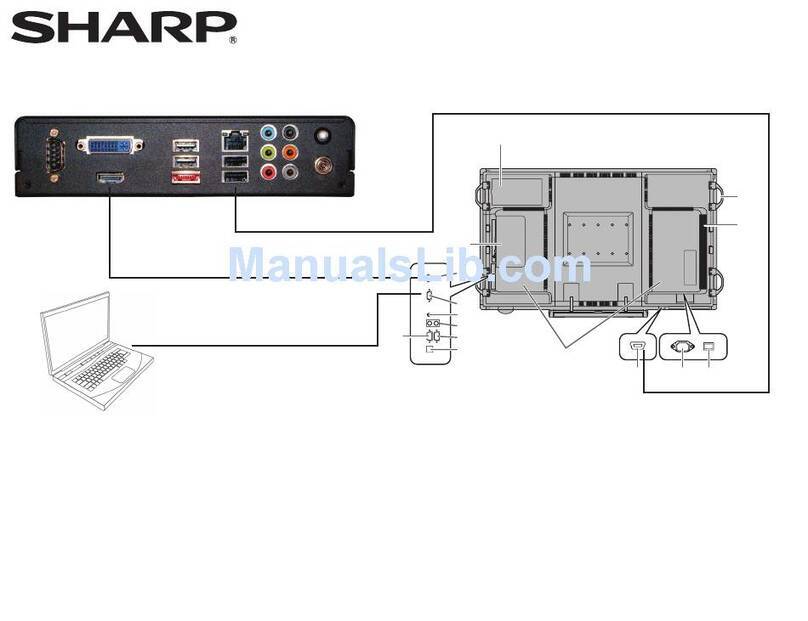

1-2. SYSTEM CONFIGURATION

Figure

1-1

illustrates system architecture. As demonstrate, the

system's main components include thesystem unitand the keyboard

unit.

The system unit includes the main PCB, floppy disk drive, hard disk

drive (PC7221 only), and optional adapter.

The System Unit

The main PCB is composed of the following components:

• 80286 16-bit microprocessor

• Control Circuits

• 64K-byte (two

32

byte chips) ROM which contains the power-on

diagnostic program, BIOS, initial program loader (IPL), and

1

~

1

system configuration and updates the date and time even if the

computer power

is

turned off.

• Keyboard interface

• Centronics-compatible parallel printer interface

• Floppy disk interface which can control up to

two

double-density

(20)

or high·capacity (2HO) floppy disk rives.

• Asynchronous serial interface which conforms to the EIA

RS·232C standard.

• One options slots-This slotcan use both IBM

PC/XT

compatible,

B·bit type. and IBM AT compatible, 16·bit type.

• A large-capacity LCD with

640x200

pixel configuration, as a

standard feature.

• Modem card designed exclusively for the PC-7200 directly

attaches to the main unit as

an

optional device.

A high density (2HD) floppy disk drive is installed as a standard

feature.

Mounted

at

the center

of

the chassis is a 3.5 inch hard disk drive

with storage capacity

of

20M~bytes.

The power supply unit has six levels

of

power output:

+5V,

-5V,

+12V,

-12V,

-15V

and AC120V. Because these voltages are

stabilized with

the

switching regulator,

the

power supply takes less

space and is light in weight.

Inside the system unit, there is a Ni-Cd battery. This battery backs

up the real time clock, permitting it to maintain information related

to the system configuration, and to update the date and time, even

when the power is down.

SYSTEM CONFIGURATION

<

SYSTEM

u'~"CC"':....

___

~=====,--;~~-:-:

I

'.

__

•••

;1

. .

: 80287 :

L_~

_ow,

.

~

4.61'115: ',,"0"1"

~

,",e,.

0,

r===;:~~$~~:;===1

IBM

CARD

[

2"

16

b"

lull

size slots

1 " 8 bit

lull

size sici

L_-'

__

...l.

__

.L_....J

1"

8

bU

hall

size

slCI

Figure

1-1

The Keyboard Unit

The keyboard is connected to the system unitusing a 6-Pin Modular

jack connector with a coiled cable. A one chip microprocessor is

used as an interface with the keyboard unit and

the

system unit.

When the power

of

the system unit is turned on, the processor

automatically checks its

own

RAM and ROM

by

executing

the

self-diagnostic program.