SONIX SN8P26L38 User manual

SN8P26L38

8-Bit Micro-Controller

SONiX TECHNOLOGY CO., LTD Page 1 Version 1.5

SN8P26L38

USER’S MANUAL

Version 1.5

SN8P26L38

S

SO

ON

Ni

iX

X

8

8-

-B

Bi

it

t

M

Mi

ic

cr

ro

o-

-C

Co

on

nt

tr

ro

ol

ll

le

er

r

SONIX reserves the right to make change without further notice to any products herein to improve reliability, function or design. SONIX does not

assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent

rights nor the rights of others. SONIX products are not designed, intended, or authorized for us as components in systems intended, for surgical

implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SONIX product

could create a situation where personal injury or death may occur. Should Buyer purchase or use SONIX products for any such unintended or

unauthorized application. Buyer shall indemnify and hold SONIX and its officers, employees, subsidiaries, affiliates and distributors harmless against

all claims, cost, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death

associated with such unintended or unauthorized use even if such claim alleges that SONIX was negligent regarding the design or manufacture of

the part.

SN8P26L38

8-Bit Micro-Controller

SONiX TECHNOLOGY CO., LTD Page 2 Version 1.5

AMENDMENT HISTORY

Version

Date

Description

VER 0.1

Dec. 2007

First Issue.

VER 0.2

Jan. 2008

Modify system register table.

VER 0.3

Feb. 2008

Modify internal low RC frequency to 10KHz.

VER 0.4

Otc. 2008

Add SN8P26L38F LQFP package type.

VER 1.0

Aug. 2009

Modify comparator pin assignment description.

VER 1.1

Jun. 2010

1. Modify UART baud rate description.

2. Modify IR register name.

3. Modify SYSTEM REGISTER TABLE.

VER 1.2

Feb. 2013

Modify LQFP package type marking definition.

VER 1.3

Apr. 2013

Add RAM limited:

The 1E6H, 1E7H of RAM address doesn’t support directly addressing mode to

access RAM but support indirectly addressing mode @HL/@YZ.

VER 1.4

Aug. 2013

Modify “SIO chapter”SCK frequency formula and description.

VER 1.5

Jan. 2019

Delete SSOP48 package.

SN8P26L38

8-Bit Micro-Controller

SONiX TECHNOLOGY CO., LTD Page 3 Version 1.5

Table of Content

AMENDMENT HISTORY............................................................................................................................ 2

1 PRODUCT OVERVIEW.............................................................................................................................. 8

1.1 FEATURES.............................................................................................................................................. 8

1.2 SYSTEM BLOCK DIAGRAM ................................................................................................................ 9

1.3 PIN ASSIGNMENT ............................................................................................................................... 10

1.4 PIN DESCRIPTIONS............................................................................................................................. 11

1.5 PIN CIRCUIT DIAGRAMS................................................................................................................... 12

2 CENTRAL PROCESSOR UNIT (CPU) ................................................................................................... 14

2.1 PROGRAM MEMORY (ROM) ............................................................................................................. 14

2.1.1 RESET VECTOR(0000H)................................................................................................................ 15

2.1.2 INTERRUPT VECTOR(0008H) ...................................................................................................... 16

2.1.3 LOOK-UP TABLE DESCRIPTION................................................................................................. 18

2.1.4 JUMP TABLE DESCRIPTION........................................................................................................ 20

2.1.5 CHECKSUM CALCULATION........................................................................................................ 22

2.2 DATA MEMORY (RAM)...................................................................................................................... 23

2.2.1 SYSTEM REGISTER........................................................................................................................ 24

2.2.1.1 SYSTEM REGISTER TABLE ................................................................................................ 24

2.2.1.2 SYSTEM REGISTER DESCRIPTION ................................................................................... 24

2.2.1.3 BIT DEFINITION of SYSTEM REGISTER........................................................................... 25

2.2.2 ACCUMULATOR............................................................................................................................ 27

2.2.3 PROGRAM FLAG ........................................................................................................................... 28

2.2.4 PROGRAM COUNTER................................................................................................................... 29

2.2.5 H, L REGISTERS............................................................................................................................. 32

2.2.6 Y, Z REGISTERS.............................................................................................................................. 33

2.2.7 R REGISTERS.................................................................................................................................. 34

2.3 ADDRESSING MODE........................................................................................................................... 35

2.3.1 IMMEDIATE ADDRESSING MODE.............................................................................................. 35

2.3.2 DIRECTLY ADDRESSING MODE................................................................................................. 35

2.3.3 INDIRECTLY ADDRESSING MODE............................................................................................. 35

2.4 STACK OPERATION............................................................................................................................ 36

2.4.1 OVERVIEW ..................................................................................................................................... 36

2.4.2 STACK REGISTERS........................................................................................................................ 37

2.4.3 STACK OPERATION EXAMPLE.................................................................................................... 38

2.5 CODE OPTION TABLE ........................................................................................................................ 39

2.5.1 RESET_PIN CODE OPTION.......................................................................................................... 39

2.5.2 SECURITY CODE OPTION............................................................................................................ 39

SN8P26L38

8-Bit Micro-Controller

SONiX TECHNOLOGY CO., LTD Page 4 Version 1.5

3 RESET.......................................................................................................................................................... 40

3.1 OVERVIEW........................................................................................................................................... 40

3.2 POWER ON RESET............................................................................................................................... 41

3.3 WATCHDOG RESET............................................................................................................................ 41

3.4 BROWN OUT RESET ........................................................................................................................... 42

3.4.1 THE SYSTEM OPERATING VOLTAGE......................................................................................... 43

3.4.2 LOW VOLTAGE DETECTOR (LVD).............................................................................................. 43

3.4.3 BROWN OUT RESET IMPROVEMENT......................................................................................... 45

3.5 EXTERNAL RESET .............................................................................................................................. 46

3.6 EXTERNAL RESET CIRCUIT ............................................................................................................. 46

3.6.1 Simply RC Reset Circuit.................................................................................................................. 46

3.6.2 Diode & RC Reset Circuit............................................................................................................... 47

3.6.3 Zener Diode Reset Circuit............................................................................................................... 47

3.6.4 Voltage Bias Reset Circuit............................................................................................................... 48

3.6.5 External Reset IC............................................................................................................................. 49

4 SYSTEM CLOCK....................................................................................................................................... 50

4.1 OVERVIEW........................................................................................................................................... 50

4.2 CLOCK BLOCK DIAGRAM................................................................................................................. 50

4.3 FCPU (INSTRUCTION CYCLE)............................................................................................................ 50

4.4 OSCM REGISTER................................................................................................................................. 51

4.5 SYSTEM HIGH CLOCK ....................................................................................................................... 51

4.6 INTERNAL HIGH RC ........................................................................................................................... 52

4.7 EXTERNAL HIGH CLOCK.................................................................................................................. 52

4.7.1 CRYSTAL/CERAMIC....................................................................................................................... 53

4.7.2 RC.................................................................................................................................................... 53

4.7.3 EXTERNAL CLOCK SIGNAL......................................................................................................... 54

4.8 SYSTEM LOW CLOCK ........................................................................................................................ 55

4.8.1 SYSTEM CLOCK MEASUREMENT ............................................................................................... 55

5 SYSTEM OPERATION MODE................................................................................................................ 56

5.1 OVERVIEW........................................................................................................................................... 56

5.2 NORMAL MODE................................................................................................................................... 57

5.3 SLOW MODE......................................................................................................................................... 57

5.4 POWER DOWN MDOE......................................................................................................................... 57

5.5 GREEN MODE....................................................................................................................................... 58

5.6 OPERATING MODE CONTROL MACRO.......................................................................................... 58

5.7 WAKEUP ............................................................................................................................................... 60

5.7.1 OVERVIEW ..................................................................................................................................... 60

5.7.2 WAKEUP TIME............................................................................................................................... 60

SN8P26L38

8-Bit Micro-Controller

SONiX TECHNOLOGY CO., LTD Page 5 Version 1.5

5.7.3 P1W WAKEUP CONTROL REGISTER.......................................................................................... 61

6 INTERRUPT................................................................................................................................................ 62

6.1 OVERVIEW........................................................................................................................................... 62

6.2 INTEN INTERRUPT ENABLE REGISTER......................................................................................... 63

6.3 INTRQ INTERRUPT REQUEST REGISTER....................................................................................... 64

6.4 GIE GLOBAL INTERRUPT OPERATION .......................................................................................... 65

6.5 PUSH, POP ROUTINE........................................................................................................................... 66

6.6 EXTERNAL INTERRUPT OPERATION (INT0)................................................................................. 67

6.7 INT1 (P0.1) INTERRUPT OPERATION............................................................................................... 68

6.8 T0 INTERRUPT OPERATION.............................................................................................................. 69

6.9 T1 INTERRUPT OPERATION.............................................................................................................. 71

6.10 TC1 INTERRUPT OPERATION......................................................................................................... 72

6.11 COMPARATOR INTERRUPT OPERATION (CMP0, CMP1).......................................................... 73

6.12 SIO INTERRUPT OPERATION.......................................................................................................... 74

6.13 UART INTERRUPT OPERATION ..................................................................................................... 75

6.14 MULTI-INTERRUPT OPERATION................................................................................................... 76

7 I/O PORT ..................................................................................................................................................... 77

7.1 OVERVIEW........................................................................................................................................... 77

7.2 I/O PORT MODE ................................................................................................................................... 78

7.3 I/O PULL UP REGISTER ...................................................................................................................... 79

7.4 I/O OPEN-DRAIN REGISTER.............................................................................................................. 80

7.5 I/O PORT DATA REGISTER ................................................................................................................ 82

8 TIMERS ....................................................................................................................................................... 83

8.1 WATCHDOG TIMER............................................................................................................................ 83

8.2 TIMER 0(T0) ......................................................................................................................................... 85

8.2.1 OVERVIEW ..................................................................................................................................... 85

8.2.2 T0M MODE REGISTER.................................................................................................................. 86

8.2.3 T0C COUNTING REGISTER.......................................................................................................... 87

8.2.4 T0 TIMER OPERATION SEQUENCE............................................................................................ 88

8.3 TIMER 1(T1) ......................................................................................................................................... 89

8.3.1 OVERVIEW ..................................................................................................................................... 89

8.3.2 T1M MODE REGISTER.................................................................................................................. 89

8.3.3 T1CH, T1CL COUNTING REGISTER............................................................................................ 90

8.3.4 T1 TIMER OPERATION SEQUENCE............................................................................................ 92

8.4 TIMER/COUNTER 0(TC1)................................................................................................................... 93

8.4.1 OVERVIEW ..................................................................................................................................... 93

8.4.2 TC1M MODE REGISTER............................................................................................................... 94

8.4.3 TC1C COUNTING REGISTER....................................................................................................... 95

SN8P26L38

8-Bit Micro-Controller

SONiX TECHNOLOGY CO., LTD Page 6 Version 1.5

8.4.4 TC1R AUTO-LOAD REGISTER ..................................................................................................... 96

8.4.5 TC1 CLOCK FREQUENCY OUTPUT (BUZZER)......................................................................... 97

8.4.6 TC1 TIMER OPERATION SEQUENCE ......................................................................................... 98

8.5 PWM1 MODE ........................................................................................................................................ 99

8.5.1 OVERVIEW ..................................................................................................................................... 99

8.5.2 TC1IRQ AND PWM DUTY ........................................................................................................... 100

8.5.3 PWM PROGRAM EXAMPLE ....................................................................................................... 101

8.5.4 PWM1 DUTY CHANGING NOTICE............................................................................................ 102

9 ANALOG COMPARATOR..................................................................................................................... 104

9.1 OVERVIEW......................................................................................................................................... 104

9.2 CMP0M REGISTER ............................................................................................................................ 106

9.3 CMP1M REGISTER ............................................................................................................................ 107

9.4 ANALOG COMPARATOR APPLICATION...................................................................................... 108

10 IR OUTPUT............................................................................................................................................. 110

10.1 OVERVIEW....................................................................................................................................... 110

10.2 IR CONTROL REGISTER................................................................................................................. 111

10.2.1 IRM MODE REGISTER .............................................................................................................. 111

10.2.2 IRC COUNTING REGISTER ...................................................................................................... 111

10.2.3 IRR AUTO-LOAD REGISTER..................................................................................................... 112

10.2.4 IRD IR DUTY CONTROL REGISTER ........................................................................................ 113

10.2.5 IR OUTPUT OPERATION SEQUENCE..................................................................................... 114

11 SERIAL INPUT/OUTPUT TRANSCEIVER (SIO) ............................................................................ 115

11.1 OVERVIEW....................................................................................................................................... 115

11.2 SIO OPERATION............................................................................................................................... 115

11.3 SIOM MODE REGISTER.................................................................................................................. 117

11.4 SIOB DATA BUFFER ....................................................................................................................... 118

11.5 SIOR REGISTER DESCRIPTION..................................................................................................... 119

12 UNIVERSAL ASYNCHRONOUS RECEIVER/TRANSMITTER (UART)..................................... 120

12.1 OVERVIEW....................................................................................................................................... 120

12.2 UART OPERATION.......................................................................................................................... 120

12.3 UART RECEIVER CONTROL REGISTER...................................................................................... 123

12.4 UART TRANSMITTER CONTROL REGISTER............................................................................. 123

12.5 UART BAUD RATE CONTROL REGISTER................................................................................... 124

12.6 UART DATA BUFFER...................................................................................................................... 125

13 INSTRUCTION TABLE ........................................................................................................................ 126

14 ELECTRICAL CHARACTERISTIC................................................................................................... 127

SN8P26L38

8-Bit Micro-Controller

SONiX TECHNOLOGY CO., LTD Page 7 Version 1.5

14.1 ABSOLUTE MAXIMUM RATING.................................................................................................. 127

14.2 ELECTRICAL CHARACTERISTIC................................................................................................. 127

15 DEVELOPMENT TOOL ....................................................................................................................... 128

15.1 SN8P26L38 EV-KIT............................................................................................................................ 128

15.2 ICE AND EV-KIT APPLICATION NOTIC........................................................................................ 129

16 OTP PROGRAMMING PIN.................................................................................................................. 130

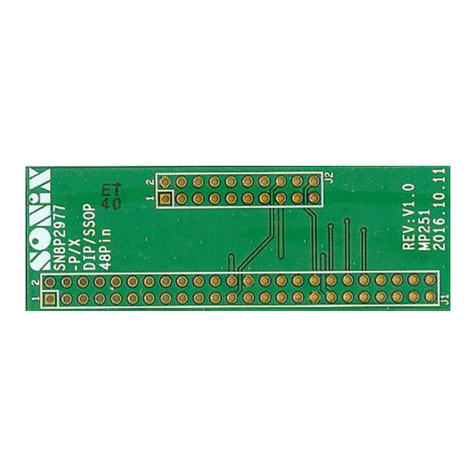

16.1 THE PIN ASSIGNMENT OF EASY WRITER TRANSITION BOARD SOCKET:................................................. 130

16.2 PROGRAMMING PIN MAPPING:............................................................................................................. 131

17 MARKING DEFINITION...................................................................................................................... 132

17.1 INTRODUCTION.............................................................................................................................. 132

17.2 MARKING INDETIFICATION SYSTEM........................................................................................ 132

17.3 MARKING EXAMPLE...................................................................................................................... 133

17.4 DATECODE SYSTEM ...................................................................................................................... 133

18 PACKAGE INFORMATION ................................................................................................................ 134

18.1 P-DIP 48 PIN ...................................................................................................................................... 134

18.2 LQFP 48 PIN....................................................................................................................................... 135

SN8P26L38

8-Bit Micro-Controller

SONiX TECHNOLOGY CO., LTD Page 8 Version 1.5

1 PRODUCT OVERVIEW

1.1 FEATURES

Memory configuration

Two 8-bit Timer/Counter

OTP ROM size: 8K * 16 bits.

T0: Basic timer.

RAM size: 880 * 8 bits.

TC1: Auto-reload timer/counter.

8 levels stack buffer

One RTC timer (T0).

One channels PWM output.

I/O pin configuration

One channels buzzer output.

Bi-directional: P0, P1, P2, P3, P4, P5

One channel IR output (duty/cycle programmable

Programmable open-drain: P1.0, P1.1, P5.0~P5.2,

PWM, TC0).

P3.2, P3.3.

On chip watchdog timer and clock source is internal

Wakeup:P0, P1 level change trigger.

low clock RC type (about 10KHz @3V).

P1 wake-up function controlled by P1W.

Pull-up resisters: P0, P1, P2, P3, P4, P5

One channel SIO interface.

External interrupt input: P0.0, P0.1

One channel UART interface.

External Interrupt trigger edge:

P0.0 controlled by PEDGE register

Four system clocks

External high clock: RC type up to 8 MHz

3-Level LVD.

External high clock: Crystal type up to 8 MHz

Reset system and power monitor.

Internal high clock: RC type 8MHz.

Internal low clock: RC type 10KHz(3V).

2-ch analog comparators with internal selectable

reference voltage 0.9V/1.0V/1.1V/1.2V and

Four operating modes

external reference input.

Normal mode: Both high and low clock active

Slow mode: Low clock only

8 interrupt sources

Sleep mode: Both high and low clock stop

6 internal interrupts: T0, TC1, CM0, CM1, SIO,

Green mode: Periodical wakeup by timer

UART

2 external interrupts: INT0 INT1

Package (Chip form support)

P-DIP 48 pins

Powerful instructions

LQFP 48 pins

One clock per instruction cycle (1T)

All ROM area JMP instruction.

All ROM area CALL address instruction.

All ROM area lookup table function (MOVC)

SN8P26L38

8-Bit Micro-Controller

SONiX TECHNOLOGY CO., LTD Page 9 Version 1.5

1.2 SYSTEM BLOCK DIAGRAM

INTERRUPT

CONTROL

EXTERNAL

HIGH OSC.

ACC

INTERNAL

LOW RC

TIMING GENERATOR

RAM

SYSTEM REGISTERS

LVD

(Low Voltage Detector)

WATCHDOG TIMER

TIMER & COUNTER

P0 P3P1

PWM 1

BUZZER 1

ALU

PC

FLAGS

IR OTP

ROM

PWM1

BZ1

P2

INTERNAL HIGH

RC 8MHz

Comparator 0

Comparator 1

CM0P

CM0N

CM0O

CM1P

CM1N

CM1O

IR OUT IROUT

UART

SIO

P4 P5

UTX, URX

SI, SO, SCK

SN8P26L38

8-Bit Micro-Controller

SONiX TECHNOLOGY CO., LTD Page 10 Version 1.5

1.3 PIN ASSIGNMENT

SN8P26L38P (P-DIP 48 pins)

VSS

1

U

48

VDD

P0.0/INT0

2

47

P5.7

P0.1/INT1

3

46

P5.6

P0.2/RST/VPP

4

45

P5.5

P0.3/XIN

5

44

P5.4/IROUT

P0.4/XOUT

6

43

P5.3/PWM1/BZ1

P0.5

7

42

P5.2/SO

P0.6

8

41

P5.1/SI

P0.7

9

40

P5.0/SCK

P1.0

10

39

P3.3/UTX

P1.1

11

38

P3.2/URX

P1.2

12

37

P3.1

P1.3

13

36

P3.0

P1.4

14

35

P4.7

P1.5

15

34

P4.6

P1.6

16

33

P4.5

P1.7

17

32

P4.4

P2.0

18

31

P4.3

P2.1

19

30

P4.2

P2.2/CM0N

20

29

P4.1

P2.3/CM0P

21

28

P4.0

P2.4/CM0O

22

27

VDD

P2.5/CM1N

23

26

VSS

P2.6/CM1P

24

25

P2.7/CM1O

SN8P26L38F (LQFP 48 pins)

P0.4/XOUT

P0.3/XIN

P0.2/RST/VPP

P0.1/INT1

P0.0/INT0

VSS

VDD

P5.7

P5.6

P5.5

P5.4/IROUT

P5.3/BZ1/PWM1

48

47

46

45

44

43

42

41

40

39

38

37

P0.5

1

O

36

P5.2/SO

P0.6

2

35

P5.1/SI

P0.7

3

34

P5.0/SCK

P1.0

4

33

P3.3/UTX

P1.1

5

32

P3.2/URX

P1.2

6

31

P3.1

P1.3

7

30

P3.0

P1.4

8

29

P4.7

P1.5

9

28

P4.6

P1.6

10

27

P4.5

P1.7

11

26

P4.4

P2.0

12

25

P4.3

13

14

15

16

17

18

19

20

21

22

23

24

P2.1

P2.2/CM0N

P2.3/CM0P

P2.4/CM0O

P2.5/CM1N

P2.6/CM1P

P2.7/CM1O

VSS

VDD

P4.0

P4.1

P4.2

SN8P26L38

8-Bit Micro-Controller

SONiX TECHNOLOGY CO., LTD Page 11 Version 1.5

1.4 PIN DESCRIPTIONS

PIN NAME

TYPE

DESCRIPTION

VDD, VSS

P

Power supply input pins for digital and analog circuit.

P0.2/RST/

VPP

I, P

RST: System external reset input pin. Schmitt trigger structure, active “low”, normal stay

to “high”. Build-in wake-up function.

VPP: OTP power input pin in programming mode.

P0.2: Input only pin with Schmitt trigger structure and no pull-up resistor.

XIN/P0.3

I/O

XIN: Oscillator input pin while external oscillator enable (crystal and RC).

P0.3: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters.

Build-in wake-up function.

XOUT/P0.4

I/O

XOUT: Oscillator output pin while external crystal enable.

P0.4: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters.

Build-in wake-up function.

P0.0/INT0

I/O

P0.0: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters.

Build-in wake-up function.

INT0: External interrupt 0 input pin.

P0.1/INT1

I/O

P0.1: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters.

Build-in wake-up function.

INT1: External interrupt 0 input pin.

TC1 event counter input pin.

P0[7:5]

I/O

P0[7:5]: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters.

Build-in wake-up function.

P1[1:0]

I/O

P1[1:0]: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters.

Build-in wake-up function. Open-drain structure controlled by P1OC register.

P1[7:0]

I/O

P1[7:2]: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters.

Build-in wake-up function.

P2[1:0]

I/O

P2[1:0]: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters.

P2.2/CM0N

I/O

P2.2: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters.

CM0N: The negative input pin of comparator.

P2.3/CM0P

I/O

P2.3: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters.

CM0P: The positive input pin of comparator.

BTO: Band-gap trimming mode output pin.

P2.4/CM0O

I/O

P2.4: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters.

CM0O: The output pin of comparator.

P2.5/CM1N

I/O

P2.5: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters.

CM1N: The negative input pin of comparator.

P2.6/CM1P

I/O

P2.6: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters.

CM1P: The positive input pin of comparator.

P2.7/CM1O

I/O

P2.7: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters.

CM1O: The output pin of comparator.

P3[1:0]

I/O

P3[1:0]: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters.

Open-drain structure controlled by P1OC register.

P3.2/URX

I/O

P3.2: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters.

Open-drain structure controlled by P1OC register.

URX: UART data receive pin.

P3.3/UTX

I/O

P3.3: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters.

Open-drain structure controlled by P1OC register.

UTX: UART data transmit pin.

P4[7:0]

I/O

P4[7:0]: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters.

P5.0/SCK

I/O

P5.0: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters.

Open-drain structure controlled by P1OC register.

SCK: SIO clock pin.

P5.1/SI

I/O

P5.1: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters.

Open-drain structure controlled by P1OC register.

SI: SIO data input pin.

P5.2/SO

I/O

P5.2: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters.

SN8P26L38

8-Bit Micro-Controller

SONiX TECHNOLOGY CO., LTD Page 12 Version 1.5

Open-drain structure controlled by P1OC register.

SO: SIO data output pin.

P5.3/BZ1/PWM1

I/O

P5.3: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters.

BZ1: Programmable buzzer output pin from TC1/2 signal.

PWM1: Programmable PWM output pin from TC1.

P5.4/IROUT

I/O

P5.4: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters.

IROUT: IR signal output pin.

P5[7:5]

I/O

P5[7:5]: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters.

1.5 PIN CIRCUIT DIAGRAMS

General purpose I/O pin:

Pull-Up

Resistor

Output

Latch

Pin

PnUR

PnM

Input Bus

Output Bus

General purpose I/O pin with open-drain structure:

Pull-Up

Resistor

Output

Latch

Pin

PnUR

PnM

Input Bus

Output Bus

P1OC

Open-Drain I/O Bus

Input only pin shared with reset pin:

Pin

OTP Program Mode

Input Bus

OTP Vpp Input

Reset Pin Code Option

Reset Trigger

SN8P26L38

8-Bit Micro-Controller

SONiX TECHNOLOGY CO., LTD Page 13 Version 1.5

General purpose I/O pin shared with Comparator:

Comparator Negative Pin:

Pull-Up

Resistor

Output

Latch

Pin

PnUR

PnM

Input Bus

Output Bus

CMnEN

Comparator

Negative Input

Comparator Positive Pin:

Pull-Up

Resistor

Output

Latch

Pin

PnUR

PnM

Input Bus

Output Bus

CMnEN

Comparator

Positive Input

CMnREF

Comparator Output Pin:

Pull-Up

Resistor

Output

Latch

Pin

PnUR

PnM

Input Bus

Output Bus

CMnEN

Comparator

Output

CMnOEN

General purpose I/O pin shared with external oscillator:

Pull-Up

Resistor

Output

Latch

Pin

PnUR

PnM

Input Bus

Output Bus

Oscillator

Code Option

Oscillator

SN8P26L38

8-Bit Micro-Controller

SONiX TECHNOLOGY CO., LTD Page 14 Version 1.5

2 CENTRAL PROCESSOR UNIT (CPU)

2.1 PROGRAM MEMORY (ROM)

8K words ROM

ROM

0000H

Reset vector

User reset vector

Jump to user start address

0001H

General purpose area

.

.

0007H

0008H

Interrupt vector

User interrupt vector

0009H

General purpose area

User program

.

.

000FH

0010H

0011H

.

.

.

.

.

1FFCH

End of user program

1FFDH

Reserved

1FFEH

1FFFH

The ROM includes Reset vector, Interrupt vector, General purpose area and Reserved area. The Reset vector is

program beginning address. The Interrupt vector is the head of interrupt service routine when any interrupt occurring.

The General purpose area is main program area including main loop, sub-routines and data table.

SN8P26L38

8-Bit Micro-Controller

SONiX TECHNOLOGY CO., LTD Page 15 Version 1.5

2.1.1 RESET VECTOR(0000H)

A one-word vector address area is used to execute system reset.

Power On Reset (NT0=1, NPD=0).

Watchdog Reset (NT0=0, NPD=0).

External Reset (NT0=1, NPD=1).

After power on reset, external reset or watchdog timer overflow reset, then the chip will restart the program from

address 0000h and all system registers will be set as default values. It is easy to know reset status from NT0, NPD

flags of PFLAG register. The following example shows the way to define the reset vector in the program memory.

Example: Defining Reset Vector

ORG

0

; 0000H

JMP

START

; Jump to user program address.

…

ORG

10H

START:

; 0010H, The head of user program.

…

; User program

…

ENDP

; End of program

SN8P26L38

8-Bit Micro-Controller

SONiX TECHNOLOGY CO., LTD Page 16 Version 1.5

2.1.2 INTERRUPT VECTOR(0008H)

A 1-word vector address area is used to execute interrupt request. If any interrupt service executes, the program

counter (PC) value is stored in stack buffer and jump to 0008h of program memory to execute the vectored interrupt.

Users have to define the interrupt vector. The following example shows the way to define the interrupt vector in the

program memory.

Note: ”PUSH”, “POP” instructions save and load ACC/PFLAG without (NT0, NPD). PUSH/POP buffer is a

unique buffer and only one level.

Example: Defining Interrupt Vector. The interrupt service routine is following ORG 8.

.CODE

ORG

0

; 0000H

JMP

START

; Jump to user program address.

…

ORG

8

; Interrupt vector.

PUSH

; Save ACC and PFLAG register to buffers.

…

…

POP

; Load ACC and PFLAG register from buffers.

RETI

; End of interrupt service routine

…

START:

; The head of user program.

…

; User program

…

JMP

START

; End of user program

…

ENDP

; End of program

SN8P26L38

8-Bit Micro-Controller

SONiX TECHNOLOGY CO., LTD Page 17 Version 1.5

Example: Defining Interrupt Vector. The interrupt service routine is following user program.

.CODE

ORG

0

; 0000H

JMP

START

; Jump to user program address.

…

ORG

8

; Interrupt vector.

JMP

MY_IRQ

; 0008H, Jump to interrupt service routine address.

ORG

10H

START:

; 0010H, The head of user program.

…

; User program.

…

…

JMP

START

; End of user program.

…

MY_IRQ:

;The head of interrupt service routine.

PUSH

; Save ACC and PFLAG register to buffers.

…

…

POP

; Load ACC and PFLAG register from buffers.

RETI

; End of interrupt service routine.

…

ENDP

; End of program.

Note: It is easy to understand the rules of SONIX program from demo programs given above. These

points are as following:

1. The address 0000H is a “JMP” instruction to make the program starts from the beginning.

2. The address 0008H is interrupt vector.

3. User’s program is a loop routine for main purpose application.

SN8P26L38

8-Bit Micro-Controller

SONiX TECHNOLOGY CO., LTD Page 18 Version 1.5

2.1.3 LOOK-UP TABLE DESCRIPTION

In the ROM’s data lookup function, Y register is pointed to middle byte address (bit 8~bit 15) and Z register is pointed

to low byte address (bit 0~bit 7) of ROM. After MOVC instruction executed, the low-byte data will be stored in ACC and

high-byte data stored in R register.

Example: To look up the ROM data located “TABLE1”.

B0MOV

Y, #TABLE1$M

; To set lookup table1’s middle address

B0MOV

Z, #TABLE1$L

; To set lookup table1’s low address.

MOVC

; To lookup data, R = 00H, ACC = 35H

; Increment the index address for next address.

INCMS

Z

; Z+1

JMP

@F

; Z is not overflow.

INCMS

Y

; Z overflow (FFH 00), Y=Y+1

NOP

;

;

@@:

MOVC

; To lookup data, R = 51H, ACC = 05H.

…

;

TABLE1:

DW

0035H

; To define a word (16 bits) data.

DW

5105H

DW

2012H

…

Note: The Y register will not increase automatically when Z register crosses boundary from 0xFF to

0x00. Therefore, user must take care such situation to avoid look-up table errors. If Z register is

overflow, Y register must be added one. The following INC_YZ macro shows a simple method to process

Y and Z registers automatically.

Example: INC_YZ macro.

INC_YZ

MACRO

INCMS

Z

; Z+1

JMP

@F

; Not overflow

INCMS

Y

; Y+1

NOP

; Not overflow

@@:

ENDM

SN8P26L38

8-Bit Micro-Controller

SONiX TECHNOLOGY CO., LTD Page 19 Version 1.5

Example: Modify above example by “INC_YZ” macro.

B0MOV

Y, #TABLE1$M

; To set lookup table1’s middle address

B0MOV

Z, #TABLE1$L

; To set lookup table1’s low address.

MOVC

; To lookup data, R = 00H, ACC = 35H

INC_YZ

; Increment the index address for next address.

;

@@:

MOVC

; To lookup data, R = 51H, ACC = 05H.

…

;

TABLE1:

DW

0035H

; To define a word (16 bits) data.

DW

5105H

DW

2012H

…

The other example of look-up table is to add Y or Z index register by accumulator. Please be careful if “carry” happen.

Example: Increase Y and Z register by B0ADD/ADD instruction.

B0MOV

Y, #TABLE1$M

; To set lookup table’s middle address.

B0MOV

Z, #TABLE1$L

; To set lookup table’s low address.

B0MOV

A, BUF

; Z = Z + BUF.

B0ADD

Z, A

B0BTS1

FC

; Check the carry flag.

JMP

GETDATA

; FC = 0

INCMS

Y

; FC = 1. Y+1.

NOP

GETDATA:

;

MOVC

; To lookup data. If BUF = 0, data is 0x0035

; If BUF = 1, data is 0x5105

; If BUF = 2, data is 0x2012

…

TABLE1:

DW

0035H

; To define a word (16 bits) data.

DW

5105H

DW

2012H

…

SN8P26L38

8-Bit Micro-Controller

SONiX TECHNOLOGY CO., LTD Page 20 Version 1.5

2.1.4 JUMP TABLE DESCRIPTION

The jump table operation is one of multi-address jumping function. Add low-byte program counter (PCL) and ACC

value to get one new PCL. If PCL is overflow after PCL+ACC, PCH adds one automatically. The new program counter

(PC) points to a series jump instructions as a listing table. It is easy to make a multi-jump program depends on the

value of the accumulator (A).

Note: PCH only support PC up counting result and doesn’t support PC down counting. When PCL is

carry after PCL+ACC, PCH adds one automatically. If PCL borrow after PCL–ACC, PCH keeps value and

not change.

Example: Jump table.

ORG

0X0100

; The jump table is from the head of the ROM boundary

B0ADD

PCL, A

; PCL = PCL + ACC, PCH + 1 when PCL overflow occurs.

JMP

A0POINT

; ACC = 0, jump to A0POINT

JMP

A1POINT

; ACC = 1, jump to A1POINT

JMP

A2POINT

; ACC = 2, jump to A2POINT

JMP

A3POINT

; ACC = 3, jump to A3POINT

SONIX provides a macro for safe jump table function. This macro will check the ROM boundary and move the jump

table to the right position automatically. The side effect of this macro maybe wastes some ROM size.

Example: If “jump table” crosses over ROM boundary will cause errors.

@JMP_A

MACRO

VAL

IF

(($+1) !& 0XFF00) !!= (($+(VAL)) !& 0XFF00)

JMP

($ | 0XFF)

ORG

($ | 0XFF)

ENDIF

ADD

PCL, A

ENDM

Note: “VAL” is the number of the jump table listing number.

Table of contents

Other SONIX Microcontroller manuals

SONIX

SONIX SN8P1829 User manual

SONIX

SONIX SN8P2604 User manual

SONIX

SONIX SN8PC20 User manual

SONIX

SONIX SN8P2501D User manual

SONIX

SONIX SN8P1700 Series User manual

SONIX

SONIX SN8P2743 Series User manual

SONIX

SONIX SN32F280 Series User manual

SONIX

SONIX SN8ICE 2K User manual

SONIX

SONIX SN8P2714_2715 User manual

SONIX

SONIX SN8P26L00 Series User manual

Popular Microcontroller manuals by other brands

Samsung

Samsung KS86C6004 manual

Epson

Epson S1C17624 Technical manual

Uctronics

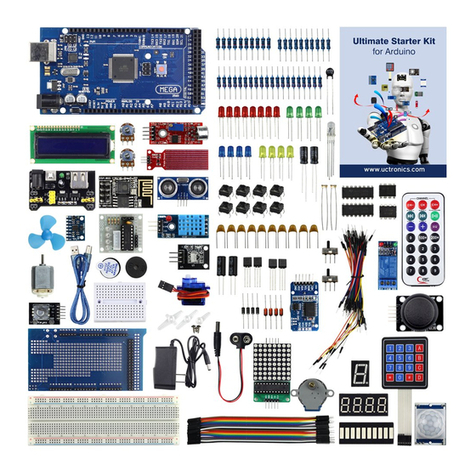

Uctronics Ultimate Starter Kit for Arduino manual

Texas Instruments

Texas Instruments TMS370 Series Technical reference

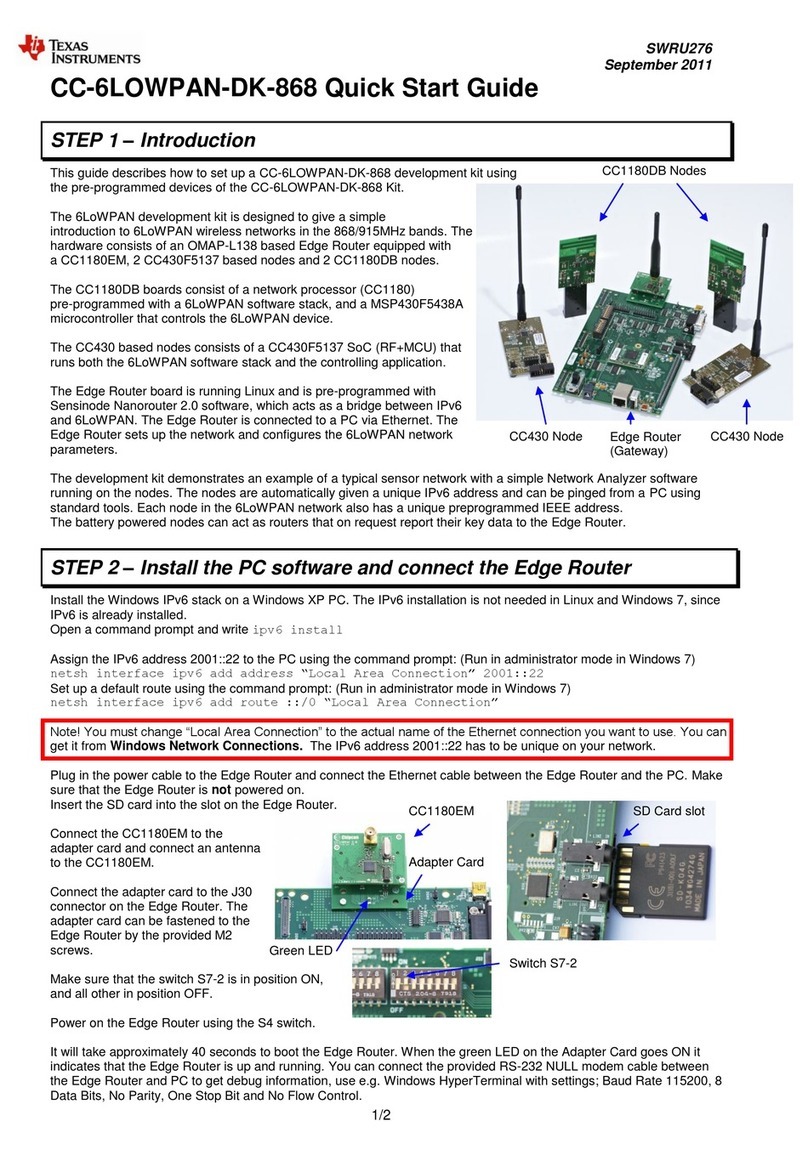

Texas Instruments

Texas Instruments CC-6LOWPAN-DK-868 quick start guide

Renesas

Renesas RX600 Series user manual